Stateflow® временные логические операторы (такие как after, before, или every) булевы операторы, которые работают с количествами повторения событий Stateflow. Временные логические операторы могут появиться только в условиях на переходах, которые происходят из состояний, и в состояниях активности. Несмотря на то, что временная логика не вводит новые события в модель Stateflow, полезно думать об изменении значения временного логического условия как событие. Можно использовать временные логические операторы во многих случаях, где счетчик требуется. Случай общего использования должен был бы использовать временную логику, чтобы реализовать счетчик тайм-аута.

Для получения дальнейшей информации смотрите Управление выполнением диаграммы при помощи Временной Логики (Stateflow).

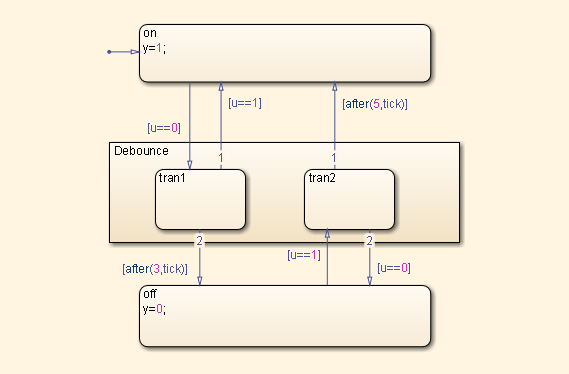

График, показанный в следующем рисунке, использует временную логику в проекте для debouncer. Вместо того, чтобы мгновенно переключиться между на и от состояний, график использует два промежуточных состояния и временную логику, чтобы проигнорировать переходные процессы. Переход фиксируется на основе тайм-аута.

По умолчанию состояния в Chart Stateflow упорядочены в алфавитном порядке. Упорядоченное расположение состояний в HDL-коде может потенциально варьироваться, если вы включаете активную генерацию выходного порта состояния в HDL-коде. Чтобы включить эту установку, откройте свойства Chart и установите флажок Create output port for monitoring. См. также Упрощают диаграммы Stateflow путем Слияния Активного Выхода состояния (Stateflow).

Когда вы генерируете VHDL® код, недавно добавленное состояние выбрано как OTHERS состояние в HDL-коде. Следующая выборка кода показывает код VHDL, сгенерированный от этого Chart.

Chart_1_output : PROCESS (is_Chart, u, temporalCounter_i1, y_reg)

VARIABLE temporalCounter_i1_temp : unsigned(7 DOWNTO 0);

BEGIN

temporalCounter_i1_temp := temporalCounter_i1;

is_Chart_next <= is_Chart;

y_reg_next <= y_reg;

IF temporalCounter_i1 < 7 THEN

temporalCounter_i1_temp := temporalCounter_i1 + 1;

END IF;

CASE is_Chart IS

WHEN IN_tran1 =>

IF u = 1.0 THEN

is_Chart_next <= IN_on;

y_reg_next <= 1.0;

ELSIF temporalCounter_i1_temp >= 3 THEN

is_Chart_next <= IN_off;

y_reg_next <= 0.0;

END IF;

WHEN IN_tran2 =>

IF temporalCounter_i1_temp >= 5 THEN

is_Chart_next <= IN_on;

y_reg_next <= 1.0;

ELSIF u = 0.0 THEN

is_Chart_next <= IN_off;

y_reg_next <= 0.0;

END IF;

WHEN IN_off =>

IF u = 1.0 THEN

is_Chart_next <= IN_tran2;

temporalCounter_i1_temp := to_unsigned(0, 8);

END IF;

WHEN OTHERS =>

IF u = 0.0 THEN

is_Chart_next <= IN_tran1;

temporalCounter_i1_temp := to_unsigned(0, 8);

END IF;

END CASE;

temporalCounter_i1_next <= temporalCounter_i1_temp;

END PROCESS Chart_1_output;Графическая функция является функцией, определяемой графически блок-схемой. Графические функции находятся в графике наряду со схемами, которые вызывают их. Как MATLAB® функции и функции C, графические функции могут принять аргументы и возвратить результаты. Графические функции могут быть вызваны в переходе и состояниях активности.

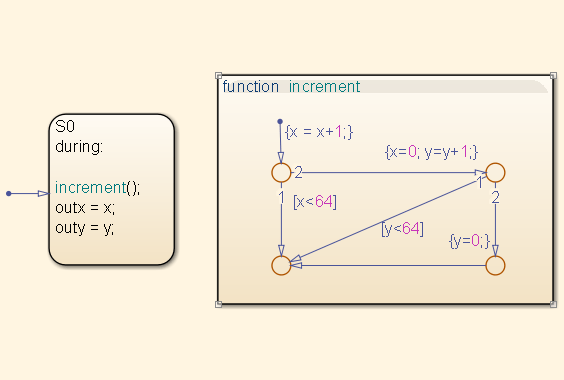

Следующий рисунок показывает графическую функцию, которая реализует 64 64 счетчик.

Следующая выборка кода показывает код VHDL, сгенерированный для этой графической функции.

x64_counter_sf : PROCESS (x, y, outx_reg, outy_reg)

-- local variables

VARIABLE x_temp : unsigned(7 DOWNTO 0);

VARIABLE y_temp : unsigned(7 DOWNTO 0);

BEGIN

outx_reg_next <= outx_reg;

outy_reg_next <= outy_reg;

x_temp := x;

y_temp := y;

x_temp := tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(x_temp, 9), 10)

+ tmw_to_unsigned(to_unsigned(1, 9), 10), 8);

IF x_temp < to_unsigned(64, 8) THEN

NULL;

ELSE

x_temp := to_unsigned(0, 8);

y_temp := tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(y_temp, 9), 10)

+ tmw_to_unsigned(to_unsigned(1, 9), 10), 8);

IF y_temp < to_unsigned(64, 8) THEN

NULL;

ELSE

y_temp := to_unsigned(0, 8);

END IF;

END IF;

outx_reg_next <= x_temp;

outy_reg_next <= y_temp;

x_next <= x_temp;

y_next <= y_temp;

END PROCESS x64_counter_sf;Диаграммы Stateflow поддерживают обе иерархии (состояния, содержащие другие состояния) и параллелизм (несколько состояний, которые могут быть активными одновременно).

В семантике Stateflow параллелизм не синонимичен с параллелизмом. Параллельные состояния могут быть активными одновременно, но они выполняются последовательно согласно их порядку выполнения. (Порядок выполнения отображен на правом верхнем углу параллельного состояния).

Для получения дальнейшей информации на иерархии и параллелизме, смотрите Иерархию Объектов Stateflow (Stateflow) и Порядок выполнения для Параллельных состояний (Stateflow).

Для генерации HDL-кода целый график сопоставляет с одним выходным процессом вычисления. В рамках выходного процесса вычисления:

Выполнение параллельных состояний продолжает последовательно.

Вложенные иерархические состояния сопоставляют с вложенным CASE операторы в сгенерированном HDL-коде.

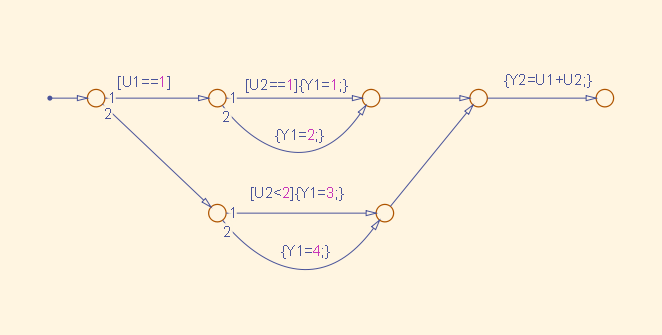

Графики, состоящие из чистых блок-схем (т.е. графики без состояний), полезны в получении if-then-else построения, используемые на процедурных языках как C.

Как пример, рассмотрите следующую логику, описанную в подобном C псевдокоде.

if(U1==1) {

if(U2==1) {

Y = 1;

}else{

Y = 2;

}

}else{

if(U2<2) {

Y = 3;

}else{

Y = 4;

}

}

Следующий рисунок показывает блок-схему, которая реализует if-then-else логика.

Следующая сгенерированная выборка VHDL кода показывает вложенные операторы IF-ELSE, полученные из блок-схемы.

Chart : PROCESS (Y1_reg, Y2_reg, U1, U2)

-- local variables

BEGIN

Y1_reg_next <= Y1_reg;

Y2_reg_next <= Y2_reg;

IF unsigned(U1) = to_unsigned(1, 8) THEN

IF unsigned(U2) = to_unsigned(1, 8) THEN

Y1_reg_next <= to_unsigned(1, 8);

ELSE

Y1_reg_next <= to_unsigned(2, 8);

END IF;

ELSIF unsigned(U2) < to_unsigned(2, 8) THEN

Y1_reg_next <= to_unsigned(3, 8);

ELSE

Y1_reg_next <= to_unsigned(4, 8);

END IF;

Y2_reg_next <= tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(unsigned(U1), 9),10)

+ tmw_to_unsigned(tmw_to_unsigned(unsigned(U2), 9), 10), 8);

END PROCESS Chart;HDL Coder™ поддерживает генерацию HDL-кода для:

Таблица истинности функционирует в диаграмме Stateflow

Truth Table (Stateflow) блокируется в Simulink® модели

Этот раздел исследует функцию Таблицы истинности в графике и коде VHDL, сгенерированном для графика.

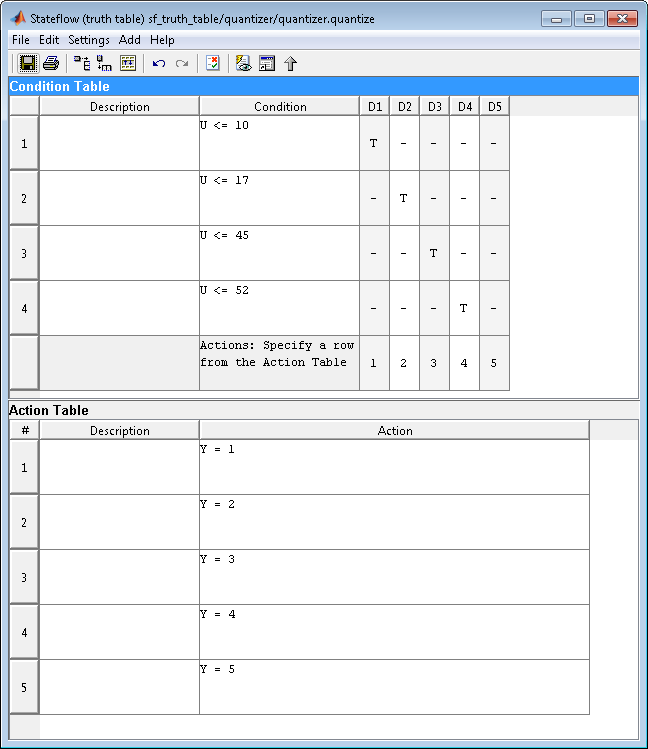

Таблицы истинности являются подходящими для реализации компактной комбинаторной логики. Типовое приложение для Таблиц истинности должно реализовать нелинейное квантование или пороговую логику. Рассмотрите следующую логику:

Y = 1 when 0 <= U <= 10 Y = 2 when 10 < U <= 17 Y = 3 when 17 < U <= 45 Y = 4 when 45 < U <= 52 Y = 5 when 52 < U

График не сохраняющий состояние с одним вызовом функции Truth Table может представлять эту логику кратко.

Следующий рисунок показывает quantizer стройте диаграмму, содержа Truth Table.

Следующий рисунок показывает пороговую логику, как отображено в Редакторе Таблицы истинности.

Следующая выборка кода показывает код VHDL, сгенерированный для quantizer график.

quantizer : PROCESS (Y_reg, U)

-- local variables

VARIABLE aVarTruthTableCondition_1 : std_logic;

VARIABLE aVarTruthTableCondition_2 : std_logic;

VARIABLE aVarTruthTableCondition_3 : std_logic;

VARIABLE aVarTruthTableCondition_4 : std_logic;

BEGIN

Y_reg_next <= Y_reg;

-- Condition #1

aVarTruthTableCondition_1 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(10, 8));

-- Condition #2

aVarTruthTableCondition_2 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(17, 8));

-- Condition #3

aVarTruthTableCondition_3 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(45, 8));

-- Condition #4

aVarTruthTableCondition_4 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(52, 8));

IF tmw_to_boolean(aVarTruthTableCondition_1) THEN

-- D1

-- Action 1

Y_reg_next <= to_unsigned(1, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_2) THEN

-- D2

-- Action 2

Y_reg_next <= to_unsigned(2, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_3) THEN

-- D3

-- Action 3

Y_reg_next <= to_unsigned(3, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_4) THEN

-- D4

-- Action 4

Y_reg_next <= to_unsigned(4, 8);

ELSE

-- Default

-- Action 5

Y_reg_next <= to_unsigned(5, 8);

END IF;

END PROCESS quantizer;Примечание

При генерации кода для блока Truth Table (Stateflow) в модели Simulink HDL Coder записывает отдельный файл сущности/архитектуры для кода Truth Table. Файл называют Truth_Table.vhd (для VHDL) или Truth_Table.v (для Verilog®).

State Transition Table (Stateflow) | Truth Table (Stateflow) | Sequence Viewer (Stateflow)