В HDL Workflow Advisor можно выбрать Processor/FPGA synchronization mode для процессора и FPGA, когда вы генерируете пользовательское ядро IP, чтобы использовать в проекте интегрирования встраиваемой системы. Следующие режимы синхронизации доступны:

Free running (значение по умолчанию)

Coprocessing – blocking

Coprocessing – nonblocking with delay

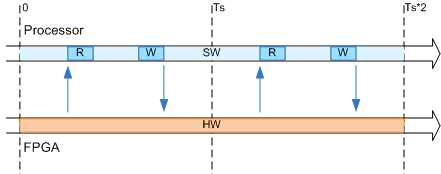

В режиме свободного доступа, процессоре и FPGA каждый несинхронизируемый запуск, постоянно, и параллельно.

Выберите Free running как Processor/FPGA synchronization mode, когда вы не захотите, чтобы ваш процессор и FPGA автоматически синхронизировались.

Следующая схема показывает, как процессор и FPGA могут связаться в режиме свободного доступа. Заштрихованные области указывают, что процессор и FPGA запускаются постоянно.

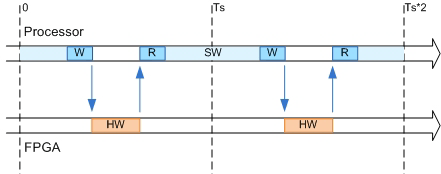

В блокирующемся режиме сопроцессора HDL Coder™ автоматически генерирует логику синхронизации для FPGA так, чтобы процессор и FPGA, запущенный в тандеме.

Выберите Coprocessing – blocking как Processor/FPGA synchronization mode, когда время выполнения FPGA коротко относительно шага расчета процессора, и вы хотите, чтобы FPGA завершился, прежде чем процессор продолжится.

Следующая схема показывает как процессор и FPGA, запущенный в блокировании режима совместной обработки.

Заштрихованные области указывают, когда процессор и FPGA запускаются. Во время каждого шага расчета процессор пишет в FPGA, затем останавливается и ожидает индикации, которую FPGA закончил обрабатывать прежде, чем продолжить запускаться. Каждый раз запуски FPGA, это выполняет логику, сгенерированную для одного шага расчета подсистемы DUT.