Симулируйте сгенерированный проект под тестом (DUT) HDL с тестовыми векторами от испытательного стенда с помощью заданного инструмента симуляции.

Запустите MATLAB к HDL Workflow Advisor.

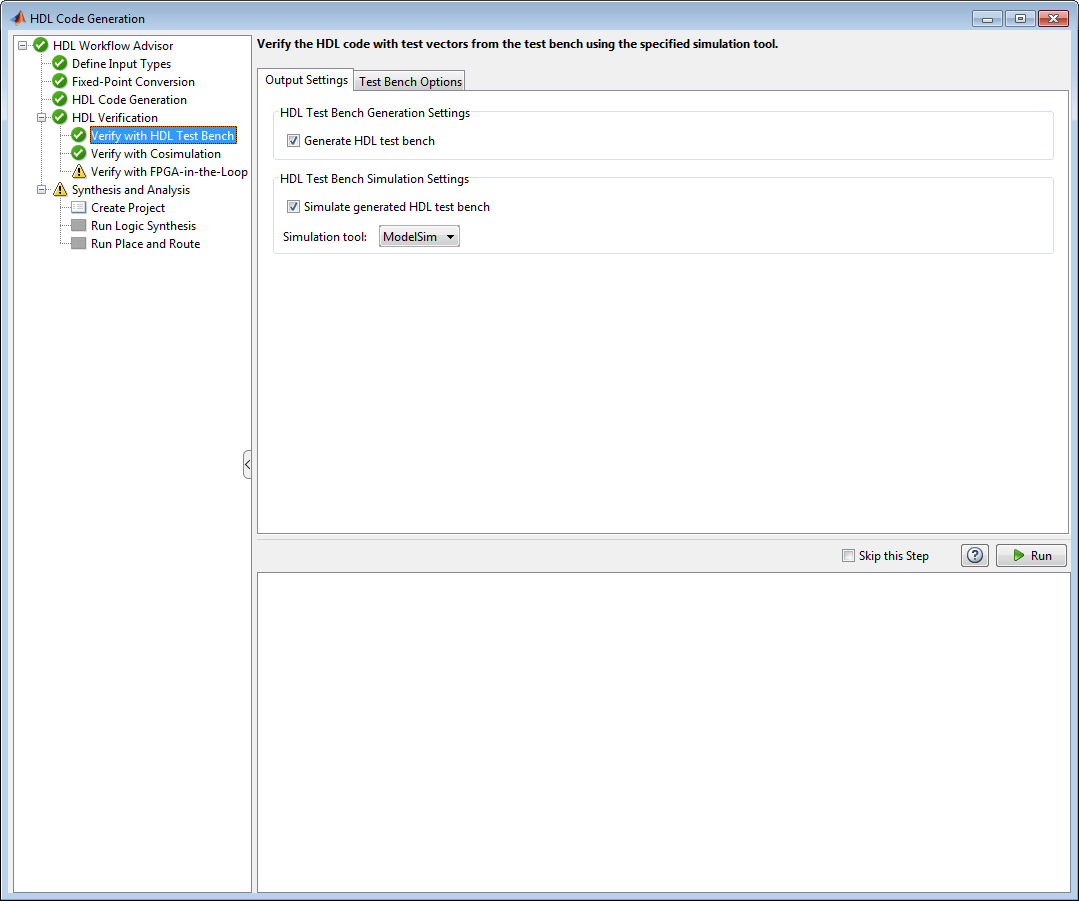

На шаге HDL Verification нажмите Verify with HDL Test Bench.

Выберите Generate HDL test bench.

Эта опция позволяет HDL Coder™ сгенерировать код испытательного стенда HDL из вашего MATLAB® тестовый скрипт.

Опционально, выберите Simulate generated HDL test bench. Эта опция позволяет MATLAB симулировать испытательный стенд HDL с HDL DUT.

Если вы выбираете эту опцию, необходимо также выбрать Simulation tool.

Для Test Bench Options выберите и установите дополнительные параметры согласно описаниям в следующей таблице.

| Параметр испытательного стенда HDL | Описание |

|---|---|

| Test bench name postfix | Задайте постфикс для имени испытательного стенда. |

| Force clock | Включите для испытательного стенда, чтобы обеспечить входные сигналы часов. |

| Clock high time (ns) | Задайте номер наносекунд, часы высоки. |

| Clock low time (ns) | Задайте номер наносекунд, часы являются низкими. |

| Hold time (ns) | Задайте время задержки для входных сигналов и обеспеченных сигналов сброса. |

| Force clock enable | Включите, чтобы обеспечить часы, включают. |

| Clock enable delay (in clock cycles) | Укажите, что время (за такты) между deassertion сброса и утверждением часов включает. |

| Force reset | Включите для испытательного стенда, чтобы обеспечить входные сигналы сброса. |

| Reset length (in clock cycles) | Задайте время (за такты) между утверждением и deassertion сброса. |

| Hold input data between samples | Включите, чтобы содержать сигналы подуровня между выборками часов. |

| Input data interval | Указывает, что количество тактов между утверждениями часов включает. Для получения дополнительной информации смотрите, Указывают, что Часы Испытательного стенда Включают Уровень Переключателя. |

| Initialize test bench inputs | Включите, чтобы инициализировать значения на входных параметрах к испытательному стенду, прежде чем испытательный стенд будет управлять данными к DUT. |

| Multi file test bench | Включите, чтобы разделить сгенерированный испытательный стенд на функции помощника, данные и код испытательного стенда HDL. |

| Test bench data file name postfix | Задайте вектор символов, чтобы добавить к имени файла данных испытательного стенда при генерации многофайлового испытательного стенда. |

| Test bench reference postfix | Задайте вектор символов, чтобы добавить к именам опорных сигналов в коде испытательного стенда. |

| Ignore data checking (number of samples) | Задайте количество отсчетов в начале моделирования, во время которого подавлена проверка выходных данных. |

| Simulation iteration limit | Задайте максимальное количество тестовых выборок, чтобы использовать в процессе моделирования сгенерированного HDL-кода. |

Опционально, выберите Skip this step, если вы не хотите использовать испытательный стенд HDL, чтобы проверить HDL DUT.

Нажмите Run.

Если испытательный стенд и симуляция успешны, необходимо видеть сообщения, похожие на них в панели сообщения:

### Begin TestBench generation. ### Collecting data... ### Begin HDL test bench file generation with logged samples ### Generating test bench: mlhdlc_sfir_fixpt_tb.vhd ### Creating stimulus vectors... ### Simulating the design 'mlhdlc_sfir_fixpt' using 'ModelSim'. ### Generating Compilation Report mlhdlc_sfir_fixpt_vsim_log_compile.txt ### Generating Simulation Report mlhdlc_sfir_fixpt_vsim_log_sim.txt ### Simulation successful. ### Elapsed Time: 113.0315 sec(s)

Если существуют ошибки, те сообщения появляются в панели сообщения. Зафиксируйте ошибки и нажмите Run.