Для FPGA в цикле можно использовать собственную квалифицированную плату FPGA, даже если это не находится в предзарегистрированном списке плат FPGA, предоставленном MathWorks®. Используя Новый мастер Совета FPGA, можно создать файл определения платы, который описывает пользовательскую плату FPGA.

В этом примере можно следовать за рабочим процессом создания файла определения платы для Xilinx® Оценочная плата KC705, чтобы использовать с симуляцией FIL.

Проверяйте спецификацию платы так, чтобы у вас была следующая готовая информация:

Интерфейс FPGA к Ethernet чип PHY

Имена и номера тактовых выводов

Сбросьте имена и номера контактов

В этом примере запрошенная информация предоставляется вам. В общем случае можно найти этот тип информации в файле спецификации платы. Этот пример использует Оценочную плату KC705 для Руководства пользователя FPGA Kintex-7, опубликованного Xilinx.

Для валидации у вас должны быть Xilinx или Altera® на вашем пути. Используйте hdlsetuptoolpath (HDL Coder) функция, чтобы сконфигурировать инструмент для использования с MATLAB®.

Чтобы проверить программирование платы FPGA после того, как вы добавите ее файл определения, присоедините пользовательскую плату к своему компьютеру. Однако соединение платы не необходимо для создания файла определения платы.

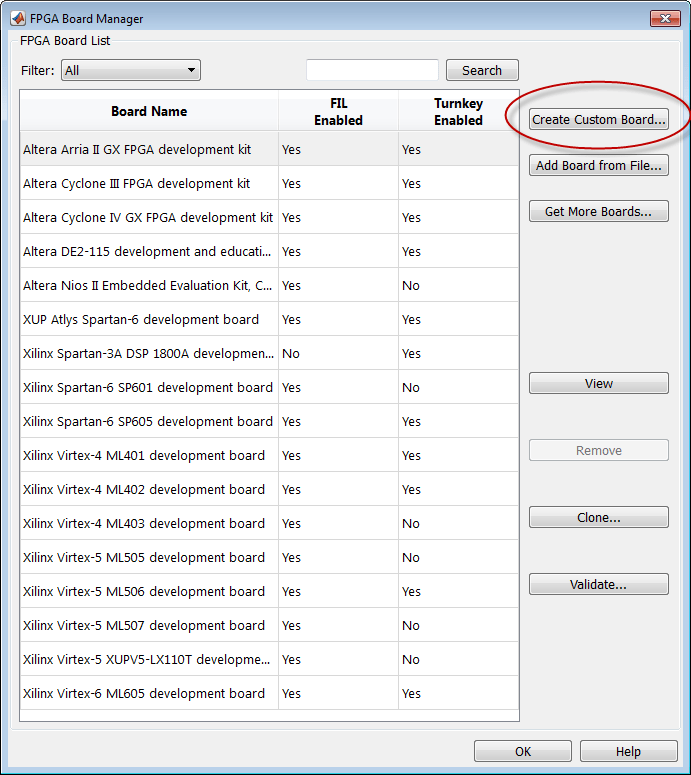

Запустите менеджера Совета FPGA путем ввода следующей команды в подсказке MATLAB:

>>fpgaBoardManager

Нажмите Create Custom Board, чтобы открыть Новый мастер Совета FPGA.

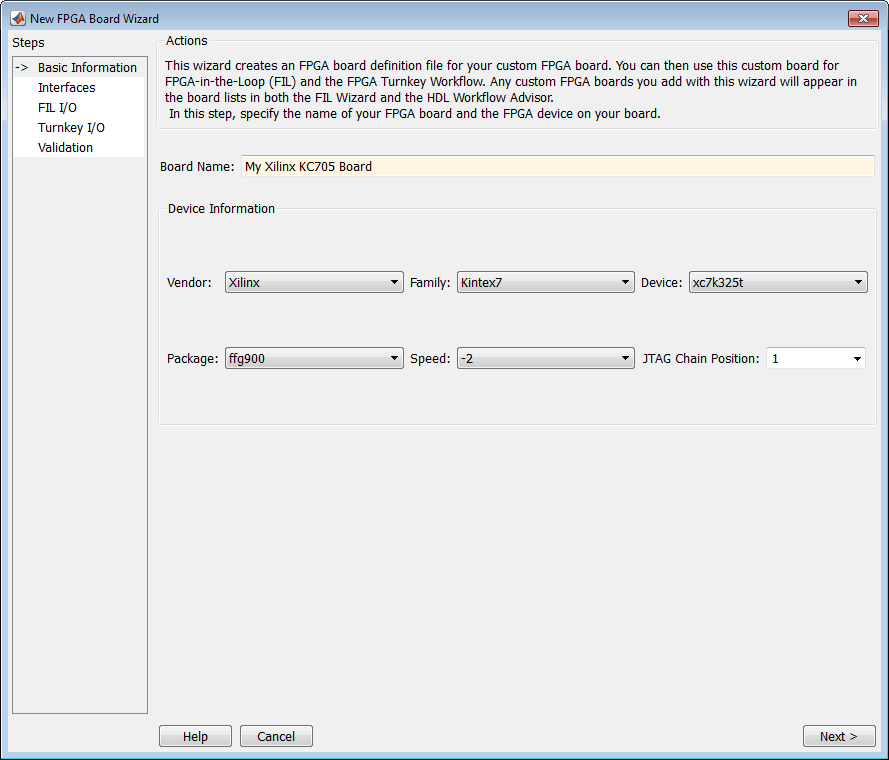

В панели Основной информации введите следующую информацию:

Board Name: вводит "мой Совет Xilinx KC705"

Vendor: выбирает Xilinx

Family: выбирает Kintex7

Device: выбирает xc7k325t

Package: выбирает ffg900

Speed: выбирает -2

JTAG Chain Position: выбирает 1

Информация, которую вы только ввели, может быть найдена в Оценочной плате KC705 для Руководства пользователя FPGA Kintex-7.

Нажмите Next.

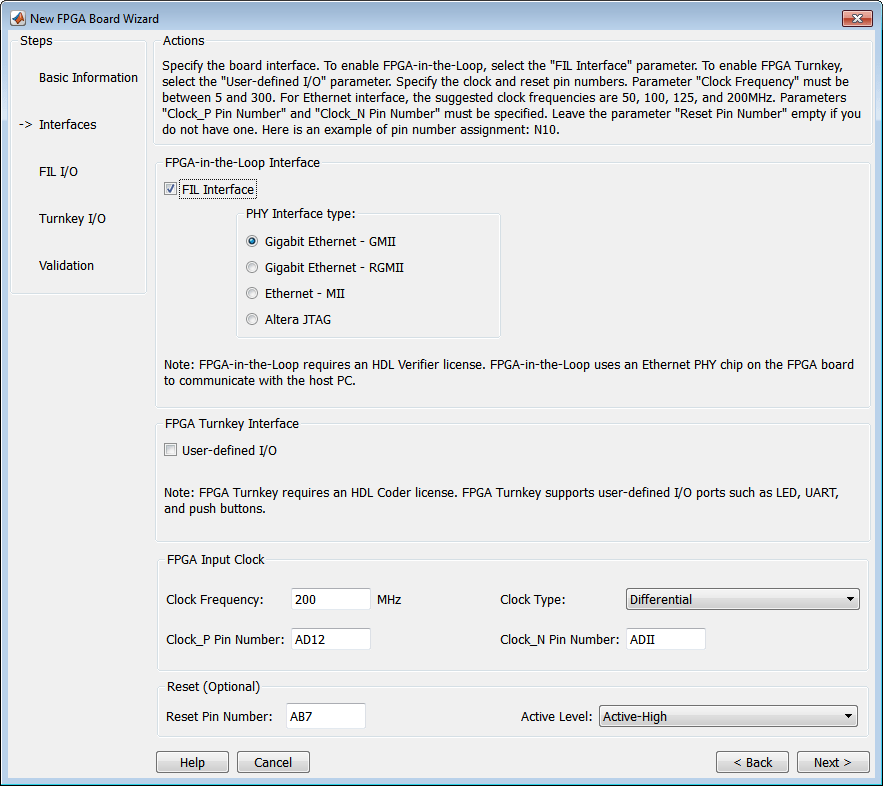

В панели Интерфейсов выполните следующие задачи.

Выберите FIL Interface. Эта опция требуется для использования вашей платы с FPGA в цикле.

Выберите GMII в Типе Интерфейса PHY. Эта опция указывает, что встроенный FPGA соединяется с Ethernet чип PHY через интерфейс GMII.

Оставьте опцию User-defined I/O в разделе FPGA Turnkey Interface очищенной. Рабочий процесс Тюремщика FPGA не является особым вниманием этого примера.

Clock Frequency: Входит 200. Эта плата Xilinx KC705 имеет несколько источников часов. Часы на 200 МГц являются одной из рекомендуемых тактовых частот для использования с интерфейсом Ethernet (50, 100, 125, и 200 МГц).

Clock Type: выбирает Differential.

Clock_P Pin Number: вводит AD12.

Clock_N Pin Number: вводит AD11.

Clock IO Standard — Оставьте незаполненный.

Reset Pin Number: Вводит AB7. Это значение предоставляет глобальный сброс к FPGA.

Active Level: выбирает Active-High.

Reset IO Standard — Оставьте незаполненный.

Можно получить всю необходимую информацию из спецификации проекта платы.

Нажмите Next.

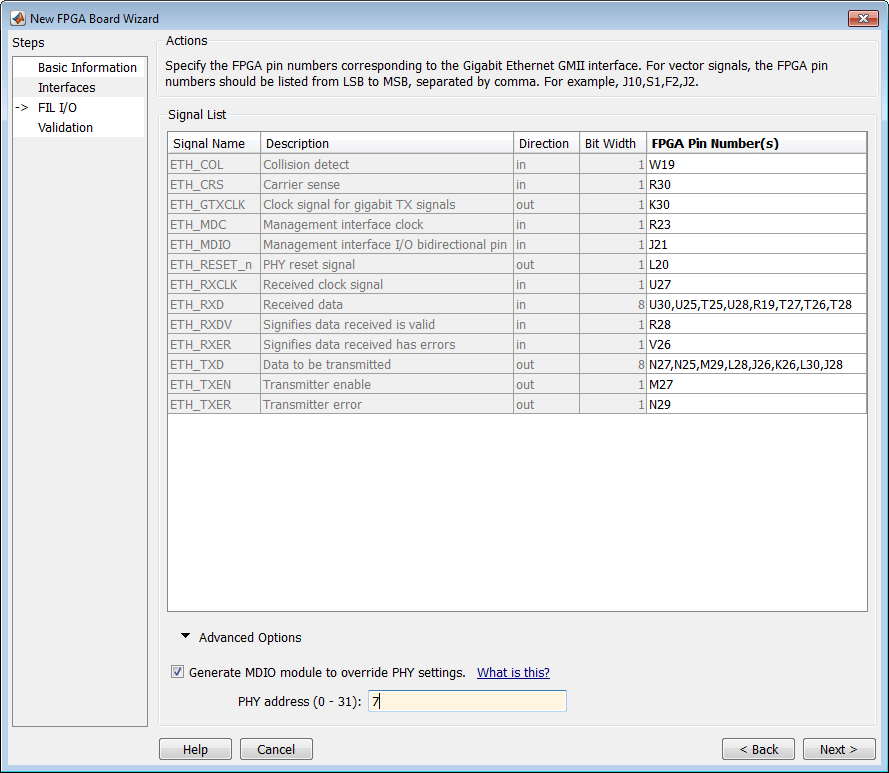

В панели FILI/O введите номера для каждого контакта FPGA. Эта информация запрашивается.

ПИН-коды для RXD и сигналов TXD вводятся от младшей значащей цифры (LSD) до старшей значащей цифры (MSB), разделенный запятой.

| Для имени сигнала... | Введите ПИН-код FPGA... |

|---|---|

| ETH_COL | W19 |

| ETH_CRS | R30 |

| ETH_GTXCLK | K30 |

| ETH_MDC | R23 |

| ETH_MDIO | J21 |

| ETH_RESET_n | L20 |

| ETH_RXCLK | U27 |

| ETH_RXD | U30, U25, T25, U28, R19, T27, T26, T28 |

| ETH_RXDV | R28 |

| ETH_RXER | V26 |

| ETH_TXD | N27, N25, M29, L28, J26, K26, L30, J28 |

| ETH_TXEN | M27 |

| ETH_TXER | N29 |

Нажмите Advanced Options, чтобы расширить раздел.

Проверяйте опцию Generate MDIO module to override PHY settings.

Эта опция выбрана по следующим причинам:

Существуют перемычки на плате Xilinx KC705, которые конфигурируют Ethernet устройство PHY к MII, GMII, RGMII или режиму SGMII. Поскольку этот пример использует интерфейсы GMII, плата FPGA не работает, если устройства PHY установлены в неправильный режим. Когда опция Generate MDIO module to override PHY settings выбрана, FPGA использует Ввод данных управления / Выход (MDIO) шина, чтобы заменить настройки перемычки и сконфигурировать чип PHY к правильному режиму GMII.

Эта опция в настоящее время только применяется к Marvell Аляска, устройство PHY 88E1111 и эта плата KC705 использует устройство Чуда.

PHY address (0 – 31): входит 7.

Нажмите Next.

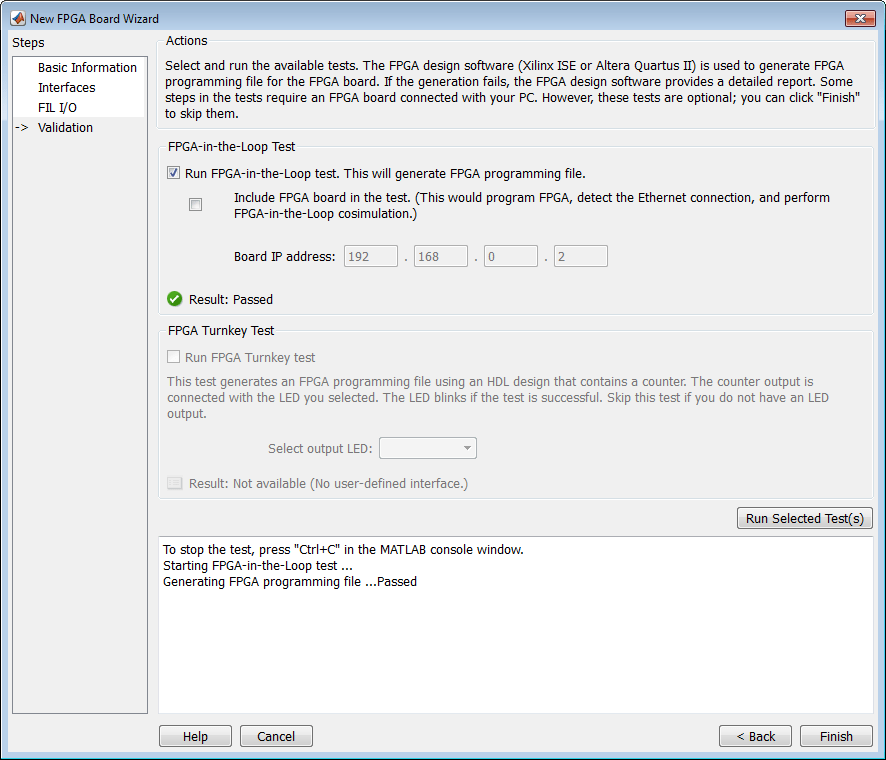

Этот шаг предоставляет тест валидации вам, чтобы проверить, правильна ли вводимая информация путем выполнения FPGA в цикле cosimulation. Вам нужны Xilinx ISE 13.4 или старшие версии, установленные на том же компьютере. Этот шаг является дополнительным, и можно пропустить его, если вы предпочитаете.

Примечание

Для валидации у вас должны быть Xilinx или Altera на вашем пути. Используйте hdlsetuptoolpath (HDL Coder) функция, чтобы сконфигурировать инструмент для использования с MATLAB.

Чтобы запустить этот тест, выполните следующие действия.

Проверяйте опцию Run FPGA-in-the-Loop test.

Если вам присоединили плату, проверяйте опцию Include FPGA board in the test. Необходимо предоставить IP-адрес Совета FPGA. Этот пример принимает, что плата Xilinx KC705 присоединена к вашему хосту - компьютеру, и это имеет IP-адрес 192.168.0.2.

Нажмите Run Selected Test(s). Тесты занимают приблизительно 10 минут, чтобы завершиться.

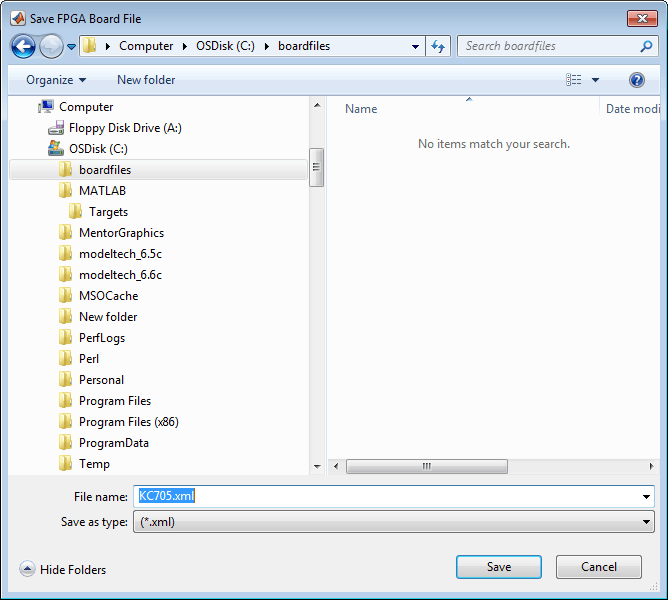

Нажмите Finish, чтобы выйти из Нового мастера Совета FPGA. Диалоговое окно Save As появляется и просит местоположение файла определения платы FPGA. В данном примере сохраните как C:\boardfiles\KC705.xml.

Нажмите Save, чтобы сохранить файл и выход.

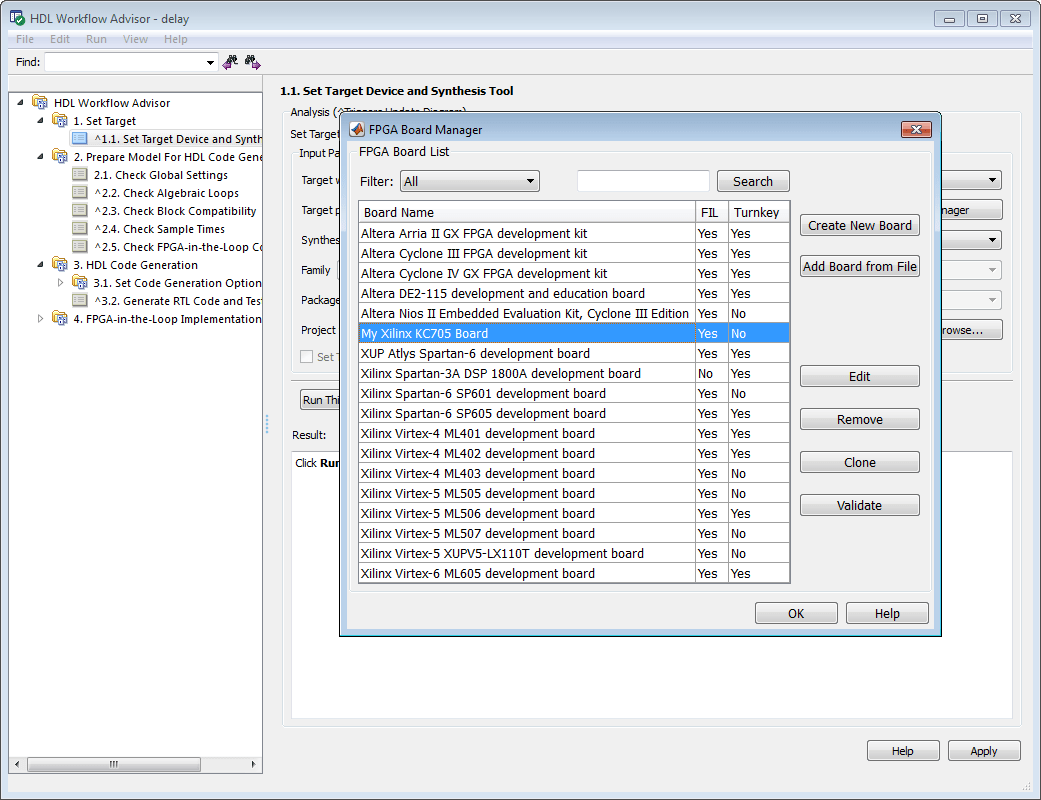

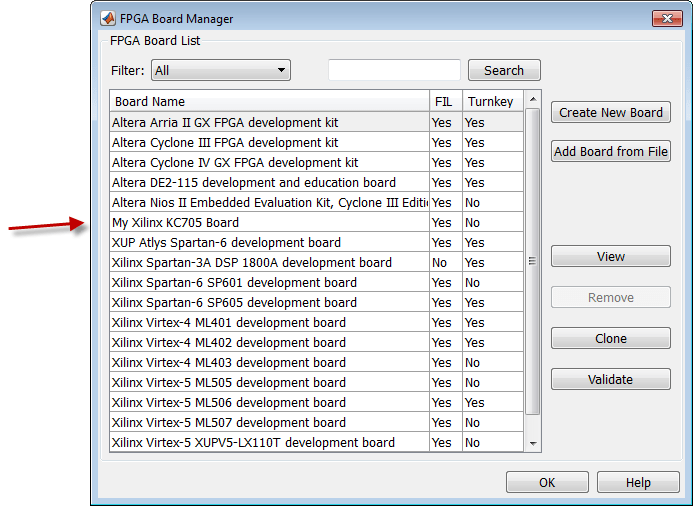

После того, как вы сохраните файл определения платы, вы возвращены в менеджера Совета FPGA. В Списке плат FPGA можно теперь видеть новую плату, которую вы задали.

Нажмите OK, чтобы закрыть менеджера Совета FPGA.

Можно просмотреть новый форум в списке плат или от мастера FIL или от HDL Workflow Advisor.

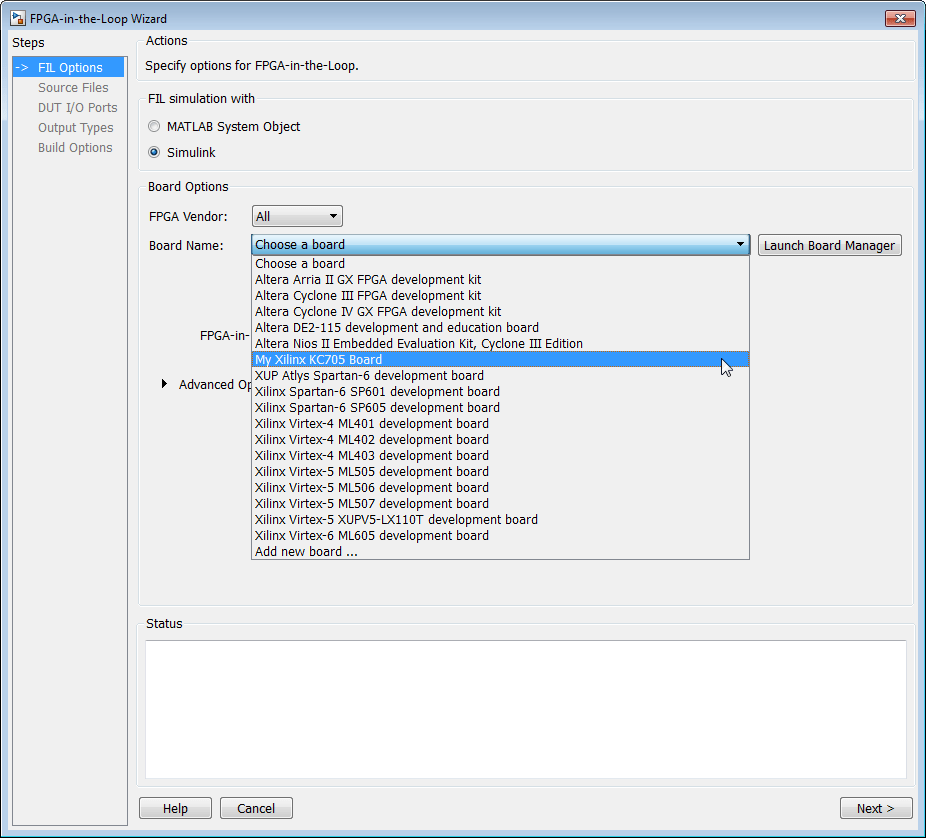

Запустите мастер FIL с подсказки MATLAB.

>>filWizard

Плата Xilinx KC705 появляется в списке плат, и можно выбрать его для FPGA в симуляции цикла.

Запустите HDL Workflow Advisor.

На шаге 1.1 выберите FPGA-in-the-Loop и нажмите Launch Board Manager.

Плата Xilinx KC705 появляется в списке плат, и можно выбрать его для FPGA в симуляции цикла.