Simulink® Design Verifier™ помогает вам выполнить систематическую верификацию модели, чтобы идентифицировать скрытые ошибки проектирования, доказать свойства и сгенерировать тесты для функционального тестирования. Simulink Design Verifier использует формальные методы, чтобы протестировать правильность проекта, которая увеличивает доверие к вашей модели проекта, что генерация производственного кода использует.

Можно выполнить систематическую верификацию модели для сценариев, таких как:

Приложения, которые разрабатываются при помощи Модельно-ориентированного проектирования, где вы выполняете верификацию проекта, чтобы продемонстрировать, что модель удовлетворяет функциональным требованиям и не содержит непредусмотренную функциональность.

Анализ подмножества модели проекта, которая предназначается для программного обеспечения управления. Для анализа регулирования без обратной связи формальная верификация широко используется для строгого тестирования моделей проекта.

Итеративно проверяя вашу модель по требованиям, проверяя на ошибки проектирования и выполняя функциональное тестирование рано в рабочем цикле и в течение процесса проектирования.

Систематическая верификация и тестирование модульного уровня маленьких компонентов в изоляции или для тестирования уровня системы интегрированной модели проекта.

Рассмотрите инженер по системам управления, кто вовлечен в разработку системы управления. Во время рабочего цикла инженер по системам управления создает модель проекта из системных требований. В процессе разработки, инженере:

Идентифицирует и устраняет скрытые ошибки проектирования

Тестовая модель против требований

Выполняет модель и анализ покрытия кода, чтобы подтвердить тщательность тестирования

Недостающее покрытие твердости при помощи генерации тестов и обнаружения мертвой логики

Выполняет базовое и эквивалентное тестирование

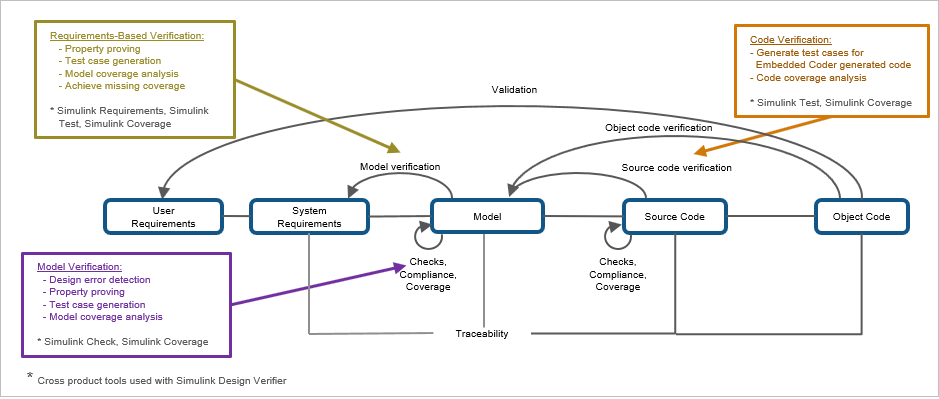

Simulink Design Verifier поддерживает их процессы верификации кода и модель. Это объединяется с Simulink Requirements™, Simulink Coverage™, Simulink Check™ и Simulink Test™, чтобы достигнуть модели и верификации кода.

Верификация модели включает проверку по сравнению со стандартами, проверку ошибки проектирования, доказательство свойств и генерацию тестов для анализа покрытия.

С Simulink Design Verifier вы можете:

Идентифицируйте скрытые ошибки проектирования, такие как целочисленное переполнение или деление на нуль и сгенерируйте контрпримеры, чтобы отладить непредусмотренные функциональности. Можно также выровнять по ширине или исключить объекты модели из анализа.

Проверьте модель по требованиям при помощи Simulink Requirements.

Достигните покрытия модели (Simulink Coverage) путем генерации тестов, который удовлетворяет целям покрытия модели.

Выполните покрытие кода (Embedded Coder) анализ путем генерации тестов для кода, сгенерированного Embedded Coder®.

Расширьте существующие тесты и достигните недостающего покрытия.

Интегрируйте тесты с Simulink Test, чтобы выполнить базовое и эквивалентное тестирование.

Поддержите промышленные стандарты через IEC Certification Kit (для IEC 61508 и ISO 26262) и DO Qualification Kit (for DO-178).

Эта схема рабочего процесса демонстрирует поддержку Simulink Design Verifier на различных этапах рабочего процесса верификации и валидации. Для получения дополнительной информации смотрите Верификацию и Валидацию.

Для краткого введения в поиск ошибок проектирования и генерацию тестов, смотрите, Обнаруживают Ошибки проектирования в Моделях контроллеров и Генерируют Тесты для Упрощенной Модели Круиз-контроля.

Чтобы узнать больше об анализе Simulink Design Verifier, смотрите Поиск ошибок проектирования, Генерацию Теста, Prove Properties в Модели, и Интерпретацию Результатов и Использование.

Можно также сгенерировать отчеты и рассмотреть результаты анализа. Существует несколько способов рассмотреть результаты анализа:

Рассмотрите результаты анализа сразу путем выделения результатов на модели.

Создайте модель тестовой обвязки, чтобы симулировать контрпримеры отладки или тесты.

Сгенерируйте отчет покрытия модели.

Просмотрите сгенерированные тесты в Инспекторе Данных моделирования.

Сгенерируйте HTML или отчет PDF, который содержит подробную информацию о результатах анализа.