В этом примере показано, как можно анализировать модель, которая состоит из периодических подсистем вызова функций. Этот пример использует модель sldvExportFunction_autosar_multirunnables в качестве примера AUTOSAR.

Добавьте папку в качестве примера в путь поиска файлов.

addpath(fullfile(docroot,'toolbox','sldv','examples'));

Откройте sldvExportFunction_autosar_multirunnables модель.

open_system('sldvExportFunction_autosar_multirunnables');Чтобы запустить анализ генерации тестов, на вкладке Design Verifier, нажимают Generate Tests.

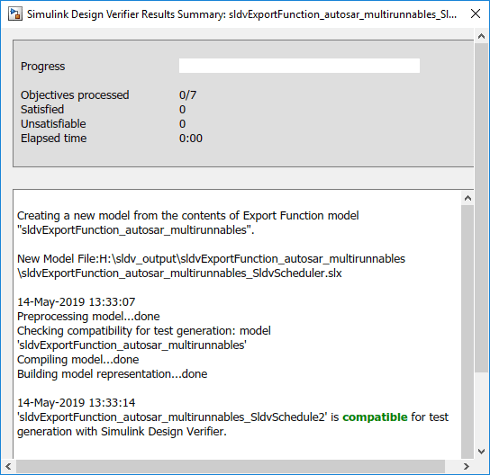

Simulink® Окно Design Verifier™ Results Summary указывает что модель sldvExportFunction_autosar_multirunnables_SldvScheduler.slx планировщика создается. Можно также сгенерировать модель планировщика при помощи sldvextract.

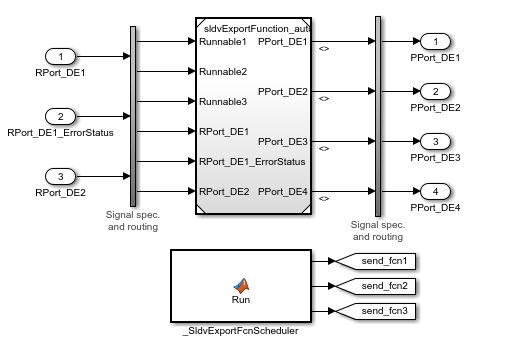

Модель планировщика состоит из блока MATLAB function _SldvExportFcnScheduler. Вызовы функции периодически называются, когда модель состоит из периодической подсистемы вызова функций.

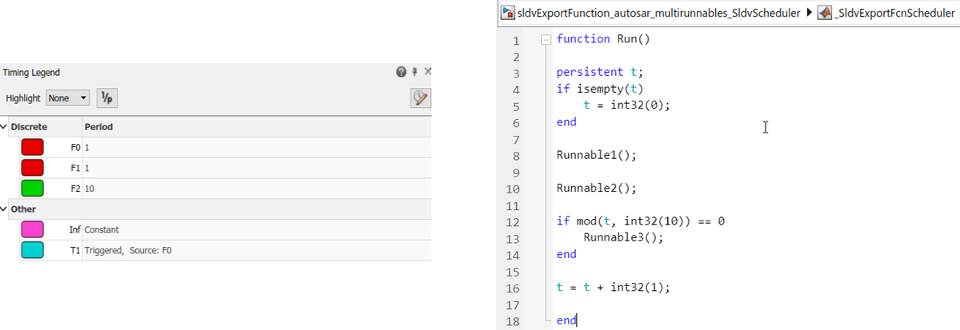

Код MATLAB задает порядок, в котором периодический вызов функции выполняются. Runnable1 и Runnable2 выполняется сначала, потому что периодом времени является 1 для них обоих. После 10 временные шаги, Runnable3 выполняется.

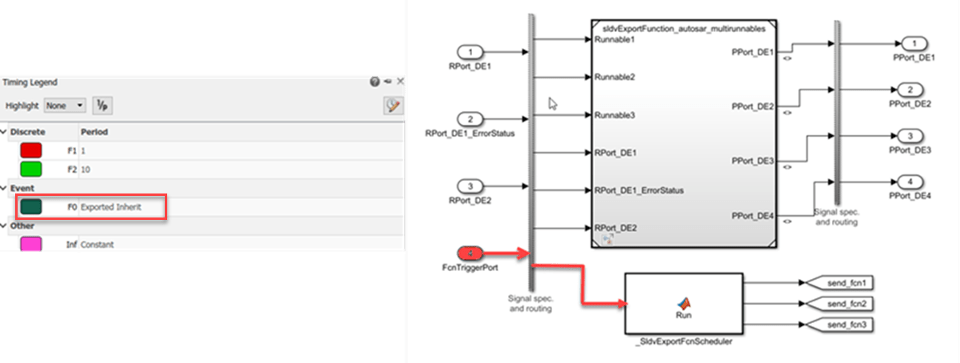

Если модель состоит из апериодических подсистем вызова функций, планировщик состоит из дополнительного импорта FcnTriggerPort. Значение FcnTriggerPort указывает, вызвать ли вызов функции во временном шаге.

Например, если Runnable1 апериодическая подсистема вызова функций, FcnTriggerPort

Блок Inport вызывает модель планировщика. Эта диаграмма показы окно Timing Legend и модель планировщика для апериодического вызова функции.

После анализа генерации тестов, в окне Simulink Design Verifier Results Summary, вы видите результаты что 7/7 целями является Satisfied.

Чтобы симулировать тесты и сгенерировать отчет покрытия, нажмите Simulate tests and produce a model coverage report в окне Simulink Design Verifier Results Summary.

Программное обеспечение симулирует тесты, собирает информацию покрытия модели и отображает отчет покрытия.

Чтобы просмотреть отчет детального анализа, нажмите HTML в окне Simulink Design Verifier Results Summary.

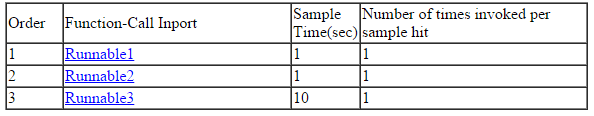

Раздел Schedule for Export Function Analysis в главе информации об Анализе перечисляет расписание для вызова экспортов функций.

Запланируйте для анализа экспорта функций