Во время анализа поиска ошибок проектирования программное обеспечение проверяет заданные минимальные и максимальные значения на промежуточных сигналах в модели и на выходных портах. Эти значения задают design ranges.

Анализ проверяет на заданные минимальные и максимальные значения на:

Simulink® блокируйте выходные параметры, за исключением ограничений, описанных в следующем разделе

Simulink.Signal объекты

Stateflow® объекты данных

MATLAB® для объектов данных генерации кода

Глобальные данные хранят записи

Если анализ обнаруживает, что сигнал превышает область значений проекта, результаты идентифицируют, где в модели ошибки произошли. Кроме того, можно сгенерировать модель тестовой обвязки, которая содержит тесты, которые демонстрируют, как ошибка произошла.

Если вы анализируете модель, проверяющую, если задано, что минимальные и максимальные значения превышены, программное обеспечение не может проверять минимальные и максимальные значения, заданные на:

Любой блок Mux с выходом, соединенным с блоком Selector

Входные параметры блока Merge

Чтобы работать вокруг этого ограничения, используйте Simulink.Signal объект на блоке Merge выход и указывает диапазон на Simulink.Signal объект.

Примечание

Для получения информации о том, как анализ Simulink Design Verifier™ указатели задали минимальные и максимальные значения на входных портах, смотрите Минимальные и Максимальные Входные Ограничения.

В этом разделе вы создаете и анализируете модель, которая задала проект минимальные и максимальные значения на:

Входные порты

Выходные порты двух из промежуточных блоков

Анализ поиска ошибок проектирования идентифицирует блоки, где выходные значения превышают область значений проекта. Если анализ обнаруживает эту ошибку, этот пример демонстрирует, как анализ использует заданные минимальные и максимальные значения при продолжении анализа.

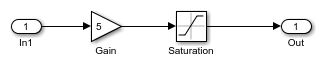

Создайте модель для этого примера:

В панели инструментов MATLAB, на вкладке Home, выбирают New> Simulink Model.

От библиотеки Simulink Commonly Used Blocks добавьте следующие блоки в модель и присвойте обозначенные значения параметров.

| Блок | Вкладка | Параметр | Значение |

|---|---|---|---|

| Inport | Signal Attributes | Minimum | 0 |

| Inport | Signal Attributes | Maximum | 5 |

| Усиление | Main | Gain | 5 |

| Усиление | Signal Attributes | Output minimum | 0 |

| Усиление | Signal Attributes | Output maximum | 20 |

| Усиление | Signal Attributes | Output data type | int16 |

| Насыщение | Main | Upper limit | 25 |

| Насыщение | Main | Lower limit | -25 |

| Насыщение | Signal Attributes | Output minimum | -25 |

| Насыщение | Signal Attributes | Output maximum | 25 |

| Выходной порт | Никакие изменения | ||

Соедините четыре блока как показано.

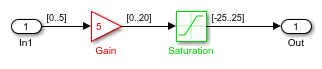

Чтобы отобразить заданные минимальные и максимальные значения, на вкладке Debug, выбирают Information Overlays> Signal Data Ranges.

На вкладке Modeling нажмите Model Settings.

В диалоговом окне Configuration Parameters, на панели Solver, под Solver selection:

Установите Type на Fixed-step.

Программное обеспечение Simulink Design Verifier не поддерживает решатели переменного шага.

Установите Solver на discrete (no continuous states).

На панели Design Verifier, набор Mode к Design error detection.

На Design Verifier> панель Design Error Detection:

Выберите Specified minimum and maximum value violations.

Очистите параметры Division by zero и Integer overflow.

В этом примере вы проверяете только на промежуточные минимальные и максимальные нарушения.

Чтобы сохранить эти настройки и выйти из диалогового окна Configuration Parameters, нажмите OK.

Сохраните модель и назовите ее ex_interim_minmax.

Чтобы анализировать модель в качестве примера, чтобы идентифицировать любые промежуточные сигналы, которые нарушают заданные минимальные и максимальные значения, выполните анализ поиска ошибок проектирования.

На вкладке Design Verifier нажмите Detect Design Errors.

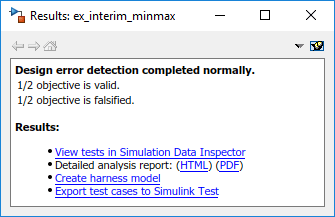

После того, как анализ завершен:

Программное обеспечение подсвечивает модель с результатами анализа.

Диалоговое окно Simulink Design Verifier Results открывает и отображается сводные данные анализа.

В окне модели блок Gain окрашен в красный, и блок Saturation окрашен в зеленый. Это указывает что:

По крайней мере одна цель, сопоставленная с блоком Gain, была сфальсифицирована. В данном примере анализ, сфальсифицированный точно одна цель.

Удовлетворили всем целям, сопоставленным с блоком Saturation. В данном примере анализ, которому удовлетворяют точно одна цель.

Изучать эти результаты:

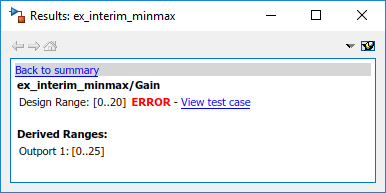

Кликните по блоку Gain.

Окно Simulink Design Verifier Results показывает, что область значений проекта для выхода была [0.. 20], но анализ обнаружил ошибку и сгенерировал тест, который демонстрирует ту ошибку. Поскольку область значений проекта для входного блока [0.. 5], когда вход с блоком Gain равняется 5, выход равняется 25, который превышает заданное максимальное значение на том порте.

Анализ вычисляет и отображает выведенную область значений, чтобы помочь вам изучить, как область значений проекта была превышена.

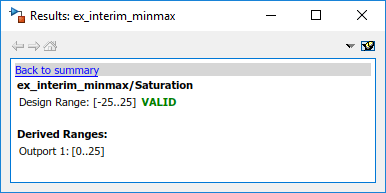

Кликните по блоку Saturation.

Окно Simulink Design Verifier Results показывает, что выход блока Saturation никогда не превышал область значений проекта [–25.. 25]. Вход с блоком Saturation, никогда превышаемым [0.. 25], который является выведенной областью значений, которую анализ распространил от блока Gain.

То, когда анализ завершается, можно создать модель тестовой обвязки, содержит тесты тот результат по ошибкам.

Для модели в качестве примера просмотрите тест, который вызвал ошибку области значений проекта в блоке Gain:

После того, как анализ завершается, и модель подсвечена, кликните по блоку Gain.

В окне Simulink Design Verifier Results нажмите View test case.

Программное обеспечение создает модель тестовой обвязки под названием ex_interim_minmax_harness и открывает блок Signal Builder в модели тестовой обвязки, которая содержит тест.

В блоке Signal Builder один тест, значение сигналов которого равняется 5, заставил выход блока Gain быть 25, который превышает заданный максимум 20.

Прежде чем вы симулируете этот тест, в диалоговом окне Configuration Parameters, на панели Diagnostics > Data Validity, установите Simulation range checking на warning или error.

Установка этого параметра задает диагностическое действие, чтобы взять, если Simulink обнаруживает сигналы, которые превышают заданные минимальные или максимальные значения в процессе моделирования.

Если вы задаете warning, симуляция отображает предупреждающее сообщение и продолжается.

Если вы задаете error, симуляция отображает сообщение об ошибке и остановки.

Нажмите OK, чтобы сохранить ваше изменение и закрыть диалоговое окно Configuration Parameters.

В окне блока Signal Builder нажмите Start simulation, чтобы симулировать модель с этим тестом.

Как ожидалось, в окне MATLAB, симуляция выводит предупреждение или ошибку, что выходное значение блока Gain превышает заданный максимум.

Можно также сгенерировать отчет HTML, содержащий подробную информацию об аналитическом отчете для ex_interim_minmax модель. Чтобы создать этот отчет, в окне Simulink Design Verifier Results, нажимают Generate detailed analysis report. Аналитический отчет открывает в браузере.

В аналитическом отчете глава Design Error Detection Objectives Status отчета обеспечивает подробные результаты в двух категориях:

Objectives Proven Valid — Выходные значения для блока Saturation всегда в области значений проекта.

Objectives Falsified with Test Cases — Выходные значения для блока Gain нарушили область значений проекта.