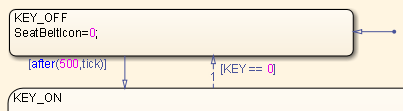

Этот пример использует sldvdemo_sbr_extend_design модель. Эта модель включает Stateflow® стройте диаграмму SBR это использует временную логику. Переход от KEY_OFF утвердите к KEY_ON состояние происходит после того, как диаграмма Stateflow была симулирована 500 раз. Протестировать этот переход требует теста с 500 временными шагами.

В этом примере вы создаете тест, который обеспечивает переход к KEY_ON путем установки KEY введите к 1 на время теста. Вы симулируете модель с помощью этого теста, удовлетворяя целям для KEY_OFF/KEY_ON переход. Затем вы анализируете модель, игнорируя цели, которым уже удовлетворяет тест, который вы создаете.

Откройте модель в качестве примера:

Откройте SBR Диаграмма Stateflow, чтобы видеть KEY_OFF/KEY_ON переход.

Создайте модель тестовой обвязки модели - ссылки:

[~, harnessModelFilePath] = ...

sldvmakeharness('sldvdemo_sbr_extend_design',[],[],true);Модель тестовой обвязки, sldvdemo_sbr_extend_design_harness, включает:

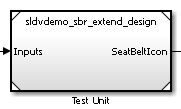

Блок Model под названием Тестовый Модуль, который ссылается на исходную модель, sldvdemo_sbr_extend_design.

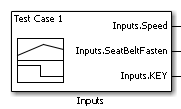

Блок Signal Builder под названием Входные параметры, который содержит входные параметры testcase к модели, на которую ссылаются в блоке Model.

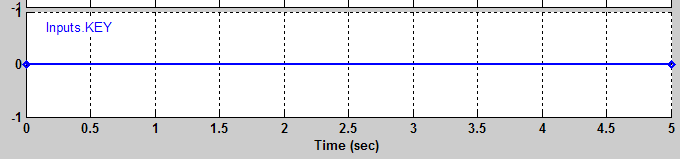

Первоначально, блок Signal Builder содержит только тест по умолчанию со всеми тремя входными наборами к 0.

Блок DocBlock под названием Объяснение Теста это документирует тест.

Первоначально, блок Test Case Explanation не имеет никакого содержимого для теста по умолчанию.

sldvmakeharness возвращает путь к файлу модели тестовой обвязки в harnessModelFilePath. Извлеките имя файла модели тестовой обвязки в harnessModel, для дальнейшего использования:

[~, harnessModel] = fileparts(harnessModelFilePath);

Для того, чтобы анализировать KEY_OFF к KEY_ON изменение состояния, создайте тест, который делает переход к KEY_ON состояние в 500 временных шагах:

Откройте диалоговое окно Signal Builder для модели тестовой обвязки.

Выберите Axes> Change Time Range.

Область значений времени Signal Builder определяет промежуток времени, за которое явным образом задан его выход. В Наборе общее диалоговое окно области значений времени, набор поле Max time к 5 секунды, создавая 500 временных шагов длительности 0,01 секунд каждый.

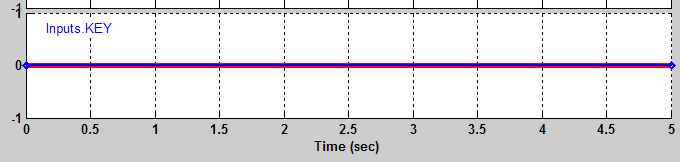

Установите KEY введите к 1 на время этого стартового теста, обеспечивая переход к KEY_ON состояние. Выбор Inputs.KEY сигнал требует двух нажатий кнопки. Во-первых, кликните по сигналу так, чтобы точки появились в обоих концах сигнала.

Нажмите Inputs.KEY предупредите снова. Signal Builder утолщает сигнал указать, что это выбрано.

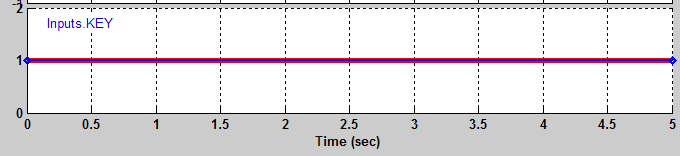

В нижней части диалогового окна Signal Builder, под Left Point, вводят 1 для Y.

Нажмите Enter, чтобы применить изменение.

Inputs.KEY сигнал установлен в 1 на время теста.

Закройте диалоговое окно Signal Builder.

Следующий шаг должен регистрировать стартовый тест, который вы создали. Можно затем задать тот Simulink® Design Verifier™ игнорирует цели, которым удовлетворяет тот тест при выполнении анализа.

sldvlogsignals функционируйте записывает данные о тесте в MAT-файле, который содержит sldvData структура. Эта структура хранит все данные, которые программное обеспечение собирает и производит во время анализа.

Регистрировать стартовые тесты:

Сохраните имя блока Model в модели тестовой обвязки, это ссылается на sldvdemo_sbr_extend_design модель:

[~, modelBlock] = find_mdlrefs(harnessModel, false);

Симулируйте модель, на которую ссылается блок Model с помощью нового теста, и регистрируйте входные сигналы в переменной loggeddata рабочей области:

loggeddata = sldvlogsignals(modelBlock{1});Сохраните записанные данные в MAT-файле под названием existingtestcase.mat:

save('existingtestcase.mat', 'loggeddata');Вы зададите этот файл, когда вы будете анализировать sldvdemo_sbr_extend_design модель.

Можно теперь анализировать sldvdemo_sbr_extend_design модель и указывает, что анализ расширяет тесты, которым уже удовлетворяют. Анализ использует данные о существующем тесте в качестве начальной точки и не пытается сгенерировать тесты для KEY_OFF к KEY_ON переход в диаграмме Stateflow SBR.

Задайте стартовый тест и анализируйте модель:

Откройте модель.

open_system('sldvdemo_sbr_extend_design');На вкладке Design Verifier нажмите Test Generation Settings.

В диалоговом окне Configuration Parameters, на панели Test Generation, под Existing test cases, выбирают Extend existing test cases.

В поле Data file введите имя MAT-файла, который содержит записанные данные:

existingtestcase.mat

Очистите Ignore objectives satisfied by existing test cases.

Когда вы очищаете эту опцию, программное обеспечение включает стартовый тест в набор завершающего испытания. Вы будете видеть, что полный тестовый набор достигает 100%-го покрытия модели.

Чтобы закрыть диалоговое окно Configuration Parameters, нажмите OK.

Сохраните sldvdemo_sbr_extend_design модель на MATLAB® путь с именем sldvdemo_sbr_extend_design_test.

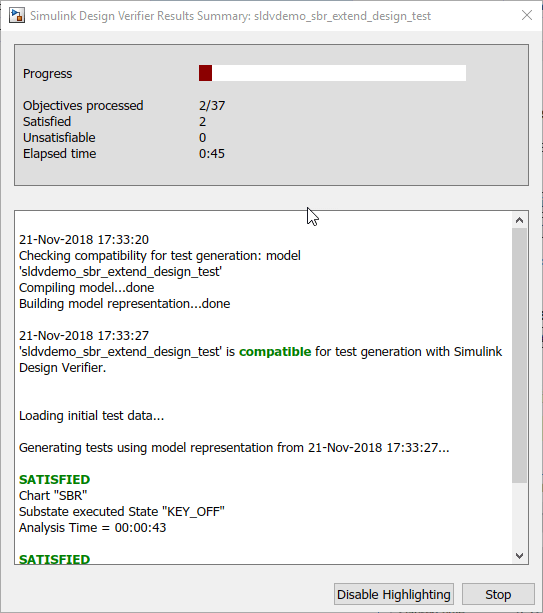

Нажмите Generate Tests.

Логарифмическое окно сначала перечисляет цели что стартовый тест, которому удовлетворяют.

Логарифмическое окно затем перечисляет цели, сгенерированные вне стартового теста.

Чтобы убедиться, что этот анализ создает полный тестовый набор, сгенерируйте модель тестовой обвязки, таким образом, можно симулировать модель со сгенерированными тестами:

На вкладке Design Verifier, в разделе Review Results, нажимают Create Test Harness Model.

В модели тестовой обвязки sldvdemo_sbr_extend_design_test_harness, откройте блок Signal Builder под названием Входные параметры.

Чтобы симулировать модель с помощью всех тестов, нажмите кнопку Run all and produce coverage![]() .

.

Когда симуляция завершена, отчет покрытия модели отображен.

Просмотрите информацию о покрытии для sldvdemo_sbr_extend_design_test модель, чтобы видеть, что полный тестовый набор достигает 100%-го покрытия.