Один способ упростить вашу модель состоит в том, чтобы использовать для обозначенного типа данных сигнала тип данных, требующий наименьшего количества суммы пробела для ожидаемых данных. Например, не используйте int тип данных для булевых данных, потому что только один бит требуется для булевых данных.

В другом примере предположите, что у вас есть блок Sum с двумя входными параметрами, которые всегда являются целыми числами между –10 и 10. Установите параметр Output data type на int8, вместо int32 или double.

Чтобы отобразить типы данных сигнала, на вкладке Debug, нажимают Information Overlays> Port Data Type.

Другой эффективный метод для сокращения сложности должен ограничить входные параметры набором представительных значений или, идеально, одно постоянное значение. Этот процесс, названный discretization, обрабатывает вход, как будто это было перечисление. Дискретизация позволяет вам обрабатывать нелинейную арифметику от умножения и деления самым простым возможным способом.

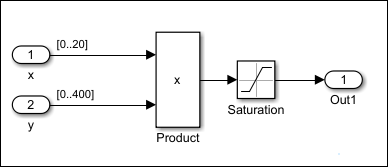

Следующая модель имеет блок Product, питающий блок Saturation. Входные параметры x и y имейте определенные области значений проекта как показано, и блок Saturation ограничивает входной сигнал верхними и более низкими степенями насыщения, который составляет 8000 и 0 об/мин.

Simulink® Программное обеспечение Design Verifier™ генерирует ошибки при попытке удовлетворить верхнему и нижним пределам блока Saturation, потому что программное обеспечение не поддерживает нелинейную арифметику. Чтобы работать вокруг этих ошибок, ограничьте одни из входных параметров к набору дискретных значений.

Идентифицируйте дискретные значения, которые требуются, чтобы удовлетворять вашим потребностям тестирования. Например, у вас может быть вход для скорости модели, и ваш проект содержит пути выполнения, которые обусловливаются на скорости выше или ниже порогов 80, 150, 600, и 8 000 об/мин. Для эффективного анализа ограничьте значения скорости быть 50, 100, 200, 1000, 5000, или 10 000 об/мин так, чтобы каждый порог мог быть или активным или неактивным.

Если необходимо использовать больше чем два или три значения, рассмотрите определение ограниченных значений с помощью выражения как

num2cell(minval:increment:maxval)

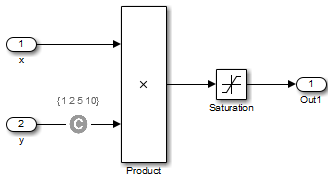

Используя модель предыдущего примера, ограничьте второй вход (y), чтобы быть любой 1, 2, 5, или 10 использование блока Test Condition как показано в следующей модели. Программное обеспечение Simulink Design Verifier производит тесты для всех входных параметров.

Можно также ограничить сигналы, которые являются промежуточными или выходными значениями модели. Ограничение таких сигналов облегчает работать вокруг умножения или деления в более низких подсистемах уровня, которые не зависят от входных параметров модели.

Примечание

Дискретизация лучше всего ограничивается небольшим количеством входных параметров (меньше чем 10). Если ваша модель требует дискретизации многих входных параметров, попытайтесь достигнуть покрытия модели посредством последовательных симуляций, как описано во Входных параметрах Модели Раздела для Инкрементной Генерации тестов.

Блоки Условия испытания не должны быть помещены точно на входных параметрах. В решении, куда поместить ограничения в вашу модель, рассмотрите следующие инструкции:

Одобрите ограничения на входные значения, потому что программное обеспечение может обработать легче входные параметры.

Если необходимо поместить ограничения и на вход и на выход, например, чтобы избежать нелинейной арифметики, одно из ограничений должно быть областью значений, такой как [minval maxval]. Программное обеспечение сначала тестирует значения в обоих концах области значений и может возвратить тест, даже если базовые вычисления нелинейны.

Убедитесь, что ограничения в соответствующих точках ввода и вывода не являются противоречащими. Не ограничивайте выходные сигналы к значениям, которые не достижимы из-за ограничений на входные значения.

Постарайтесь не создавать ограничения, которые противоречат модели. Такие противоречия происходят, когда ограничению никогда нельзя удовлетворять, потому что оно противоречит некоторому аспекту модели или другого ограничения. Анализ противоречащих моделей может заставить Simulink Design Verifier висеть.

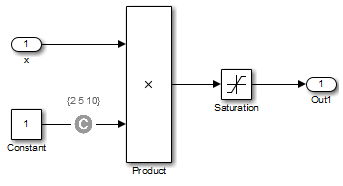

Следующая модель является простым примером противоречащей модели. Вторым входом с блоком Multiply является постоянный 1, но блок Test Condition ограничивает его к значению 2, 5, или 10. Анализ не может достигнуть всех целей тестирования в этой модели.

Когда вы работаете с большими моделями, которые имеют многих умножение и операции деления, можно найти легче добавить ограничения во все входные параметры с плавающей точкой, а не идентифицировать точный набор входных параметров, которые требуют ограничений.