Когда вы задаете ограничения входного диапазона на Simulink® и Stateflow® элементы, Simulink Design Verifier™ рассматривает эти ограничения во время анализа.

После того, как вы зададите выход минимальные и максимальные значения на Inport блоках, анализ Simulink Design Verifier использует минимальные и максимальные значения в качестве ограничений.

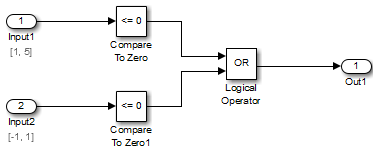

Следующая модель в качестве примера ограничивает сигналы в двух Inport блоках:

Блок Input1: Минимум: 1, Максимум: 5

Блок Input2: Минимум:-1, Максимум: 1

Когда вы используете Simulink Design Verifier, чтобы анализировать эту модель, анализ приводит к этим результатам:

Выход от Input1 никогда не меньше 0, поэтому первым входом с блоком Logical Operator никогда не является false. Цель, что первый вход к Логическому оператору равняется false невыполнимо.

Блок Logical Operator не может достигнуть 100% измененное условие/Decision Coverage (MCDC) покрытие, потому что условие, где первым входом является false никогда не происходит.

Отчет детального анализа показывает значения, которые вы используете в качестве ограничений для Input1 и Input2.

Примечание

Simulink Design Verifier полагает, что полный спектр возможных значений (и любые минимальные и максимальные ограничения) для корневого уровня импортирует только.

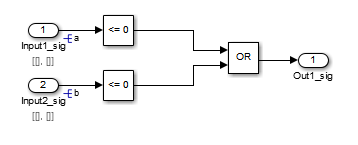

Simulink.Signal ОбъектыИспользуя Model Explorer, в рабочем пространстве модели, можно задать минимальные и максимальные значения на Simulink.Signal объекты сопоставлены с входными сигналами.

Следующая модель в качестве примера использует Simulink.Signal объекты сопоставили с входными сигналами a и b ограничить значения сигналов:

a сигнала: Минимум: 1, максимум: 5

b сигнала: Минимум:-1, максимум: 1

Когда вы анализируете эту модель, результаты эквивалентны, если вы задали минимальные и максимальные значения на входных портах.

Если вы указываете диапазоны на Inport блоках и на сигналах, анализ рассматривает самую маленькую область значений для значений. Например, если вы указываете диапазон 4..12 на входном порте и области значений 1..8 на сигнале от входного порта анализ считает область значений 4..8.

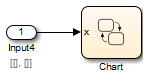

Используя Model Explorer, можно указать диапазоны на объектах данных, которые непосредственно соединяются с входными портами корневого уровня для диаграммы Stateflow.

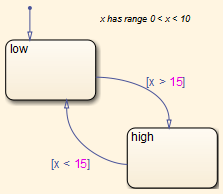

В следующей модели в качестве примера диаграмма Stateflow под названием График имеет объект данных, x, чей диапазон вы указали как 0 <x <10. В этом графике, x должен быть больше 15, чтобы инициировать переход от low к high.

Значение x диапазоны от 0 до 10, поэтому условие перехода [x > 15] никогда не true. Переход от low к high никогда не происходит. Поскольку high состояние никогда не вводится, условие перехода [x < 15] никогда не тестируется, и переход от high к low никогда не происходит. График всегда находится в low состояние.

Когда вы анализируете эту модель, эти цели доказаны невыполнимыми:

high состояние никогда не вводится.

Условие перехода [x > 15] всегда false, никогда true.

Условие [x < 15] никогда не тестируется, таким образом, это никогда не true или false.

Аналитический отчет указывает на значения, которые вы используете в качестве ограничений для x: [0, 10].

Программное обеспечение Simulink Design Verifier считает заданным, вводит минимальные и максимальные значения как ограничения только в верхнем уровне модели. Можно задать минимальные и максимальные значения на Input port на подсистемах, но когда вы анализируете модель верхнего уровня, программное обеспечение игнорирует те значения.

Когда вы выполняете анализ подсистемы, программное обеспечение рассматривает заданные минимальные и максимальные значения на входных портах подсистемы.

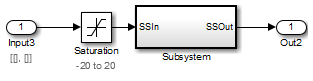

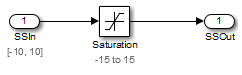

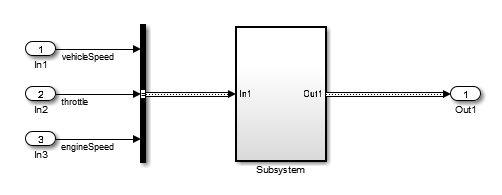

Например, рассмотрите следующую модель и ее подсистему.

В Подсистеме заданных минимальных и максимальных значениях для входного порта SSIn-10 и 10, соответственно. Нижние и верхние пределы для блока Saturation-15 и 15, соответственно.

Если вы щелкаете правой кнопкой по Subsystem по модели верхнего уровня и выбираете Design Verifier> Generate Tests for Subsystem, анализ рассматривает заданные минимальные и максимальные значения как ограничения на порт SSIn.

Ограничения: спроектируйте Max constraint Min

Анализ идентифицирует две невыполнимых цели:

введите> нижний предел F: вход всегда больше нижнего предела на блоке (-15) Saturation.

введите> = верхний предел T: вход никогда не больше или равен верхнему пределу блока (15) Saturation.

Если вы анализируете модель, которая содержит Подсистему, анализ не считает значения заданными на входном порте SSIn в подсистеме. Анализ рассматривает только входные порты корневого уровня на соответствующем уровне иерархии для анализа.

data store является репозиторием, к которому можно записать данные и от которого можно считать данные, не имея необходимость соединять сигнал ввода или вывода непосредственно с хранилищем данных. Вы создаете хранилище данных при помощи блока Data Store Memory или Simulink.Signal объект. Можно задать минимальные и максимальные значения для любого хранилища данных.

Во время анализа подсистемы Simulink Design Verifier создает входной порт, чтобы подражать контексту выполнения для хранилища глобальных данных. Для получения дополнительной информации смотрите Подсистемы Извлечения для Анализа. Если хранилище данных задало минимальные и максимальные значения, те значения присвоены как минимальные и максимальные значения на новом входном порте. Анализ Simulink Design Verifier считает вход минимальными и максимальными значениями как аналитические ограничения уровня подсистемы.

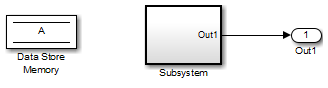

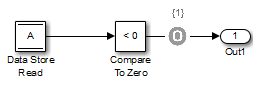

В следующей модели в качестве примера, хранилище данных A имеет минимальное значение 0 и максимальное значение 10.

Атомарная подсистема читает значения из хранилища данных и проверок, чтобы видеть, меньше ли вход 0. Выходные параметры блока Compare To Zero 1, если вход меньше 0, и выходные параметры 0, если вход больше или равен 0. Проверки блока Test Objective, чтобы видеть, равняется ли выход когда-нибудь 1.

В модели верхнего уровня, если вы щелкаете правой кнопкой по Subsystem и выбираете Design Verifier> Generate Tests for Subsystem, анализ считает ограничения для хранилища данных A быть [0, 10].

Анализ не удовлетворяет цели, заданной в блоке Test Objective. Вход всегда больше или равен 0, поэтому выход от блока Compare To Zero всегда 0.

Когда вы задаете шину, можно задать минимальные и максимальные значения для элементов в шине. Simulink Design Verifier рассматривает эти минимальные и максимальные значения при анализе подсистем и моделей, которые используют шину в качестве входного сигнала.

Рассмотрите подсистему, которая вводит шину трех полей, каждого с заданным минимумом и максимумом. Просмотреть эту подсистему, в командной строке, введите:

open_system(fullfile(docroot,'toolbox','sldv','examples',... 'sldvBusMinMaxExample'));

| Соедините шиной элемент | Соедините шиной минимум элемента | Соедините шиной максимум элемента |

|---|---|---|

| vehicleSpeed | 0 | 125 |

| дроссель | 0 | 100 |

| engineSpeed | 0 | 7600 |

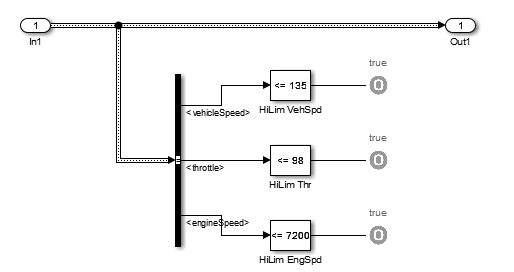

Подсистема имеет цели тестирования, которые подтверждают, что каждый элемент не превышает константу. vehicleSpeed сигнал ограничивается максимальным значением ниже, чем цель тестирования.

Установите текущую папку на перезаписываемую папку. В режиме верхнего уровня щелкните правой кнопкой по Subsystem и выберите Design Verifier> Generate Tests for Subsystem. Цель Условия для тестирования vehicleSpeed > 135 не выполнимо из-за максимальной спецификации на vehicleSpeed элемент.