Используя SoC Blockset™, можно смоделировать упрощенный, передающий потоком протокол в модели. Используйте HDL Coder™, чтобы сгенерировать AXI4-потоковые интерфейсы в ядре IP.

Когда это необходимо, чтобы сгенерировать интерфейс AXI4-Stream в вашем ядре IP, в вашем интерфейсе DUT, реализуют следующие сигналы:

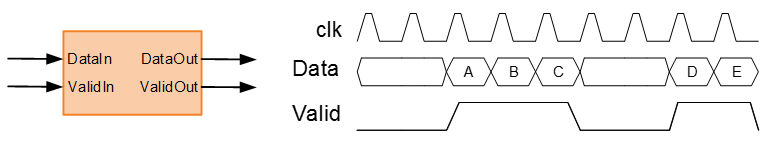

Данные

Допустимый

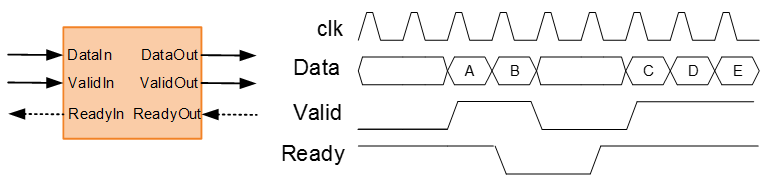

Когда вы сопоставляете скалярные порты DUT с интерфейсом AXI4-Stream, можно опционально смоделировать следующие сигналы и сопоставить их с интерфейсом AXI4-Stream:

Готовый

Другие сигналы протокола, такие как:

TSTRB

TKEEP

TLAST

TID

TDEST

TUSER

Когда сигнал Данных допустим, Допустимый сигнал утверждается.

AXI4-потоковые интерфейсы в вашем DUT могут опционально включать Готовый сигнал. В интерфейсе Slave Готовый сигнал позволяет вам применить противодавление. В интерфейсе Master Готовый сигнал позволяет вам ответить на противодавление.

Если вы моделируете Готовый сигнал в своих AXI4-потоковых интерфейсах, ваш интерфейс Master игнорирует Данные и Допустимые сигналы один такт после того, как Готовый сигнал является deasserted. Можно начать отправлять Данные и Допустимые сигналы, если Готовый сигнал утверждается. Можно отправить еще одни Данные и Допустимый сигнал после того, как Готовый сигнал будет deasserted.

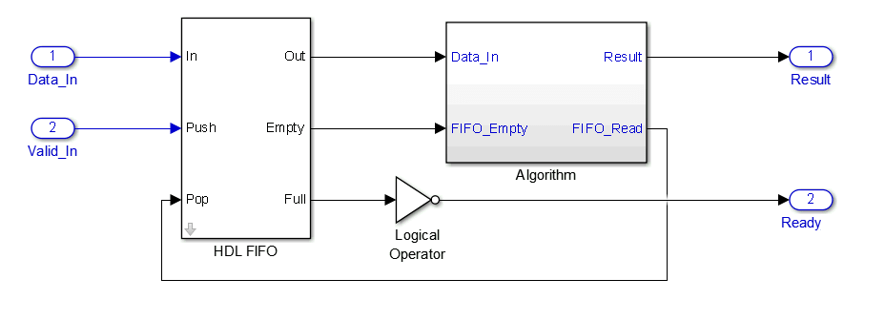

Если вы не моделируете Готовый сигнал, HDL Coder генерирует сигнал и связанную логику противодавления.

Например, если у вас есть FIFO в вашем DUT, чтобы сохранить систему координат данных, применить противодавление к восходящему компоненту, можно смоделировать Готовый сигнал на основе FIFO Полный сигнал.

Memory Channel | SoC Bus Creator