Можно использовать Simulink® для быстрого прототипирования аппаратных проектов. Блоки Wireless HDL Toolbox™, когда используется с HDL Coder™, поддерживают генерацию HDL-кода. Инструменты HDL Coder генерируют независимый от цели синтезируемый Verilog® и VHDL® код для программирования FPGA или прототипирования ASIC и проекта.

Большинство блоков в Wireless HDL Toolbox поддерживает генерацию HDL-кода.

Следующие блоки для симуляции только и не поддерживаются для генерации HDL-кода:

Frame To Samples

Samples To Frame

FIL Frame To Samples

FIL Samples To Frame

Другой MathWorks® продукты также включают блоки, поддержанные для генерации HDL-кода, которую можно использовать, чтобы создать проект.

В браузере Библиотеки Simulink можно найти библиотеки блоков поддерживаемыми для генерации HDL-кода в HDL Coder, Communications Toolbox HDL Support, библиотеках блоков DSP System Toolbox HDL Support и других.

Чтобы создать библиотеку поддержанных HDL блоков из всех ваших установленных продуктов, войти hdllib (HDL Coder) в MATLAB® командная строка. Эта команда требует лицензии HDL Coder.

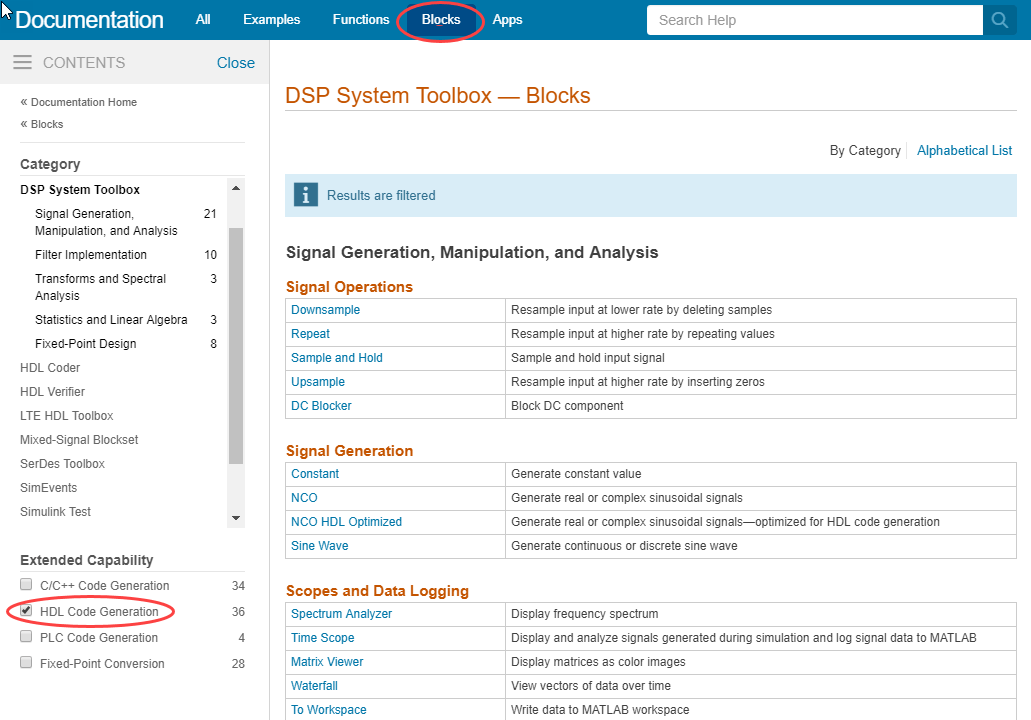

Можно также просмотреть блоки, которые поддерживаются для генерации HDL-кода в документации путем фильтрации списка ссылок блока. Нажмите Blocks в синей панели наверху окна Help, затем установите флажок HDL code generation в нижней части левого столбца. Блоки перечислены в их соответствующих продуктах. Можно использовать оглавление в левом столбце, чтобы перейти между продуктами и категориями.

Обратитесь к разделу "Extended Capabilities> HDL Code Generation" каждой страницы блока для реализаций блока, свойств и ограничений для генерации HDL-кода.

Передающий потоком демонстрационный тип данных шины управления, используемый блоками Wireless HDL Toolbox, сглажен в отдельные сигналы в HDL.

В VHDL интерфейс объявляется как:

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

in0 : IN std_logic_vector(7 DOWNTO 0); -- uint8

in1_start : IN std_logic;

in1_end : IN std_logic;

in1_valid : IN std_logic;

out0 : OUT std_logic_vector(7 DOWNTO 0); -- uint8

out1_start : OUT std_logic;

out1_end : OUT std_logic;

out1_valid : OUT std_logic

);

В Verilog интерфейс объявляется как:

input clk; input reset; input enb; input [7:0] in0; // uint8 input in1_start; input in1_end; input in1_valid; output [7:0] out0; // uint8 output out1_start; output out1_end; output out1_valid;