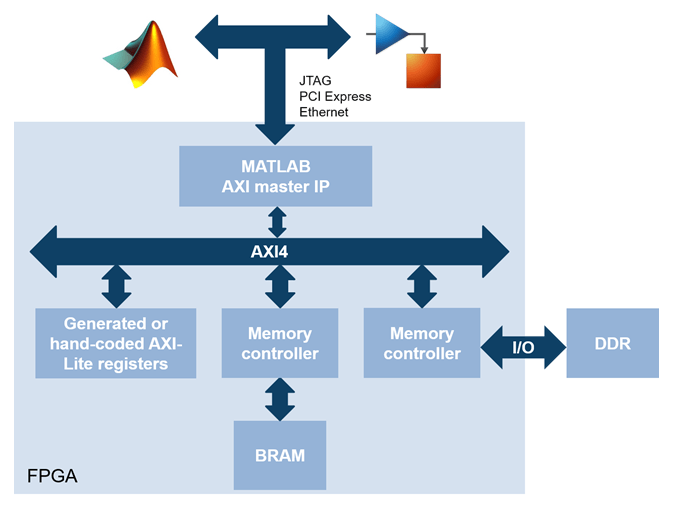

К местоположениям встроенной памяти доступа из MATLAB® или Simulink®, необходимо включать ведущий IP AXI MATLAB в проект FPGA. Этот IP соединяется с ведомыми ячейками памяти на плате. IP также отвечает на чтение и команды записи из MATLAB или Simulink, по JTAG, PCI Express или кабелю Ethernet.

Чтобы использовать эту функцию, необходимо загрузить пакет аппаратной поддержки для платы FPGA. Смотрите Пакет поддержки плат FPGA Загрузки.

Чтобы настроить основной IP AXI для доступа из MATLAB или Simulink, выполните эти шаги настройки:

Включайте ведущий IP AXI MATLAB в свой проект FPGA. Чтобы добавить путь для файлов IP к вашему проекту, вызовите setupAXIMasterForVivado или setupAXIMasterForQuartus функции.

Открытый Vivado® или Куарт®, и от IP Каталог выбирают ведущий IP MATLAB AXI в вашем проекте FPGA.

При использовании JTAG как физическое соединение выберите MATLAB as AXI Master.

При использовании Ethernet как физическое соединение выберите UDP Matlab as AXI Master и Ethernet MAC Hub и добавьте их в свой проект.

При использовании PCIe как физическое соединение выберите PCIe MATLAB as AXI Master и добавьте его в свой проект.

В вашем проекте FPGA задайте, к каким адресам основному IP AXI позволяют получить доступ.

Примечание

Основной IP AXI поддерживает AXI4 Облегченный, AXI4 и Altera® Ведомые ячейки памяти Авалона. Межсоединение FPGA автоматически преобразует транзакции AXI4 в протокол каждого адреса.

Скомпилируйте свой проект FPGA, включая ведущий IP AXI MATLAB.

Соедините свою плату FPGA с вашим хостом - компьютером с помощью физического кабеля (JTAG, PCI Express или кабель Ethernet).

Программируйте FPGA со своим скомпилированным проектом.

Примечание

В качестве альтернативы можно выполнить эти шаги в ведомом рабочем процессе HDL Coder™ при помощи демонстрационного исходного проекта, такого как тот, включенный в эти примеры: Доступ к Регистрам DUT на Intel Чистая плата FPGA Используя Рабочий процесс Генерации Ядра IP (HDL Coder) или доступ к Регистрам DUT на Xilinx Чистый Совет FPGA Используя Рабочий процесс Генерации Ядра IP (HDL Coder).

После загрузки проекта на вашем FPGA можно получить доступ к местоположениям с отображенной памятью на плате.

Чтобы получить доступ к плате из MATLAB, создайте aximaster возразите и используйте readmemory и writememory методы, чтобы читать и записать местоположения с отображенной памятью на плате.

Чтобы получить доступ к плате от Simulink, создайте модель Simulink и включайте AXI Master Read и AXI Master Write в нем. Сконфигурируйте блоки, чтобы считать и записать местоположения с отображенной памятью на плате.

При использовании JTAG как физическое соединение к вашей плате у вас может быть дополнительный дюйм/с, которые используют ту же связь JTAG. Такой дюйм/с включает сбор данных FPGA, Intel® SignalTap II или Xilinx® Ядра Logic Analyzer Vivado. Ведущий IP AXI MATLAB может сосуществовать в вашем проекте с другим дюйм/с, которые используют связь JTAG, однако, только одно из этих приложений может использовать кабель JTAG за один раз. Выпустите aximaster возразите, чтобы возвратить ресурс JTAG для использования другими приложениями.

Наиболее распространенное конфликтное использование кабеля JTAG должно повторно программировать FPGA. Остановите любой сбор данных FPGA или MATLAB ведущее устройство AXI связь JTAG, прежде чем можно будет использовать кабель, чтобы программировать FPGA.

Максимальная скорость передачи данных между хостом - компьютером и FPGA ограничивается тактовой частотой JTAG. Для плат Intel тактовая частота JTAG составляет 12 МГц или 24 МГц. Для плат Xilinx тактовая частота JTAG составляет 33 МГц или 66 МГц. Частота JTAG зависит от типа кабеля и максимальной тактовой частоты, поддержанной платой FPGA.