Автоматическая функция верификации интегрирует верификацию как часть рабочего процесса для HDL cosimulation использование HDL Workflow Advisor. Во время этого рабочего процесса, Simulink® генерирует тестовую модель для HDL cosimulation. Эта тестовая модель сравнивает сгенерированный HDL DUT выходные параметры (проникающий через блок HDL Cosimulation) с исходным блоком Simulink выходные параметры. Автоматический шаг верификации автоматически запускает этот испытательный стенд. Этот шаг возвращает информацию о передаче/сбое, зависящую, если выходные параметры HDL DUT совпадают с выходом исходного блока Simulink в испытательном стенде.

Открытый HDL Workflow Advisor для вашей модели.

Шаг 1.1, выберите Generic ASIC/FPGA.

Запустите все шаги под 2, Prepare Model For HDL Code Generation.

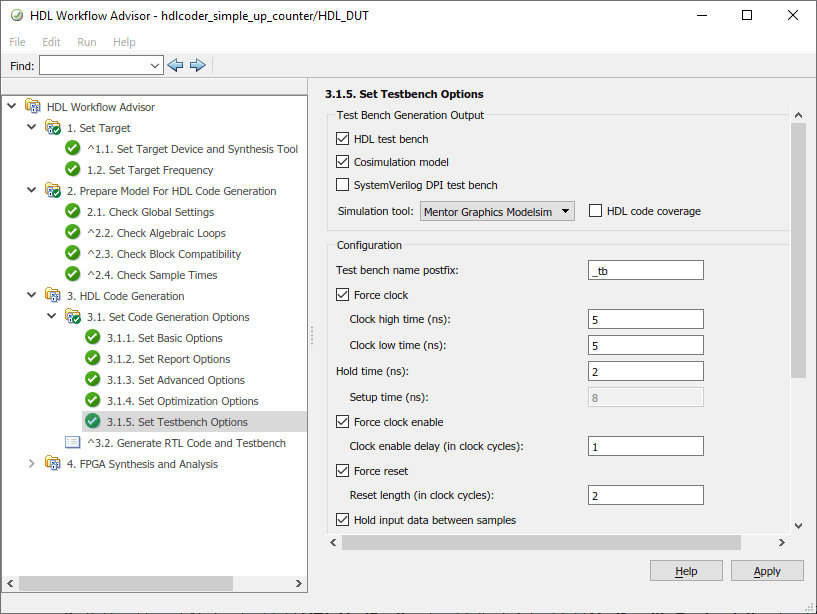

На шаге 3.1.5, Set Testbench Options, выбирают Cosimulation model. Затем установите Simulation tool на любой Mentor Graphics ModelSim или Cadence Incisive для вашего симулятора HDL.

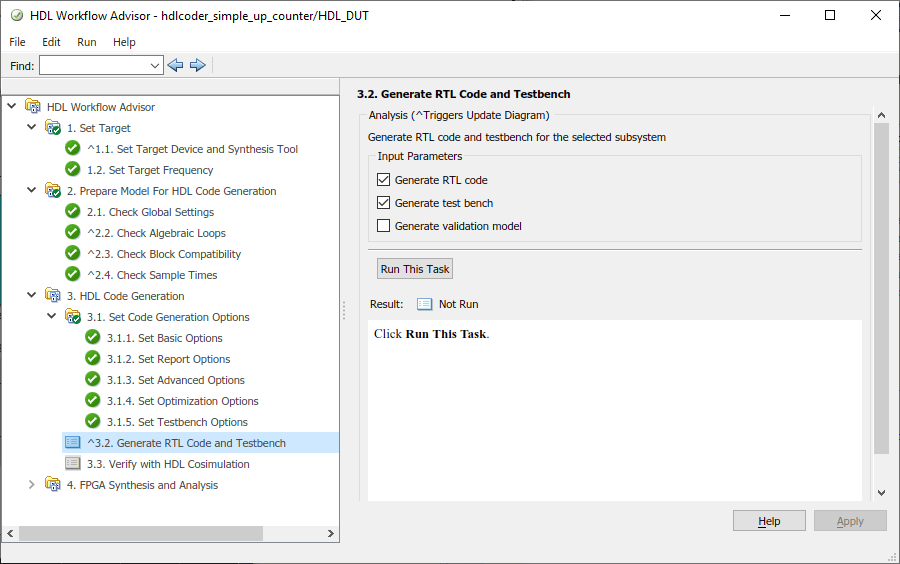

На Шаге 3.2, Generate RTL Code and Testbench, выбирают Generate testbench. Этот выбор заставляет Шаг 3.3 появляться.

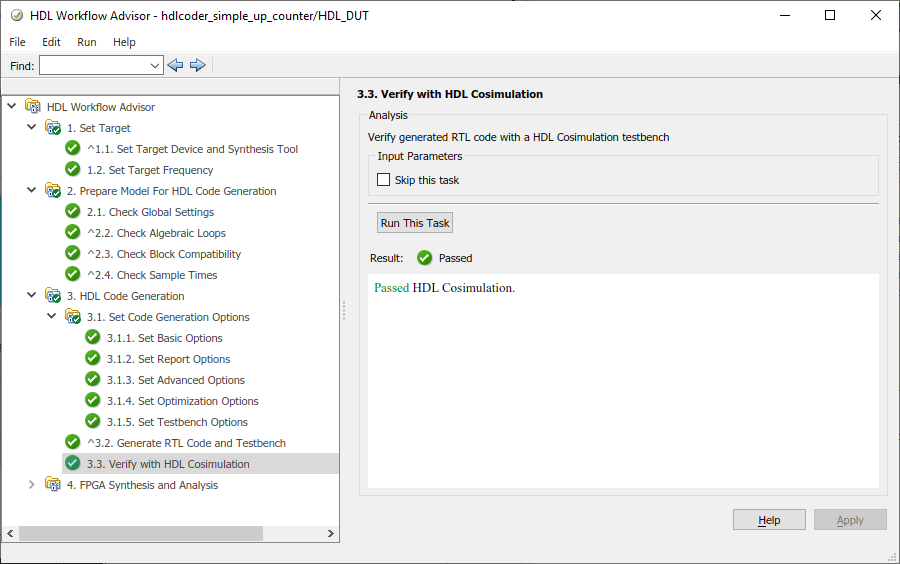

На шаге 3.3 нажмите Run This Task. HDL Workflow Advisor и HDL Verifier™ проверяют сгенерированный HDL с помощью cosimulation между симулятором HDL и испытательным стендом Simulink. Любые соответствующие сообщения о состоянии отображены в окне состояния в HDL Workflow Advisor.