Поведенческая модель интегральной схемы драйвера полумоста

Simscape / Электрический / Semiconductors & Converters

Блок Half-Bridge Driver обеспечивает абстрактное представление интегральной схемы для управления MOSFET и полумостами IGBT. Модели блока вводят гистерезис, задержку распространения и turn-on/turn-off динамику. Если, моделируя схему драйвера логического элемента явным образом, всегда не используйте этот блок или блок Gate Driver, чтобы установить напряжение источника логического элемента на блоке MOSFET или эмиттерное логическим элементом напряжение на блоке IGBT. Не соединяйте управляемый источник напряжения непосредственно с полупроводниковым логическим элементом, потому что это не использует выходной импеданс драйвера логического элемента, который определяет переключающуюся динамику.

Блок Half-Bridge Driver имеет два варианта моделирования, доступные путем щелчка правой кнопкой по блоку по блок-схеме и затем выбирания подходящей опции из контекстного меню, под Simscape> Block choices:

PS input — Состоянием вывода драйвера управляет входной u физического сигнала. Используйте этот вариант, если весь ваш контроллер, включая генерацию сигналов PWM, определяется Simulink® блоки. Этим вариантом моделирования является значение по умолчанию.

Electrical input ports — Состоянием вывода драйвера управляют две электрических входных связи, PWM и REF. Используйте этот вариант, если ваша модель имеет восходящие аналоговые компоненты, такие как источник Controlled PWM Voltage.

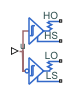

Первая пара выходных электрических портов, HO и HS, ведет себя таким же образом как порты G и S блока Gate Driver. Соедините эти порты с высокой стороной MOSFET или IGBT полумоста. Вторая пара портов, LO и LS, соединяет с низкой стороной MOSFET или IGBT полумоста. Они ведут себя похожим способом, за исключением того, что их логика инвертируется относительно той из высокой стороны.

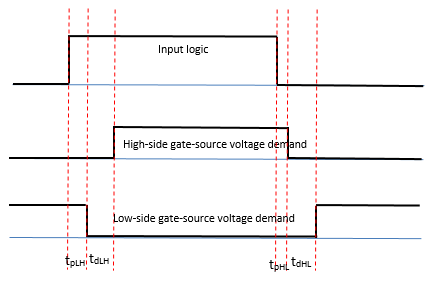

Схема показывает свойства синхронизации для драйвера полумоста, где:

t pLH является задержкой распространения низкой стороны, когда входная логика идет от 0 до 1.

t dLH является потерей времени высокой стороны, когда входная логика идет от 0 до 1.

t pHL является задержкой распространения высокой стороны, когда входная логика идет от 1 до 0.

DHL t является потерей времени низкой стороны, когда входная логика идет от 1 до 0.

Можно вставить отказ в один или оба из выходных параметров в заданном времени симуляции. Опции отказа:

Вход сбоя зафиксирован в логическом 0

Вход сбоя зафиксирован в логической 1

Сбой высокая сторона прочь

Сбой высокая сторона на

Сбой низкая сторона прочь

Сбой низкая сторона на

Приводят высокие и низкие стороны к сбою прочь

Приводят высокие и низкие стороны к сбою на

Controlled PWM Voltage | Gate Driver | N-Channel IGBT | N-Channel MOSFET | P-Channel MOSFET