Поведенческая модель интегральной схемы таймера

Simscape / Электрический / Интегральные схемы

Блок Timer является поведенческой моделью интегральной схемы таймера, такой как NE555.

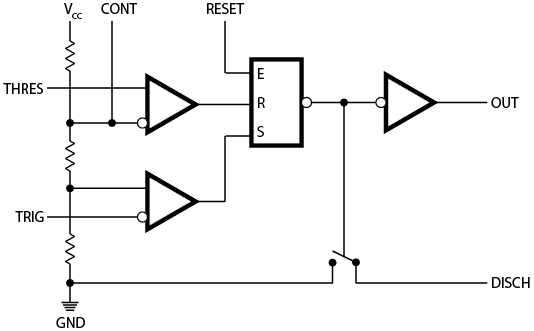

Следующий рисунок показывает структуру реализации.

Наборы параметров Potential divider component resistance значения этих трех резисторов, создающих потенциальный делитель. Два входных параметров компаратора имеют бесконечное входное сопротивление и обнуляют входную емкость. Блок S-R Latch обеспечивает функциональность сброшенного набором фиксатора. Это включает выходной конденсатор и резистор с набором значений, чтобы совпадать со значением параметров Propagation delay. Блок моделирует инвертор выходного каскада с помощью блока CMOS NOT. Вы задаете выходное сопротивление, низкоуровневое выходное напряжение и высокоуровневое выходное напряжение для логического элемента CMOS в диалоговом окне блока Timer. Переключатель выброса аппроксимирует биполярный транзистор NPN на действительном таймере как переключатель с заданным переключателем значения вне сопротивления и на сопротивлении.

Поведение абстрагировано. Результаты не так точны как модель транзисторного уровня.

Задержка в ответ на изменение входных параметров зависит только от постоянной времени RC конденсаторной резистором сети при выходе фиксатора. На практике задержка имеет более комплексную зависимость от структуры устройства. Установите это значение на основе импульсных выходом времен взлета и падения.

Понижение выходного напряжения является линейной функцией текущего выхода. На практике отношение является отношением биполярного транзистора двухтактная пара.

Расположение управляемого переключателя, используемое блоком, является приближением расположения открытого коллектора.

Подключения источника питания внутренне в компоненте и блоке принимают, что контакт GND основывается.