Параллельный интерфейс ссылки обычно является шиной со многими источниками данных и/или местами назначения. Необходимо оценить часы к синхронизации данных для каждой комбинации драйвера и приемника в параллельном интерфейсе. Также необходимо исследовать форму формы волны для каждой такой комбинации. Проблемы, такие как несоответствующая амплитуда, несоответствующая скорость нарастания или вызов могут вызвать ненадежную передачу данных, в то время как проблемы, такие как перерегулирование могут вызвать ранний отказ.

Каждый дизайн интерфейса должен быть оценен и до и после системных плат и до и после Плат ПК, спроектированы. Предварительный анализ топологии требуется, если проект должен иметь шанс работы, и постанализ топологии требуется, чтобы убеждаться, что ничто не было пропущено в процессе Конструкции печатной платы. Конечный результат состоит в том, что обычно существует крупное количество возможностей анализировать. Эти возможности являются составленной комбинацией каждой комбинации драйвера и приемника, каждой фазы интерфейсного протокола, полупроводниковых углов процесса, углов процесса Платы ПК отдельно для каждого слоя каждой Платы ПК, значения пассивного компонента, напряжений источника питания, температуры, и предварительного размещения и постанализа топологии. Отказ оценить каждые без разбора из этих комбинаций увеличивает вероятность, что проблемы будут идентифицированы намного позже в рабочем цикле, когда исправление их будет намного более дорогим.

Приложение Parallel Link Designer автоматизирует выполнение симуляций путем обеспечения графической среды, чтобы настроить симуляции и стандартизованный способ, в котором можно организовать библиотеки модели. Можно отсеять через массу данных, чтобы идентифицировать информацию, которая очень важна для проекта несколькими способами:

Форма волны анализатор оценивает выходные формы волны и идентифицирует любые формы волны, которым не удается удовлетворить предопределенные требования.

Синхронизация анализатор оценивает часы к синхронизации данных и идентифицирует случаи, где часы к данным, синхронизирующим или сбои, чтобы удовлетворить требования или, имеют минимальное поле синхронизации.

Отдельная электронная таблица предоставлена для исследований формы волны и синхронизирующих исследований. Каждая такая электронная таблица организует данные от итоговой информации до деталей отдельных случаев, таким образом делая его практичным, чтобы найти подробную информацию об индивидууме, переставшем работать или крайних случаях.

Средство просмотра формы волны делает удобным исследовать результаты графически. Отдельные панели обеспечиваются для форм волны и табличных результатов. Формы волны могут быть просмотрены или во временном интервале или в частотном диапазоне. Табличные результаты представлены в формате графика рассеивания.

Чтобы автоматизировать процесс симуляции и анализа, приложение Parallel Link Designer организовывает работу в типовой структуре:

Проект — проект является организацией верхнего уровня в приложении Parallel Link Designer. Вся работа, связанная с конкретным продуктом или системой, обычно содержится в проекте. Проект может содержать несколько интерфейсов.

Интерфейс — Интерфейс является сигналами набора, такими как часы, данные или строб раньше реализовывали протокол физического уровня от базового одного IC до ядра другого IC. Интерфейсы в качестве примера: DDR, QDR, RLDRAM, PCIe или XAUI.

Схематический Лист — схематический лист является графическим представлением последовательного канала, полученные элементы использования, такие как указатели, линии электропередачи, s-параметры, vias и т.д. Схематический лист всегда является частью схематического набора.

Схематический Набор — схематический набор является набором схематических листов в интерфейсе. Каждый схематический набор может представлять различную настройку Интерфейса. В приложении Serial Link Designer интерфейс может иметь один или несколько схематических наборов.

Сетевая передача — Каждый тип сигнала в интерфейсе называется сетевой передачей, и состоит из драйверов, приемников, электрических проводников и пассивных компонентов, вовлеченных в передачу того типа сигнала. Может быть несколько экземпляров передачи, сетевой в интерфейсе (пример: линии данных) или мог быть один экземпляр (пример: часы.

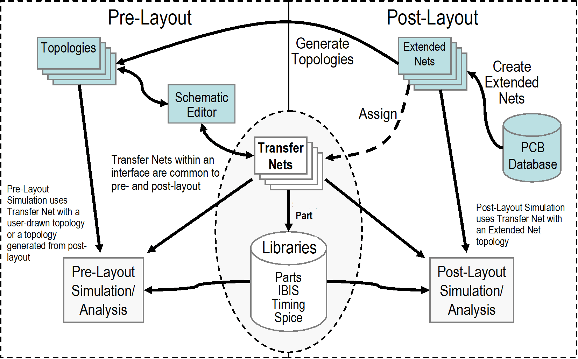

Сети передачи характерны и для предварительного анализа топологии и для верификации постразмещения. В предварительном анализе топологии каждый лист имеет связанную передачу, сетевую с тем же именем как лист. В верификации постразмещения расширенные сети присвоены передать сети.

Пробел решения — Изменения параметров, такие как напряжение, температура или процесс для каждой сетевой передачи организованы в пробел решения.

Указатель — В рамках сетевой передачи, драйверы и приемники упоминается как указатели. Другими словами, указатель является или начальной точкой или конечной точкой для сетевой передачи и является поэтому точкой, где синхронизация анализа должна быть выполнена.

В предварительном анализе топологии каждая сетевая передача описана на отдельном схематическом листе и симулирована в отдельной запущенной симуляции. Значения элемента схемы в передаче, сетевой схематичный, могут быть параметрированы так, чтобы много изменений могли быть оценены, не имея необходимость изменять схематическое. Кроме того, передача, сетевая схематичный, может содержать перекрестные помехи interferers, так, чтобы анализ сетевой передачи мог быть завершен.

Цели предварительного анализа топологии к:

оцените несколько проектных решений, чтобы идентифицировать соответствующие модели I/O, топологию и завершение,

идентифицируйте бюджеты перекрестных помех и сопоставленные штрафы синхронизации,

и задайте правила макета для проекта PCB.

В постанализе топологии каждая сеть на PCB называется сетевым CAD. Сети CAD могут быть объединены с драйверами, приемниками, пакетами, дискретными компонентами и контактами коннектора, чтобы сформировать расширенную сеть. Расширенная сеть содержит указатели и достигает от одного IC до другого. Расширенные сети могут также пересечь несколько PCBs. Приложение Parallel Link Designer обеспечивает удобные механизмы для идентификации расширенных сетей и присвоения их, чтобы передать сети для всех главных потоков PCB.

Цели постанализа топологии к:

подтвердите маршрутизацию PCB,

подтвердите целостность сигнала PCB и поля синхронизации,

и подтвердите поля перекрестных помех.

Одно из преимуществ передачи, которая сетевая концепция - то, что сети передачи могут быть снова использованы без модификации от одной фазы проекта другому, или между проектами. Например, если сети передачи были заданы во время предварительной фазы макета проекта, то те определения могут быть снова использованы без модификации во время постфазы макета. С другой стороны, если сетевая передача была задана в постфазе макета, она может быть снова использована непосредственно в предварительном анализе топологии

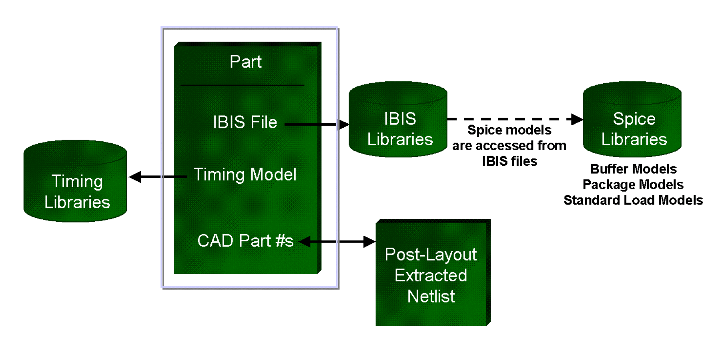

Обычно существует много различных типов данных, сопоставленных с данным компонентом, включая электрические данные, таких как модели HSPICE или IBIS, синхронизируя модели и физические данные, такие как номер детали CAD и схема контактов. Для каждого компонента все эти данные держатся вместе в Части, и каждый указатель в схематическом должен иметь Часть.

Часть имеет уникальный идентификатор и содержит ссылки на файл IBIS, модель синхронизации и номер детали CAD. Файл IBIS, в свою очередь, может содержать:

отображение информации между логическим именем контакта части, физическим ПИН-кодом и вводом-выводом буферизует имя модели,

поведенческие буферные модели ввода-вывода (например, кривые IV/VT),

ссылки на модели HSPICE и усовершенствованные модели пакета,

и уровни обработки формы волны, которые являются MathWorks собственные расширения стандартов IBIS.

Приложение Parallel Link Designer включает 2D полевой решатель, который может использоваться, чтобы создать точные модели линий электропередачи с потерями. Там четко определены места, чтобы поместить библиотеки или для одного проекта или быть общим для много проектов. Те же элементы библиотеки используются в предварительном размещении и постанализе топологии.

Parallel Link Designer | Signal Integrity Viewer