Сгенерируйте и настройте испытательный стенд HDL

Со свойствами испытательного стенда HDL можно включить и настроить генерацию испытательного стенда.

Задайте эти свойства как пары, разделенные запятой аргументов Name,Value к функции generatehdl. Name является именем свойства, и Value является соответствующим значением. Имя должно находиться внутри одинарных кавычек (' '). Вы можете задать несколько аргументов в виде пар имен и значений в любом порядке, например: Name1, Value1, ..., NameN, ValueN.

Например:

fir = dsp.FIRFilter('Structure','Direct form antisymmetric'); generatehdl(fir,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestBench','on','MultifileTestBench','on');

GenerateHDLTestBench — Сгенерируйте испытательный стенд HDL'off' (значение по умолчанию) | 'on'Сгенерируйте испытательный стенд HDL для своего кода фильтра HDL, заданного как 'off' или 'on'. Испытательный стенд применяет сгенерированные входные стимулы для сгенерированного кода фильтра и сравнивает вывод с сохраненными результатами симуляции MATLAB®.

TestBenchName — Имя файла сгенерированного испытательного стендаfiltername_tbИмя файла сгенерированного испытательного стенда, заданного как filtername_tbfiltername является именем сгенерированного модуля сущности или Verilog VHDL. Можно настроить это имя путем установки свойства Name. Кодер добавляет расширение типа файла имени испытательного стенда, как задано свойствами VerilogFileExtension или VHDLFileExtension. Файл испытательного стенда расположен в папке, заданной свойством TargetDirectory.

Если вы задаете значение, которое является зарезервированным словом на выходном языке, кодер добавляет постфиксный _rsvd в это значение. Можно обновить постфиксное значение при помощи свойства ReservedWordPostfix. Для получения дополнительной информации смотрите Решение Конфликтов Зарезервированного слова HDL.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

ErrorMargin — Допуск на погрешность для сравнения испытательного стенда в битах4 (значение по умолчанию) | положительное целое числоДопуск на погрешность для сравнения испытательного стенда в битах, заданных как 4 или положительное целое число. Испытательный стенд сравнивает результаты со ссылочными сигналами. Следующая оптимизация HDL может сгенерировать код испытательного стенда, который приводит к числовым результатам, которые отличаются от результатов, приведенных исходной функцией filter:

Набор FIRAdderStyle к 'tree' или 'pipelined'

AddPipelineRegisters с КИХ, асимметричным КИХ и симметричными КИХ-фильтрами

Допуск на погрешность задает приемлемое минимальное количество битов, которыми могут отличаться числовые результаты, прежде чем испытательный стенд выдает предупреждение.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

MultifileTestBench — Сгенерируйте многофайловый испытательный стенд'off' (значение по умолчанию) | 'on'Сгенерируйте многофайловый испытательный стенд, заданный как 'off' или 'on'. Когда это свойство установлено в 'on', кодер генерирует отдельные файлы для кода испытательного стенда, функций помощника и данных об испытательном стенде вместо одного файла. Имена файлов выведены из свойств TestBenchName и TestBenchDataPostfix. Например, если именем сгенерированного модуля сущности или Verilog VHDL является my_fir_filt, имена файлов испытательного стенда по умолчанию:

my_fir_filt_tb — Код испытательного стенда

my_fir_filt_tb_pkg — Помощник функционирует пакет

my_fir_filt_tb_data — Блок данных тестового вектора

Кодер добавляет к этим именам файлов расширение типа файла, заданное свойствами VerilogFileExtension или VHDLFileExtension.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

TestBenchDataPostfix — Снабдите постфиксом к имени файла данных об испытательном стенде'_data' (значение по умолчанию) | вектор символов | представляет скаляр в виде строкиПостфикс к имени файла данных об испытательном стенде, заданных как '_data', вектор символов или скаляр строки. Кодер генерирует файл данных испытательного стенда с именем файла, полученным путем добавления этого постфикса к значению свойства TestBenchName.

Это свойство применяется только, когда свойства GenerateHDLTestBench и MultifileTestBench установлены в 'on'.

TestBenchReferencePostfix — Снабдите постфиксом к ссылочным именам сигнала'_ref' (значение по умолчанию) | вектор символов | представляет скаляр в виде строкиПостфикс к ссылочным именам сигнала, заданным как '_ref', вектор символов или скаляр строки. Кодер применяет этот постфикс к ссылочному выходному сигналу в испытательном стенде. Кодер представляет ссылочные данные сигнала как массивы.

CONSTANT filter_out_expected : filter_in_data_log_type :=

(

-2.4228738523269194E-03,

-2.0832449820793104E-03,

6.7703446401186345E-03,...SIGNAL filter_out_ref : real := 0.0; -- double ... filter_out_ref <= filter_out_expected(TO_INTEGER(filter_out_addr));

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

ClockHighTime — Период, в который испытательный стенд управляет входными сигналами часов высоко (1) в нс5 (значение по умолчанию) | положительная скалярная величинаПериод, в который испытательный стенд управляет входными сигналами часов высоко (1) в нс, заданном как 5 или положительная скалярная величина. Можно задать целое число или значение с плавающей точкой с двойной точностью, имеющее до 6 значительных цифр после десятичной точки.

Это свойство применяется только, когда свойства GenerateHDLTestBench и ForceClock установлены в 'on'.

ClockLowTime — Период, в который испытательный стенд управляет входными сигналами часов низко (0) в нс5 (значение по умолчанию) | положительная скалярная величинаПериод, в который испытательный стенд управляет входными сигналами часов низко (0) в нс, заданном как 5 или положительная скалярная величина. Можно задать целое число или значение с плавающей точкой с двойной точностью, имеющее до 6 значительных цифр после десятичной точки.

Это свойство применяется только, когда свойства GenerateHDLTestBench и ForceClock установлены в 'on'.

ForceClock — Испытательный стенд обеспечивает входные сигналы часов'on' (значение по умолчанию) | 'off'Испытательный стенд обеспечивает входные сигналы часов, заданные как одно из следующего:

'on' — Испытательный стенд обеспечивает входные сигналы часов. Значения свойств ClockHighTime и ClockLowTime управляют формой волны часов.

'off' Необходимо управлять входными сигналами часов из внешнего источника.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

ForceClockEnable — Часы сил испытательного стенда включают входные сигналы'on' (значение по умолчанию) | 'off'Часы сил испытательного стенда включают входные сигналы, заданные как одно из следующего:

'on' — Силы испытательного стенда часы включают входные сигналы. Полярность активна высокий (1). Этот сигнал также повинуется установке свойства HoldTime.

'off' Необходимо управлять часами, включают входные сигналы из внешнего источника.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

TestBenchClockEnableDelay — Такты между deassertion сброса и утверждением часов включают1 (значение по умолчанию) | положительное целое числоТакты между deassertion сброса и утверждением часов включают, заданный как 1 или положительное целое число. Испытательный стенд ожидает это количество циклов между deasserting сигнал сброса и утверждением, что часы включают сигнал. Свойство HoldTime также применяется.

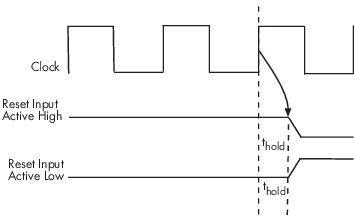

В фигуре испытательный стенд deasserts возбуждаемый высоким уровнем сигнала сигнал сброса после того, как интервал маркировал Hold Time. Испытательный стенд затем утверждает, что часы включают после дальнейшего интервала, маркировал Clock enable delay.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

ForceReset — Испытательный стенд обеспечивает входные сигналы сброса'on' (значение по умолчанию) | 'off'Испытательный стенд обеспечивает входные сигналы сброса, заданные как одно из следующего:

'on' — Испытательный стенд обеспечивает входные сигналы сброса. Можно также задать время задержки, чтобы управлять синхронизацией сброса путем установки свойства HoldTime.

'off' Необходимо управлять входными сигналами сброса из внешнего источника.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

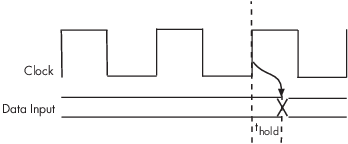

HoldTime — Время задержки для значений входных данных и обеспеченного сброса сигнализирует в нс2 (значение по умолчанию) | положительная скалярная величинаВремя задержки для значений входных данных и обеспеченного сброса сигнализирует в нс, заданном как 2 или положительная скалярная величина. Испытательный стенд содержит сигналы ввода данных фильтра и обеспеченные входные сигналы сброса для интервала требуемого времени мимо возрастающего фронта синхроимпульса. Можно задать целое число или значение с плавающей точкой с двойной точностью, имеющее до 6 значительных цифр после десятичной точки.

Следующие данные показывают приложение времени задержки, thold, для сигналов ввода данных и сброса. Сигналы обеспечены к активному, высокому и активному низко. Свойство ResetLength установлено в 2 цикла, и испытательный стенд утверждает сигнал сброса для в общей сложности 2 циклов плюс thold.

Время задержки для входных сигналов сброса

Время задержки для сигналов ввода данных

Это свойство применяется только, когда свойства GenerateHDLTestBench и ForceReset установлены в 'on'.

ResetLength — Количество тактов, что испытательный стенд утверждает сигнал сброса2 (значение по умолчанию) | положительное целое числоКоличество тактов, что испытательный стенд утверждает сигнал сброса, заданный как 2 или положительное целое число.

Испытательный стенд по умолчанию утверждает возбуждаемый высоким уровнем сигнала сигнал сброса для 2 тактов.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

HoldInputDataBetweenSamples — Испытательный стенд содержит входные данные разогнанных, просачивается допустимое состояние'off' (значение по умолчанию) | 'on'Испытательный стенд содержит входные данные разогнанных, просачивается допустимое состояние, заданное как 'off' или 'on'. Последовательная архитектура и распределенная арифметическая архитектура реализуют внутренние тактовые частоты выше, чем входной уровень. В таких реализациях фильтра основные часы запускают циклы N (N >= 2) для каждой входной выборки. Это свойство относится к количеству тактов, что испытательный стенд содержит входные данные в допустимом состоянии.

'off' Испытательный стенд содержит значения данных в допустимом состоянии для одного такта. Для следующих циклов N-1 данные находятся в неизвестном состоянии (выражены как 'X'). Принуждение входных данных к неизвестному состоянию проверяет что сгенерированные кодовые регистры фильтра входные данные только на первом цикле.

'on' — Испытательный стенд содержит значения входных данных в допустимом состоянии через такты N.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

InitializeTestBenchInputs — Инициализируйте вход испытательного стенда'off' (значение по умолчанию) | 'on'Инициализируйте вход испытательного стенда, заданный как одно из следующего:

'off' В начале симуляции испытательный стенд управляет неизвестным состоянием (выраженный как 'X') к входным портам.

'on' — В начале симуляции испытательный стенд управляет нулями к входным портам.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

TestBenchStimulus — Входные стимулы применились к сгенерированному фильтру{'impulse','step','ramp','chirp','noise'} (значение по умолчанию) | массив ячеек из символьных векторов | массив строкВходные стимулы применились к сгенерированному фильтру, заданному как {'impulse','step','ramp','chirp','noise'}, массив ячеек из символьных векторов или массив строк. Массив ячеек или массив строк должны быть подмножеством набора по умолчанию стимулов. Можно задать комбинации стимулов в любом порядке. Например:

generatehdl(filt,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestbench','on', ... 'TestBenchStimulus',{'ramp','impulse','noise'})

TestBenchUserStimulus. Когда TestBenchUserStimulus является непустым вектором, он берет приоритет над TestBenchStimulus.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

TestBenchUserStimulus — Custom[] (пустой вектор) (значение по умолчанию) | вектор входных данныхПользовательский входной стимул, заданный как одно из следующего:

[] (пустой вектор) — Испытательный стенд использует свойство TestBenchStimulus сгенерировать входные данные.

Вектор входных данных — испытательный стенд применяет этот входной стимул для сгенерированного фильтра. Можно задать вектор как вызов функции, возвращающий вектор.

Например, этот вызов функции генерирует прямоугольную волну с демонстрационной частотой 8 бит в секунду (Фс/8).

repmat([1 1 1 1 0 0 0 0],1,10)

generatehdl.generatehdl(filt,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestbench','on', ... 'TestBenchUserStimulus',repmat([1 1 1 1 0 0 0 0],1,10))

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

TestBenchCoeffStimulus — Содействующий стимул для КИХ или БИХ-фильтров[] (пустой вектор) (значение по умолчанию) | вектор коэффициентов (КИХ фильтрует только), | массив ячеек коэффициента и значений шкалы (БИХ фильтрует только),Содействующий стимул для КИХ или БИХ-фильтров, заданных как одно из следующего:

[] (пустой вектор) — Испытательный стенд использует коэффициенты объекта фильтра и обеспечивает входные стимулы. Эта последовательность показывает ответ на входные стимулы и проверяет, что интерфейс пишет один набор коэффициентов в содействующую память как ожидалось.

Вектор коэффициентов (КИХ фильтрует только) — фильтр обрабатывает входные стимулы дважды: однажды с коэффициентами объекта фильтра и однажды с содействующим стимулом. Испытательный стенд проверяет, что интерфейс пишет два различных набора коэффициентов в содействующую память. Для получения дополнительной информации смотрите Генерацию Испытательного стенда для Программируемых КИХ-Коэффициентов.

Массив ячеек коэффициента и значений шкалы (БИХ фильтрует только) — Задает стимул как вектор-столбец значений шкалы и матрицы раздела второго порядка (SOS). Фильтр обрабатывает входные стимулы дважды: однажды с коэффициентами объекта фильтра и однажды с содействующим стимулом. Испытательный стенд проверяет, что интерфейс пишет два различных набора коэффициентов в содействующую память. Для получения дополнительной информации смотрите Генерацию Испытательного стенда для Программируемых БИХ-Коэффициентов.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on', и свойство CoefficientSource установлено в 'ProcessorInterface'.

TestBenchFracDelayStimulus — Дробный стимул задержки для односкоростных фильтров Фэрроу'RandSweep' | 'RampSweep'Дробный стимул задержки для односкоростных фильтров Фэрроу, заданных как одно из следующего:

Постоянное числовое значение — испытательный стенд управляет дробным входным сигналом задержки с постоянным значением, полученным из объекта фильтра.

Вектор числовых значений — испытательный стенд управляет дробным входным сигналом задержки от этого вектора. Можно задать вектор как вызов функции, возвращающий вектор. Вектор должен иметь ту же длину как входной сигнал испытательного стенда.

'RandSweep' — Испытательный стенд управляет дробным входным сигналом задержки при помощи вектора значений, инкрементно увеличивающихся по диапазону от 0 до 1. Этот сигнал стимула имеет ту же длительность как входной сигнал к фильтру, но изменяется на более медленном уровне. Каждое дробное значение задержки, полученное из вектора, сохранено на 10% общего времени входного сигнала.

'RampSweep' — Испытательный стенд управляет дробным входным сигналом задержки при помощи вектора случайных значений от 0 до 1. Этот сигнал стимула имеет ту же длительность как входной сигнал к фильтру, но это изменяется на более медленном уровне. Каждое дробное значение задержки, полученное из вектора, сохранено на 10% общего времени входного сигнала.

Смотрите свойства генерации кода для неоплодотворенных фильтров.

Это свойство применяется только, когда свойство GenerateHDLTestBench установлено в 'on'.

TestBenchRateStimulus — Rate для CIC-фильтровУровень ввел стимул для фильтров Каскадной расчески интегратора (CIC), заданных как максимальный фактор изменения уровня или целое число. Если вы не задаете TestBenchRateStimulus, кодер принимает, что фильтр разработан с максимальным ожидаемым уровнем. Фактор десятикратного уменьшения (для CIC decimators) или коэффициент интерполяции (для интерполяторов CIC) установлен в этот максимальный фактор изменения уровня.

Смотрите CIC-фильтры с плавающей ставкой.

Это свойство применяется только к CIC-фильтрам с плавающей ставкой, когда свойства GenerateHDLTestBench и AddRatePort установлены в 'on'.

GenerateCosimBlock — Generate Simulink® HDL блоки Cosimulation'off' (значение по умолчанию) | 'on'Сгенерируйте модель Simulink HDL блоки Cosimulation, заданные как 'off' или 'on'. Сгенерированная модель Simulink содержит два HDL блоки Cosimulation: один для Mentor Graphics® ModelSim® и один для Cadence Incisive®. Кодер конфигурирует эти блоки, чтобы соответствовать порту и интерфейсу типа данных выбранного фильтра. Используйте эти блоки для cosimulate ваш проект с желаемым симулятором HDL в Simulink.

Эта функция требует лицензии HDL Verifier™.

GenerateCosimModel — Generate Simulink реализованного фильтра и блока HDL Cosimulation'none' (значение по умолчанию) | 'ModelSim' | 'Incisive'Сгенерируйте модель Simulink реализованного фильтра и блока HDL Cosimulation, заданного как 'none', 'ModelSim' или 'Incisive'. Когда вы устанавливаете это свойство на 'ModelSim' или 'Incisive', кодер генерирует и открывает модель Simulink. Модель содержит HDL cosimulation блок для выбранного средства моделирования и поведенческая реализация проекта фильтра. Модель применяет сгенерированные входные стимулы и сравнивает вывод средства моделирования EDA с выводом поведенческой подсистемы фильтра. Можно настроить входной стимул и допуск на погрешность с помощью тех же свойств, как вы были бы для сгенерированного испытательного стенда HDL.

Смотрите генерацию модели Simulink для Cosimulation с симулятором HDL.

Эта функция требует лицензии HDL Verifier.

Если вы используете функциональный fdhdltool, чтобы сгенерировать HDL-код, можно установить соответствующие свойства на вкладке Test Bench в диалоговом окне Generate HDL.

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.