Двухпортовый RAM, который поддерживает два уровня

HDL Coder / Операции HDL

Блок Dual Rate Dual Port RAM моделирует RAM, который поддерживает одновременные операции чтения и операции записи к различным адресам на двух тактовых частотах. Порт RAM может достигнуть одного уровня, и порт B может запуститься на различном уровне.

В высокоэффективных аппаратных приложениях можно использовать этот блок, чтобы получить доступ к RAM дважды на такт. Если вы генерируете HDL-код, это блок-диаграммы к двойному тактовому двухпортовому RAM в большей части FPGAs.

Можно получить доступ к различным адресам от портов A и B одновременно. Можно также считать тот же адрес из портов A и B одновременно.

Однако не получайте доступ к адресу от одного порта RAM, в то время как он пишется из другого порта RAM. Во время симуляции, если вы получаете доступ к адресу от одного порта RAM в то же время, что и вы пишете, что адрес от другого порта RAM, программное обеспечение сообщает об ошибке.

RAM имеет запись первое поведение. То, когда вы пишете в RAM, новые записывают данные, сразу доступно в выходном порту.

Для результатов симуляции, которые совпадают со сгенерированным HDL-кодом в панели Решателя диалогового окна Configuration Parameters, снимают флажок для Treat each discrete rate as a separate task. Когда флажок снимается, однозадачный режим включен.

Если вы моделируете этот блок с выбранным Treat each discrete rate as a separate task, многозадачный режим включен. Выходные данные могут обновить в том же цикле, но в сгенерированном HDL-коде, выходные данные обновляются один цикл позже.

Ширина адресного бита. Минимальная битная ширина равняется 2, и максимальная битная ширина равняется 28. Значение по умолчанию равняется 8.

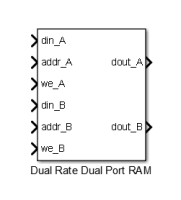

Блок имеет следующие порты:

din_AЗапишите данные вход для порта RAM A. Данные могут быть любой шириной. Это наследовало ширину и тип данных от входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

addr_AЗапишите адрес для порта RAM A.

Тип данных: скалярное беззнаковое целое (uintN) или фиксированная точка без знака (ufixN) с дробной длиной 0

we_AРазрешите запись для порта RAM A. Установите we_A на true для операции записи или false для операции чтения.

Тип данных: булевская переменная

din_BЗапишите данные вход для порта RAM B. Данные могут иметь любую ширину и наследовали ширину и тип данных от входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

addr_BЗапишите адрес для порта RAM B.

Тип данных: скалярное беззнаковое целое (uintN) или фиксированная точка без знака (ufixN) с дробной длиной 0

we_BРазрешите запись для порта RAM B. Установите we_B на true для операции записи или false для операции чтения.

Тип данных: булевская переменная

dout_AВыходные данные от порта RAM адрес, addr_A.

dout_BВыходные данные от порта RAM B адрес, addr_B.

Двухпортовый RAM | FIFO HDL | Простой двухпортовый RAM | Один порт RAM