Последовательность хранилищ входных выборок в методе "первым пришел - первым вышел" (FIFO) регистр

HDL Coder / Операции HDL

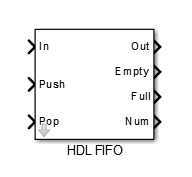

Блок HDL FIFO хранит последовательность входных выборок в методе "первым пришел - первым вышел" (FIFO) регистр.

Для результатов симуляции, которые совпадают со сгенерированным HDL-кодом в панели Решателя диалогового окна Configuration Parameters, снимают флажок для Treat each discrete rate as a separate task. Когда флажок снимается, однозадачный режим включен.

Если вы моделируете этот блок с выбранным Treat each discrete rate as a separate task, многозадачный режим включен. Выходные данные могут обновить в том же цикле, но в сгенерированном HDL-коде, выходные данные обновляются один цикл позже.

Задайте количество записей, которые может содержать регистр FIFO. Минимум равняется 4. Значение по умолчанию равняется 10.

Входные параметры (In, Push) и выходные параметры (Out, Pop) могут запуститься в различных шагах расчета. Введите отношение выходного шага расчета, чтобы ввести шаг расчета. Используйте положительное целое число или 1/N, где N является положительным целым числом. Значение по умолчанию равняется 1.

Например:

Если вы вводите 2, выходной шаг расчета является дважды входным шагом расчета, означая выходные параметры, запущенные медленнее.

Если вы вводите 1/2, выходной шаг расчета является половиной входного шага расчета, означая выходные параметры, запущенные быстрее.

Full, Empty и сигналы Num, запущенные на более быстром уровне.

Ответ (Ignore, Error или Warning) к триггеру, полученному в порте Push, когда регистр полон. Значением по умолчанию является Warning.

Ответ (Ignore, Error или Warning) к триггеру, полученному в порте Pop, когда регистр пуст. Значением по умолчанию является Warning.

Включите Пустой выходной порт, который является высок (1), когда регистр FIFO пуст и низкий (0) в противном случае.

Включите Полный выходной порт, который является высок (1), когда регистр FIFO полон и низкий (0) в противном случае.

Включите Цифровой выходной порт, который отслеживает количество записей в настоящее время в очереди.

Блок имеет следующие порты:

InСигнал ввода данных.

PushУправляющий сигнал. Когда этот порт получает значение 1, блок продвигает вход в порте In на конец регистра FIFO.

PopУправляющий сигнал. Когда этот порт получает значение 1, блок появляется, первый элемент от FIFO указывают, и содержит порт Out в том значении.

OutСигнал вывода данных.

EmptyБлок утверждает этот сигнал, когда регистр FIFO пуст. Этот порт является дополнительным.

FullБлок утверждает этот сигнал, когда регистр FIFO полон. Этот порт является дополнительным.

NumТекущее количество значений данных в регистре FIFO. Этот порт является дополнительным.

Если два или больше из входных портов управления инициированы в том же временном шаге, операции выполняются в следующем порядке:

Поп

Продвинуть