Этот пример обрисовывает в общих чертах шаги, чтобы создать аппаратные и программные исполняемые файлы для вашей модели и выполнить ваше приложение. Ваша модель SoC может содержать модель процессора, модель FPGA или обоих.

Чтобы сгенерировать двоичные файлы SoC, необходимо включать путь к Vivado® или исполняемым файлам Quartus® в системном пути. Если исполняемые файлы уже не находятся в вашем системном пути, используйте функцию hdlsetuptoolpath, чтобы добавить их в ваш путь.

В окне модели выберите Tools> SoC Builder. Поддерживаемая плата должна быть задана в параметрах конфигурации в панели Hardware Implementation.

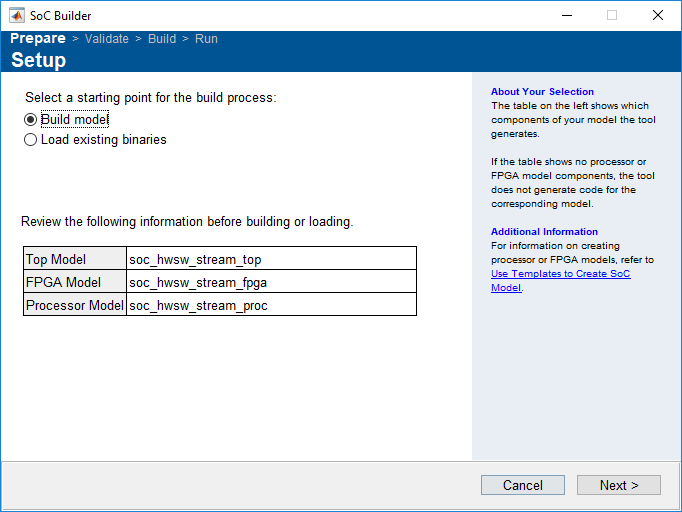

Подготовьте свою модель путем выбора отправной точки для процесса сборки, и затем рассмотрите информацию модели.

Во-первых, задайте отправную точку для процесса сборки. Если вы создаете модель, которую вы не создали прежде, выберите Build model. Если вы ранее завершили процесс сборки и сохранили двоичные файлы в папке, выберите Load existing binaries.

Разработчик SoC анализирует модель и отображает топ-модель, модель FPGA (если вы существуете), и модель ARM (если вы существуете). Рассмотрите эту информацию для точности. Если это кажется неправильным, пересмотрите модель, сохраните и перезапустите инструмент SoC Builder.

Если ваша модель FPGA установлена в основанный на кадре вариант модели Simulink®, то SoC Builder не отображает модель в таблице. Чтобы сделать его видимым в таблице, установите образцовый вариант на основанный на выборке и перекомпилируйте ваш проект.

Нажмите Next.

Следующая страница SoC Builder предоставляет информацию о карте распределения памяти модели. Чтобы открыть Memory Mapper, нажмите View/Edit. Рассмотрите базовые адреса и смещения, и отредактируйте их в случае необходимости.

Этот шаг карты распределения памяти SoC Builder видим, только если у вас есть модель FPGA в вашей топ-модели. Если ваша модель FPGA установлена в основанное на кадре моделирование - затем, никакая модель FPGA не видима, и поэтому нет никакого доступа к инструменту Memory Mapper.

Нажмите Next.

Задайте путь к папке проекта путем ввода пути в текстовое поле Project Folder или путем просмотра к местоположению папки. Разработчик SoC помещает все сгенерированные файлы, включая отчеты, исполняемые файлы и поток битов, в этой заданной папке.

Если вы выбрали Load existing binaries как отправную точку для процесса сборки, задайте местоположение папки проекта предыдущих двоичных файлов и отчетов.

Нажмите Next.

В разделе Select Build Action выберите одну из этих опций:

Build, load and run – Выберите эту опцию, чтобы сгенерировать HDL и код С, исполняемые файлы программного обеспечения сборки и файл программирования FPGA из вашей модели. После создания SoC Builder загружает сгенерированный код к плате FPGA и выполняет приложение.

Build only – Выберите эту опцию, чтобы сгенерировать HDL и код С, исполняемые файлы программного обеспечения сборки и файл программирования FPGA из вашей модели. SoC Builder сохраняет сгенерированные двоичные файлы в папке, и можно продолжить выполнение позже.

Build and load for external mode – Выберите эту опцию, чтобы создать проект и запустить его в режиме external mode. Режим external mode позволяет настройкам параметров на FPGA, не имея необходимость восстанавливать проект FPGA. Это также позволяет регистрировать данные от FPGA и отобразить его на хосте. Для получения дополнительной информации о режиме external mode, см. Модели Мелодии и Монитора, Работающие на Целевом компьютере (Simulink).

Проверяйте модель по выбранной плате и сгенерируйте отчет. Проверяйте отчет гарантировать, что проект сгенерирован как ожидалось.

SoC Builder называет отчет <project-folder>/html/modelname_system_report.html

Чтобы сгенерировать поток битов для вашего проекта FPGA и скомпилированный исполняемый файл для вашего программного обеспечения, нажмите Build.

Нажатие на Build открывает внешний интерпретатор и запускает сторонние программы для синтеза и реализации проекта. Время генерации зависит от сложности вашей модели и вашего хоста - компьютера. Если генерация завершена, поток битов сгенерирован с вашим именем модели. SoC Builder генерирует скрипт испытательного стенда JTAG, если вы выбрали опцию Include MATLAB as AXI Master в параметрах конфигурации. Скрипт показывает, как создать MATLAB как Ведущее устройство AXI и сконфигурировать ваш проект FPGA по JTAG. Можно настроить скрипт, чтобы создать собственный испытательный стенд. Для получения дополнительной информации о MATLAB как Ведущее устройство AXI, см. документацию пакета поддержки: SoC Blockset Поддерживаемые аппаратные средства.

Рассмотрите адрес IPv4, Номер порта SSH и учетные данные входа в систему. Отредактируйте любое из этих значений при необходимости. Этот шаг очень важен, если у вас есть больше чем одна плата, соединенная с хостом - компьютером, так, чтобы SoC Builder мог идентифицировать связь правильного порта. Проверьте, что отображенный IP-адрес совпадает с IP-адресом для платы, которую вы намереваетесь использовать.

Проверьте, что плата соединяется с хостом с кабелем Ethernet, и затем нажмите Test Connection, чтобы протестировать физическое соединение к плате.

Этот шаг в SoC Builder видим, только если ваша топ-модель включает модель процессора.

Проверьте, что ваша плата соединяется с хостом - компьютером.

Если модель процессора присутствует в вашей топ-модели, подключении к плате с кабелем Ethernet.

Если топ-модель включает модель FPGA, но никакую модель процессора, подключение к плате с кабелем JTAG.

Нажмите Load and Run. Это действие загружает сгенерированный поток битов к FPGA, программирует процессор и запускает приложение.

Если вы выбрали Tune parameters and monitor signals in external mode на шаге 5, это действие загружает поток битов к FPGA и открывает модель в режиме external mode. В этом случае можно теперь выбрать сигналы для журналирования и контроля или изменить настраиваемые параметры.

Если ваша топ-модель включает модель FPGA, но никакая модель процессора, кнопка показывает Load.