Обнаружьте ошибки во входных данных с помощью CRC, оптимизированного для генерации HDL-кода

Communications Toolbox> Исправление ошибок и Обнаружение> CRC (commcrc2)

Поддержка HDL Communications Toolbox> Исправление ошибок и Обнаружение> CRC (commhdlcrc)

Этот благоприятный для оборудования блок детектора CRC выполняет контроль циклическим избыточным кодом (CRC) на данных и сравнивает получившуюся контрольную сумму с добавленной контрольной суммой. Если эти две контрольных суммы не соответствуют, блок сообщает об ошибке. Вместо того, чтобы обработать целый кадр целиком, блок принимает и возвращает демонстрационный поток данных с сопроводительными управляющими сигналами. Управляющие сигналы указывают на валидность выборок и контуры системы координат. Чтобы достигнуть более высокой пропускной способности, блок принимает векторные данные до продолжительности CRC и реализует параллельную архитектуру.

| Порт | Направление | Описание | Тип данных |

|---|---|---|---|

dataIn | Входной параметр | Передайте данные плюс контрольная сумма. Данные могут быть вектором двоичных значений или скалярным целым числом, представляющим несколько битов. Например, векторный вход [0 0 0 1 0 0 1 1] эквивалентен входу uint8 19. Ширина данных должна быть меньше чем или равна продолжительности CRC, и продолжительность CRC должна быть делимой по условию ширина. Например, для CRC-CCITT/CRC-16, допустимые ширины данных равняются 16, 8, 4, 2, и 1. | Вектор: дважды или булевская переменная Скаляр: беззнаковое целое (uint8/16/32) или fixdt (0, N, 0) |

startIn | Входной параметр | Указывает на запуск системы координат данных, включая контрольную сумму. | Булевская переменная |

endIn | Входной параметр | Указывает на конец системы координат данных. | Булевская переменная |

validIn | Входной параметр | Указывает, что входные данные допустимы. | Булевская переменная |

dataOut | Вывод | Передайте данные. Выходные данные имеют ту же ширину как входные данные. | То же самое как dataIn |

startOut | Вывод | Указывает на запуск системы координат данных. | Булевская переменная |

endOut | Вывод | Указывает на конец системы координат данных. | Булевская переменная |

validOut | Вывод | Указывает, что выходные данные допустимы. | Булевская переменная |

err | Вывод | Указывает на повреждение полученных данных, когда err высок (1). | Булевская переменная |

Двойной или булев вектор, задающий полином, в порядке убывания степеней. Продолжительность CRC является длиной (полином) – 1. Значением по умолчанию является [1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1].

Двойной или булев скаляр или вектор длины равняются продолжительности CRC, задавая начальное состояние внутреннего сдвигового регистра. Значение по умолчанию 0.

Когда этот параметр выбран, блок использует прямой алгоритм в вычислениях контрольной суммы CRC.

Когда этот параметр не выбран, блок использует непрямой алгоритм в вычислениях контрольной суммы CRC.

Параметр очищен по умолчанию.

Чтобы узнать о прямых и непрямых алгоритмах, см. Коды Контроля циклическим избыточным кодом.

Ширина входных данных должна быть кратной 8.

Когда этот параметр выбран, каждый входной байт инвертируется прежде, чем ввести сдвиговый регистр.

Когда этот параметр не выбран, данные о сообщении передаются неизменному сдвиговому регистру.

Параметр очищен по умолчанию.

Продолжительность CRC должна быть кратной 8.

Когда этот параметр выбран, каждый байт контрольной суммы инвертируется, прежде чем это будет передано итоговому этапу XOR.

Когда этот параметр не выбран, байт контрольной суммы передается итоговому неизменному этапу XOR.

Параметр очищен по умолчанию.

Значение, что контрольная сумма CRC является XORed с тем, прежде чем это будет добавлено к входным данным. Этот параметр может быть двойным или булевым скаляром или вектором длины, равной продолжительности CRC. Значение по умолчанию 0.

Когда вы используете векторный или целочисленный вход, блок реализует параллельный алгоритм CRC [1].

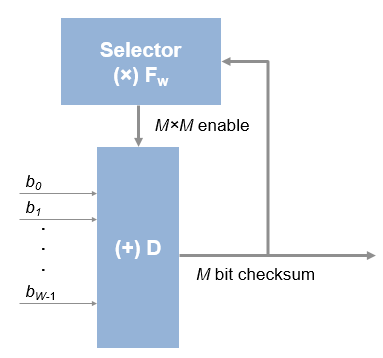

Чтобы обеспечить высокую пропускную способность для современных систем связи, алгоритм CRC реализован с параллельной архитектурой. Эта архитектура рекурсивно вычисляет биты M контрольной суммы CRC для каждого входа W биты. В конце системы координат итоговый результат контрольной суммы добавлен к сообщению. Для полиномиальной длины M рекурсивное вычисление контрольной суммы для битов W параллельно:

FW является M-by-M матрица, которая выбирает элементы текущего состояния для полиномиального вычисления с новыми входными битами. D является M - демонстрационный вектор, который обеспечивает новые входные биты, упорядоченный относительно полинома и дополненный обнуляет. (×) реализован с логическим AND, и (+) реализован с логическим XOR.

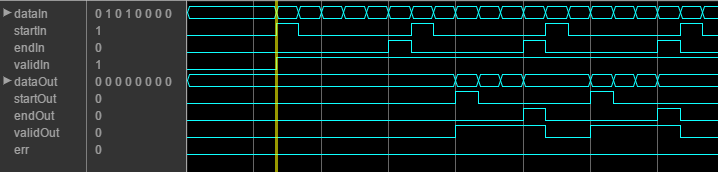

Эта форма волны показывает данные о потоковой передаче и сопроводительные управляющие сигналы для CRC16 с 8-битным бинарным векторным входом. Входные кадры непрерывны, и выходные системы координат показывают пробел между ними, потому что блок детектора удаляет слово контрольной суммы.

Эта схема формы волны показывает непрерывные входные данные. Нетекущие данные также поддержаны.

Блок General CRC Syndrome Detector HDL Optimized вводит задержку на выходе. Эта задержка может быть вычислена следующим уравнением, предположением, что входные данные непрерывны:

initialdelay = 3 * (CRC length/input data width) + 2

[1] Кампобелло, Джузеппе, Джузеппе Патане и Марко Руссо. "Параллельная Реализация CRC". Транзакции IEEE на Компьютерах. Издание 52, № 10, октябрь 2003, стр 1312–1319.