Вектор карты целых чисел к вектору битов

Служебные блоки

Целое число к Битным блок-диаграммам Конвертера каждое целое число (или значение фиксированной точки) во входном векторе группе битов в выходном векторе.

Блок-диаграммы каждое целочисленное значение (или сохраненное целое число, когда вы используете вход фиксированной точки) группе битов M, с помощью выбора в Output bit order, чтобы определить старший значащий бит. Получившаяся длина выходного вектора является временами M длина входного вектора.

Когда вы устанавливаете параметр Number of bits per integer на M и Treat input values as к Unsigned, затем входные значения должны быть между 0 и 2M-1. Когда вы устанавливаете Number of bits per integer на M и Treat input values as к Signed, затем входные значения должны быть между –2M-1 и 2M-1-1. В процессе моделирования блок выполняет проверку на этапе выполнения и выдает ошибку, если какое-либо входное значение за пределами соответствующей области значений. Когда блок генерирует код, он не выполняет эту проверку на этапе выполнения.

Этот блок является односкоростным и одноканальным. Это принимает длину вектор-столбец N или со скалярным знаком (N = 1) входной сигнал и выводит длину N · вектор-столбец M.

Блок может принять типы данных int8uint8int16uint16int32uint32единственный'double', и fixed point.

Количество битов использование блока, чтобы представлять каждое целое число входа. Этот параметр должен быть целым числом между 1 и 32.

Укажите, должны ли входные диапазоны целочисленного значения быть обработаны, как подписано или без знака. Настройкой по умолчанию является Unsigned.

Задайте, является ли первый бит выходного сигнала старшим значащим битом (MSB) или младшим значащим битом (LSB). Выбором по умолчанию является MSB first.

Можно выбрать следующие опции Output data type:

Inherit via internal rule

Smallest integer

Same as input

double

single

uint8

uint16

uint32

Выбором по умолчанию для этого параметра является Inherit via internal rule.

Когда параметр устанавливается на Inherit via internal rule, блок определяет тип выходных данных на основе типа входных данных.

Если входной сигнал с плавающей точкой (любой single или double), тип выходных данных совпадает с типом входных данных.

Если тип входных данных не с плавающей точкой, тип выходных данных определяется, как будто параметр устанавливается на Smallest integer.

Когда параметр устанавливается на Smallest integer, блок выбирает тип выходных данных на основе настроек, используемых в Панели Аппаратной реализации (Simulink) диалогового окна Configuration Parameters.

Если вы выбираете ASIC/FPGA, тип выходных данных является идеальным однобитным размером; ufix1.

Для всех других выборов тип выходных данных является беззнаковым целым с самым маленьким доступным размером слова, как задано в настройках Hardware Implementation (например, uint8)

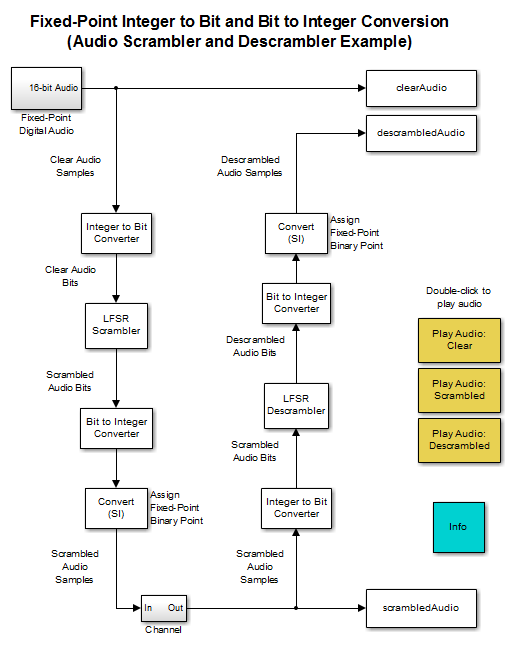

Этот пример иллюстрирует, как использовать Бит для Целого числа и Целого числа с Битными блоками Конвертера с сигналами фиксированной точки.

Этот пример использует упрощенную аудио настройку скремблера и 16-битный источник цифрового аудио фиксированной точки, который является записанной речью. Левая сторона модели представляет аудио подсистему скремблера, и правая сторона представляет подсистему дескремблера.

Можно открыть модель путем ввода doc_audioscrambler в командной строке MATLAB®.

В аудио подсистеме скремблера блок Integer to Bit Converter распаковывает каждый 16-битный аудиосэмпл в двоичный файл, 1-битный сигнал. Двоичный сигнал передает скремблеру линейного сдвигового регистра обратной связи (LFSR), который рандомизирует биты управляемым способом, таким образом, скремблируя сигнал. Блок Communications Toolbox™ Scrambler используется в реализации LFSR. От LFSR скремблированные аудио биты передают блоку Bit to Integer Converter. Этот блок упаковывает скремблированные 1-битные выборки в 16-битные аудиосэмплы. Аудиосэмплы передают блоку Data Type Conversion, который преобразует основанные на целом числе аудиосэмплы назад в выборки фиксированной точки.

Выборки фиксированной точки передают от подсистемы скремблера до канала. Канал отправляет выборки в подсистему дескремблера. В иллюстративных целях этот пример использует бесшумный канал. В фактической системе канал может ввести шум. Удаление такого шума требует более сложного проекта.

В аудио подсистеме дескремблера блок Integer to Bit Converter распаковывает каждый 16-битный аудиосэмпл в двоичный файл, 1-битный сигнал. Двоичный сигнал передает дескремблеру линейного сдвигового регистра обратной связи (LFSR), который рандомизирует биты управляемым способом, инвертируя процесс скремблирования. Эта реализация дескремблера LFSR использует блок Communications Toolbox Descrambler. От LFSR дескремблированные аудио биты передают блоку Bit to Integer Converter. Этот блок упаковывает дескремблированные 1-битные выборки в 16-битные аудиосэмплы. Аудиосэмплы передают блоку Data Type Conversion, который преобразует основанные на целом числе аудиосэмплы назад в выборки фиксированной точки.

В Simulink sfix16_En15 тип данных представляет (s) фиксированную точку со знаком (фиксируют) сигнал с размером слова 16 и дробная длина 15. Поэтому эта модель представляет звуковые сигналы с помощью sfix16_En15 типа данных, кроме тех случаев, когда, преобразовывая в и от 1-битных двоичных сигналов. Все 1-битные сигналы представлены ufix1, как замечено при выходе блока Integer to Bit Converter. Источник аудиосигналов имеет формат кадра (или количество выборок на систему координат) 1 024. Для получения дополнительной информации о сигналах фиксированной точки обратитесь к Числам Фиксированной точки в документации Simulink.

Необходимо запустить пример, прежде чем можно будет слушать любой из звуковых сигналов.

Можно запустить пример путем нажатия на Simulation> Run.

Можно услышать звуковые сигналы путем нажатия на желтые, значки аудио модели.

В аудио подсистемах скремблера и дескремблера настройки блока Integer to Bit Converter:

Number of bits per integer:

16

Treat input values as:

Signed

Output bit order:

MSB first

Output data type:

Inherit via internal rule

В аудио подсистемах скремблера и дескремблера настройки блока Bit to Integer Converter:

Number of bits per integer:

16

Input bit order:

MSB first

After bit packing, treat resulting integer values as: Signed

Output data type:

Inherit via internal rule