Сгенерируйте действительный или объедините синусоидальные сигналы — оптимизированный для генерации HDL-кода

Поддержка HDL DSP System Toolbox / Операции Сигнала

Поддержка HDL DSP System Toolbox / источники

![]()

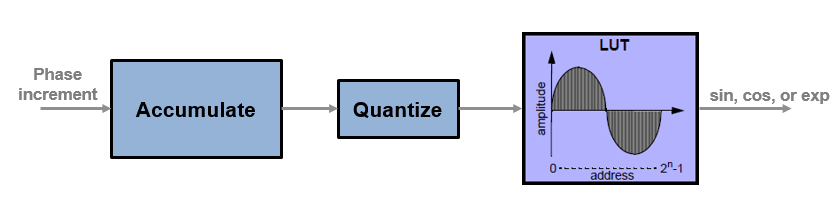

Блок NCO HDL Optimized генерирует действительный, или объедините синусоидальные сигналы при обеспечении благоприятных для оборудования управляющих сигналов. Блок использует то же накопление фазы и алгоритм интерполяционной таблицы, как реализовано в блоке NCO. Когда вы используете входные сигналы целочисленной или фиксированной точки или используете блок в качестве источника без входного сигнала, использование блока квантовало целочисленное накопление, чтобы создать сигнал синусоиды.

Блок NCO HDL Optimized обеспечивает эти функции:

Опция сжатия интерполяционной таблицы, чтобы уменьшать размер интерполяционной таблицы. Это сжатие приводит меньше чем к одной потере LSB в точности. Смотрите Сжатие Интерполяционной таблицы для получения дополнительной информации.

Опция, чтобы синтезировать интерполяционную таблицу к ROM при использовании HDL Coder™ с целью FPGA. Чтобы активировать эту опцию, щелкните правой кнопкой по блоку, выберите HDL Code> HDL Block Properties и установите LUTRegisterResetType на none.

Дополнительный входной порт для внешнего dither.

Дополнительный порт сброса, который инициировал сброс фазы к ее начальному значению во время синусоиды выходная генерация.

Дополнительный выходной порт для текущей фазы NCO.

Учитывая желаемую выходную частоту F 0, вычислите использование входного значения phase increment

, где N является размером слова аккумулятора и

Можно задать шаг фазы использование параметра или входного порта.

Разрешение частоты NCO задано

Учитывая желаемое смещение фазы (в радианах), вычислите использование входного значения phase offset

Можно задать смещение фазы с помощью параметра или входного порта.

Когда вы используете входные сигналы с плавающей точкой, блок не квантует накопление. Поэтому необходимо выбрать шаг и возместить значения, чтобы представлять часть 2π без квантования, видеть, Вычисляют Шаг Фазы С плавающей точкой для Оптимизированного HDL NCO.

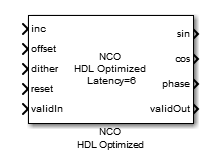

Этот блок появляется в библиотеках Sources с набором параметра Phase increment source к Property. Единственным входным портом является validIn.

Этот блок появляется в библиотеках Signal Operations с набором параметра Phase increment source к Input port. Эта настройка показывает дополнительному входному порту inc.

Этот значок показывает дополнительные порты блока NCO HDL Optimized.

inc — (Дополнительный) шаг фазыШаг фазы, заданный как скалярное целое число. Если шаг является значением фиксированной точки, блок использует только целочисленные биты и игнорирует любые дробные биты. double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода. Когда вы используете входные сигналы с плавающей точкой, необходимо выбрать шаг и возместить значения, чтобы представлять часть 2π, видеть, Вычисляют Шаг Фазы С плавающей точкой для Оптимизированного HDL NCO.

Чтобы включить этот порт, установите Phase increment source на Input port.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

offset — Фаза возместила (дополнительный)Смещение фазы, заданное как скалярное целое число. Если смещение является значением фиксированной точки, блок использует только целочисленные биты и игнорирует любые дробные биты. double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода. Когда вы используете входные сигналы с плавающей точкой, необходимо выбрать шаг и возместить значения, чтобы представлять часть 2π, видеть, Вычисляют Шаг Фазы С плавающей точкой для Оптимизированного HDL NCO.

Чтобы включить этот порт, установите Phase offset source на Input port.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

dither — (Дополнительный) DitherРазмойтесь, заданный как скалярное целое число. double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода.

Чтобы включить этот порт, установите Dither source на Input port.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

reset — Сбросьте (дополнительный) аккумуляторtrue | falseУправляющий сигнал, который сбрасывает аккумулятор, заданный как скалярная булевская переменная. Когда этим сигналом является true(1 ), блок сбрасывает аккумулятор к 0.

Чтобы включить этот порт, выберите Enable reset input port.

Типы данных: Boolean

validIn — Включите (дополнительный) сигналtrue | falseУправляющий сигнал, который включает операцию NCO. Когда этим сигналом является true(1 ), блок постепенно увеличивает фазу. Когда этим сигналом является false(0 ), блок содержит фазу.

Чтобы включить этот порт, выберите Enable valid input port.

Типы данных: Boolean

sin, cos, exp — Сгенерированная форма волныСгенерированная форма волны, возвращенная как скалярный sin или значение cos, как скалярное значение exp, представляющее sine + j*cosine, или как два значения, sin и cos. Если какой-либо вход является типом с плавающей точкой, блок возвращает значения с плавающей точкой, в противном случае блок возвращает значения фиксированной точки. Типы с плавающей точкой поддерживаются для симуляции, но не для генерации HDL-кода.

По умолчанию этот выходной порт является синусоидой, sin. Метка порта и изменения формата на основе вашего выбора для Type of output signal.

phase — Текущая фаза (дополнительного) NCOТекущая фаза NCO, возвращенного как скаляр типа fixdt(1,M,-Z), где M количество квантованных двоичных разрядов аккумулятора и Z размер слова аккумулятора. Блок возвращает phase как плавающую точку, если вход с блоком является плавающей точкой. Типы с плавающей точкой поддерживаются для симуляции, но не для генерации HDL-кода.

Чтобы включить этот порт, выберите Enable phase port.

Типы данных: single | double | fixdt(1,NumQuantizerAccumulatorBits,-AccumulatorWL)

validOut — Указывает на допустимые выходные данные true | falseУправляющий сигнал, который указывает, допустимы ли другие значения выходного порта или нет. Когда validOut является true(1 ), значения на sin, cos, exp и портах phase допустимы. Когда validOut является false(0 ), значения на выходных портах не допустимы.

Типы данных: Boolean

Этот блок поддерживает double и single введите для симуляции, но не для генерации HDL-кода. Когда вход является фиксированной точкой, или когда все входные порты отключены, блок вычисляет выходную форму волны на основе настроек маски фиксированной точки. Когда вход является плавающей точкой, блок вычисляет выходную форму волны с двойной точностью и игнорирует параметры, связанные с настройками фиксированной точки (Number of dither bits, Quantize phase, Number of quantizer accumulator bits, Enable look up table compression method и вкладка Data Types).

Чтобы использовать тип данных заменяют функцию Fixed-Point Designer™, можно получить double выходное значение путем применения double входные данные к одному из дополнительных портов. Когда вы переключаетесь на использование шага фазы с плавающей точкой, необходимо настроить значение шага, чтобы считать из-за отсутствия квантования фазы. Смотрите Вычисляют Шаг Фазы С плавающей точкой для Оптимизированного HDL NCO.

Phase increment source — Источник шага фазыInput port (значение по умолчанию) | PropertyМожно установить шаг фазы с входным портом или путем ввода значения для параметра. Если вы выбираете Property, параметр Phase increment, кажется, для вас вводит значение. Если вы выбираете Input port, порт inc появляется на блоке.

Phase increment — Шаг фазы для сгенерированной формы волныШаг фазы для сгенерированного форма волны, заданная как скалярное целое число. Если шаг является значением фиксированной точки, блок использует только целочисленные биты и игнорирует любые дробные биты. double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода. Когда вы используете входные сигналы с плавающей точкой, необходимо выбрать шаг и возместить значения, чтобы представлять часть 2π, видеть, Вычисляют Шаг Фазы С плавающей точкой для Оптимизированного HDL NCO.

Этот параметр отображается, когда вы устанавливаете Phase increment source на Property.

Типы данных: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixdt([],N,0)

Phase offset source — Источник фазы возмещенInput port (значение по умолчанию) | PropertyМожно установить смещение фазы с входным портом или путем ввода значения для параметра. Если вы выбираете Property, параметр Phase offset, кажется, для вас вводит значение. Если вы выбираете Input port, порт offset появляется на блоке.

Phase offset — Фаза возмещена для сгенерированной формы волныСмещение фазы для сгенерированной формы волны, заданной как скалярное целое число. Если шаг является значением фиксированной точки, блок использует только целочисленные биты и игнорирует любые дробные биты. double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода. Когда вы используете входные сигналы с плавающей точкой, необходимо выбрать шаг и возместить значения, чтобы представлять часть 2π, видеть, Вычисляют Шаг Фазы С плавающей точкой для Оптимизированного HDL NCO.

Этот параметр отображается, когда вы устанавливаете Phase offset source на Property.

Типы данных: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixdt([],N,0)

Dither source — Источник количества битов ditherProperty (значение по умолчанию) | Input port | NoneМожно установить dither от входного порта или от параметра. Если вы выбираете Property, параметр Number of dither bits появляется. Если вы выбираете Input port, порт появляется на блоке. Если вы выбираете None, блок не добавляет dither.

Number of dither bits — Биты раньше выражали ditherКоличество битов dither, заданных как положительное целое число.

Этот параметр отображается, когда вы устанавливаете Dither source на Property.

Quantize phase — Квантуйте накопленную фазуКогда этот параметр включен, блок квантует результат аккумулятора фазы к фиксированной битной ширине. Это квантованное значение используется, чтобы выбрать значение формы волны из интерполяционной таблицы. Выберите разрешение интерполяционной таблицы с помощью параметра Number of quantizer accumulator bits.

Разрешение частоты NCO задано

Когда вы отключаете этот параметр, блок использует полный тип данных аккумулятора в качестве адреса интерполяционной таблицы.

Number of quantizer accumulator bits — Биты раньше выражали фазуКоличество двоичных разрядов аккумулятора квантизатора, заданных как целочисленный скаляр, больше, чем 1 и меньше, чем размер слова аккумулятора. Этот параметр должен быть меньше чем или равен 17 битам для генерации HDL-кода. Интерполяционная таблица значений синуса имеет 2NumQuantizerAccumBits-2 записи.

Этот параметр отображается, когда вы выбираете Quantize phase.

Enable look up table compression method — Сожмите интерполяционную таблицуПо умолчанию блок реализует несжатую интерполяционную таблицу, и выход этого блока совпадает с выходом блока NCO. Когда вы включаете эту опцию, блок реализует сжатую интерполяционную таблицу. Сандерлендский метод сжатия уменьшает размер интерполяционной таблицы, теряя меньше чем один LSB точности. Свободный от паразитных составляющих динамический диапазон (SFDR) опытным путем на 1-3 дБ ниже, чем несжатый случай. Экономия средств на оборудование сжатой интерполяционной таблицы предусматривает пространство, чтобы улучшать производительность путем увеличения размера слова аккумулятора, и количество квантуют биты. Для детали метода сжатия см. Алгоритмы.

Enable reset input port — Включите управляющий сигнал сбросаКогда выбрано, порт reset появляется на блоке. Когда reset является true(1 ), блок сбрасывает аккумулятор, чтобы обнулить.

Enable valid input port — Включите допустимый управляющий сигналКогда выбрано, порт validIn появляется на блоке. Когда validIn является true(1 ), блок постепенно увеличивает фазу. Когда validIn является false(0 ), фаза сохранена.

Type of output signal — Формат выходной формы волныSine (значение по умолчанию) | Cosine | Complex exponential | Sine and cosineЕсли вы выбираете Sine или Cosine, блок показывает применимый порт, sin или cos. Если вы выбираете Complex exponential, выход имеет форму sine + j*cosine и порт помечен exp. Если вы выбираете Sine and cosine, блок показывает два порта, sin и cos.

Show phase port — Выведите текущую фазуВыведите текущую фазу аккумулятора, когда выбрано.

Overflow mode — Режим переполнения для операций фиксированной точкиWrap (значение по умолчанию)Режим переполнения для операций фиксированной точки. Overflow mode является параметром только для чтения. Числа фиксированной точки повторяются на переполнении.

Rounding Mode — Режим Rounding для операций фиксированной точкиFloor (значение по умолчанию)Режим Rounding для операций фиксированной точки. Rounding Mode является параметром только для чтения со значением Floor.

Accumulator Data Type — Тип данных аккумулятораBinary point scaling (значение по умолчанию)Описание типов данных аккумулятора. Этот параметр только для чтения со значением Binary point scaling. Блок задает тип данных с фиксированной точкой с помощью Accumulator Signed, Accumulator Word length и параметров Accumulator Fraction length.

Accumulator Signed — Подписанный или формат данных аккумулятора без знакаSigned (значение по умолчанию)Этот параметр только для чтения. Весь выход является подписанным форматом.

Accumulator Word length — Размер слова аккумулятораРазмер слова аккумулятора, в битах, заданных как скалярное целое число.

Если Quantize phase отключен, этот параметр должен быть меньше чем или равен 17 битам для генерации HDL-кода.

Accumulator Fraction length — Длина части аккумулятораЭтот параметр только для чтения. Длина части аккумулятора является нулевыми битами.

Аккумулятор работает с целыми числами. Если шагом фазы является fixdt введите с дробной частью, блок игнорирует дробную часть.

Output Data Type — Тип выходных данныхBinary point scaling (значение по умолчанию) | double | singleЗадайте тип данных выходного сигнала. Если вы выбираете Binary point scaling, блок задает тип данных с фиксированной точкой с помощью Output Signed, Output Word length и параметров Output Fraction length.

Output Signed — Подписанный или формат выходных данных без знакаSigned (значение по умолчанию)Этот параметр только для чтения. Весь выход является подписанным форматом.

Output Word length — Выведите размер словаВыведите размер слова, в битах, заданных как скалярное целое число.

Output Fraction length — Выведите дробную длинуВыведите дробную длину, в битах, заданных как скалярное целое число.

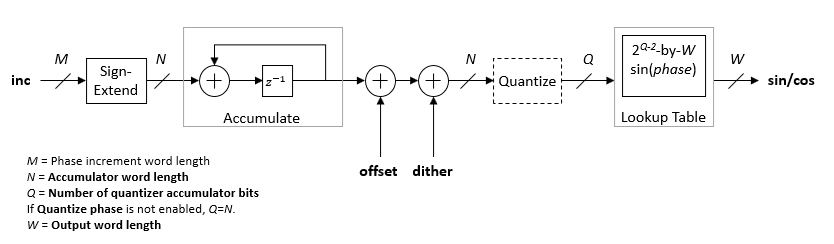

Реализация NCO зависит от того, выбираете ли вы Enable look up table compression method.

Без сжатия интерполяционной таблицы блок использует ту же интерполяционную таблицу четверти синуса в качестве блока NCO. Размер LUT 2Number квантизатора accumulator bits-2×Output word length биты.

Если вы не включаете Quantize phase, то Number of quantizer accumulator bits =Accumulator Word length. Рассмотрите удар на ресурсы памяти средства моделирования и аппаратные ресурсы, когда вы выберете эти параметры.

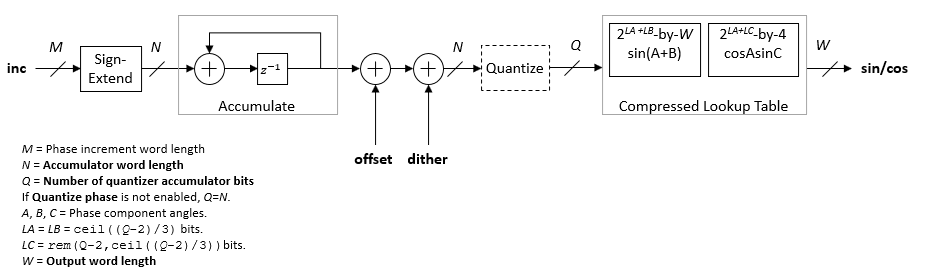

Когда вы выбираете интерполяционную таблицу (LUT) сжатие, блок NCO HDL Optimized применяет Сандерлендский метод сжатия. Сандерлендские методы используют тригонометрические тождества, чтобы разделить каждую фазу синусоиды четверти на три компонента и выразить его как:

Если фаза четверти синуса имеет Q-2 биты, затем компоненты фазы A и B перебрасываются парой слов длина LA =LB=ceil((Q-2)/3). Компонент фазы C содержит остающиеся биты фазы. Если фаза имеет 12 битов, то фаза синуса четверти имеет 10 битов, и компоненты заданы как:

A, четыре старших значащих бита

B, следующие четыре бита

C, остающиеся два младших значащих бита

Учитывая относительные размеры A, B, и C, уравнение может быть аппроксимировано:

Блок NCO HDL Optimized реализует это уравнение с одним LUT для![]() и одним LUT для

и одним LUT для![]() . Второй срок является прекрасным поправочным коэффициентом, который можно обрезать до меньшего количества битов, не теряя точность. Поэтому второй LUT возвращает четырехбитный результат.

. Второй срок является прекрасным поправочным коэффициентом, который можно обрезать до меньшего количества битов, не теряя точность. Поэтому второй LUT возвращает четырехбитный результат.

С размером аккумулятора по умолчанию 16 битов и значением по умолчанию квантовал фазу width 12 битов, использование LUTs 28×16 плюс 26×4 биты (4,5 Кбита). Интерполяционная таблица синуса четверти использует 210×16 биты (16 Кбит). Это приближение с точностью до одного LSB, приводящего к ОСШ по крайней мере 60 дБ на выходе. См. [1].

Существует два сигнала элемента управления вводом, reset и validIn, и один сигнал элемента управления выводом, validOut. Когда reset является true(1 ), блок обнуляет аккумулятор фазы. Когда validIn является true(1 ), блок постепенно увеличивает фазу. Когда validIn является false(0 ), блок останавливает аккумулятор фазы и содержит его состояние. Когда validOut является true(1 ), выход допустим.

Задержка блока NCO HDL Optimized является шестью циклами.

[1] Cordesses, L., "Прямой цифровой синтез: Инструмент для Периодической Генерации Волны (Часть 1)". Журнал Обработки сигналов IEEE. Объем 21, Выпуск 4, июль 2004, стр 50–54.

Этот блок поддерживает генерацию кода C/C++ для акселератора Simulink® и быстрых режимов Accelerator и для генерации компонента DPI.

HDL Coder обеспечивает дополнительные параметры конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| LUTRegisterResetType | Тип сброса интерполяционной таблицы выходной регистр. Выберите |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

Когда вы устанавливаете Dither source на Property, блок добавляет случайный dither каждый цикл. Если вы генерируете модель валидации с этими настройками, предупреждение выведено. Случайная генерация внутреннего dither может вызвать несоответствия между моделями. Можно увеличить допуск на погрешность для сравнения валидации, чтобы составлять различие. Можно также отключить dither или установить Dither source на Input port избегать этой проблемы.

Вы не можете использовать блок NCO HDL Optimized в Resettable Synchronous Subsystem.

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.