В этом примере показано, как можно сгенерировать HDL-код для простого Counter модель. Модель является простым суммирующим счетчиком, который подсчитывает от нуля до порогового значения и затем переносится назад, чтобы обнулить. Прежде чем вы сгенерируете HDL-код для этой модели, рекомендуется, чтобы вы проверили совместимость HDL своей модели при помощи Средства проверки Модели HDL. Учиться как:

Создайте эту встречную модель, смотрите, Создают Модель Simulink для генерации HDL-кода.

Проверяйте совместимость HDL встречной модели, смотрите Совместимость HDL Проверки Модели Используя Средство проверки Модели HDL.

По умолчанию HDL Coder™ создает hdlsrc папка в текущей рабочей папке, чтобы сгенерировать файлы HDL. Поэтому, прежде чем вы продолжаете генерировать HDL-код, убедитесь, что ваша текущая рабочая папка writeable.

Откройте эту модель, чтобы видеть простой суммирующий счетчик. Модель подсчитывает от нуля до порогового значения и затем переносится назад, чтобы обнулить. В этой модели пороговое значение установлено в 15. Можно изменить пороговое значение путем изменения значения блока Constant, который вводится к count_threshold порт. Разрешать сигнал задает, должен ли счетчик подсчитать или содержать предыдущее значение. Разрешать сигнал установлен в 1 что означает, что счетчик рассчитывает вверх постоянно.

open_system('hdlcoder_simple_up_counter.slx') set_param('hdlcoder_simple_up_counter', 'SimulationCommand', 'Update')

Чтобы сгенерировать код, вы используете вкладку HDL Code в, Чтобы открыть Средство проверки Модели HDL, Выбрать DUT Subsystem и затем нажать HDL Code Advisor.

Для модели суммирующего счетчика Подсистема HDL_DUT является DUT. Сгенерировать код для DUT:

Во вкладке Apps выберите HDL Coder. Вкладка HDL Code появляется.

Выберите DUT Subsystem в своей модели и убедитесь, что это имя Subsystem появляется в опции Code for. Чтобы помнить выбор, можно прикрепить эту опцию. Нажмите Generate HDL Code.

По умолчанию HDL Coder генерирует код VHDL в целевом hdlsrc папка.

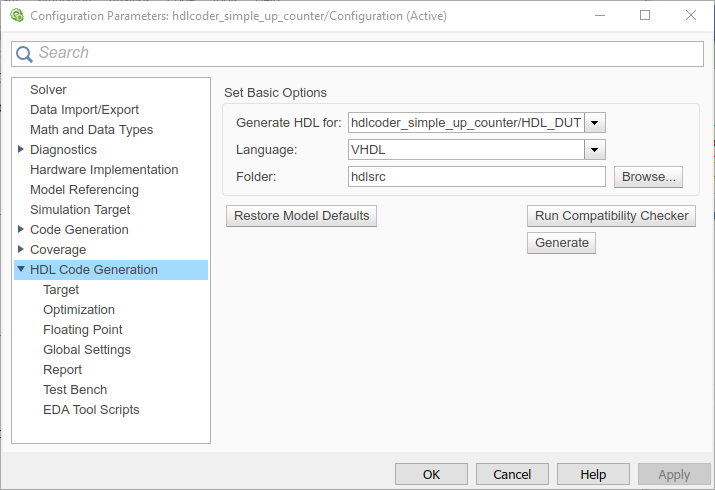

Если вы хотите сгенерировать код Verilog, можно задать эту установку в панели HDL Code Generation диалогового окна Configuration Parameters. Прежде чем вы сгенерируете код, можно также настроить настройки уровня модели для проекта те, которые включают нативную поддержку с плавающей точкой, генерируют ресурс и отчеты трассируемости, используют оптимизацию уровня модели и изменяют другие глобальные настройки.

Сгенерировать код Verilog для встречной модели:

Во вкладке HDL Code нажмите Settings.

В панели HDL Code Generation, для Language, выбирают Verilog. Оставьте другие настройки значению по умолчанию. Нажмите Apply и затем нажмите Generate.

HDL Coder компилирует модель прежде, чем сгенерировать код. В зависимости от параметров отображения модели, таких как типы данных порта, модель может изменение внешности после генерации кода. В то время как генерация кода продолжает, HDL Coder отображает сообщения о ходе выполнения в командной строке MATLAB® с:

Соединитесь с Конфигурацией модели, которая указывает на модель, для которой применяются Параметры конфигурации.

Ссылки на сгенерированные файлы. Чтобы просмотреть файлы в редакторе MATLAB, щелкните по ссылкам.

Процесс завершается с сообщением:

### HDL Code Generation Complete.

Значок папки для hdlsrc папка теперь отображается в Браузере текущей папки. Чтобы просмотреть сгенерированный код и файлы скрипта, дважды кликните hdlsrc значок папки. В папке вы видите, что файл содержит код VHDL или Verilog, скрипт, чтобы скомпилировать сгенерированный код, скрипт синтеза и файл отображения. Например, если вы сгенерированный код для symmetric_fir Подсистема, вы видите эти файлы в hdlsrc папка:

HDL_DUT.vhd: Этот файл является кодом VHDL®, который содержит определение сущности и архитектуру RTL, реализующую суммирующий счетчик, который вы спроектировали.

Если вы сгенерировали код Verilog, вы получаете HDL_DUT.v файл.

HDL_DUT_compile.do: Наставник скрипт компиляции Graphics® ModelSim®. Чтобы вызвать этот скрипт и скомпилировать сгенерированный код VHDL, вы используете vcom команда.

HDL_DUT_synplify.tcl: Этот файл является синтезом Synplify® скрипт TCL.

HDL_DUT_map.txt: Этот файл отчета является файлом отображения, который сгенерировал сущности или модули к подсистемам, которые сгенерировали их. См., что Код Трассировки Использует Файл Отображения.

HDL_DUT_report.html: Этот файл является отображениями отчета Проверки генерации HDL-кода состояние генерации HDL-кода и любых предупреждений или сообщений. Если генерация HDL-кода перестала работать, вы видите причину отказа в отчете Проверки.

gm_hdlcoder_simple_up_counter.slx: Этот файл является сгенерированной моделью, которая поведенчески представляет HDL-код в среде моделирования Simulink®. Для получения дополнительной информации см. Сгенерированную Модель Модели и Валидации.

Прежде чем вы продолжите развертывать свой проект на целевом компьютере, необходимо проверить сгенерированный HDL-код. От hdlsrc папка, перейдите к текущей рабочей папке. Чтобы изучить, как можно проверить сгенерированный HDL-код, смотрите, Проверяют Сгенерированный код из Модели Simulink Используя Испытательный стенд HDL.

hdlset_param | hdlsetup | makehdl