Откройте свою модель и выберите Simulation> Model Configuration Parameters.

Выберите панель Code Generation.

В System target file, под Target Selection, нажимают Browse. Выберите systemverilog_dpi_grt.tlc из списка.

В качестве альтернативы, если у вас есть лицензия Embedded Coder®, можно выбрать целевой systemverilog_dpi_ert.tlc. Эта цель позволяет вам получить доступ к своим опциям генерации дополнительного кода на панели Code Generation диалогового окна Model Configuration Parameters.

Все еще на панели Code Generation, выберите Toolchain. Чтобы сгенерировать разделяемую библиотеку для той же операционной системы как хост-машина, выберите компилятор из списка установленных компиляторов или выберите Automatically locate an installed toolchain. Чтобы использовать компилятор, включенный с симулятором HDL, или сгенерировать компонент для различной операционной системы или сгенерировать проект симулятора HDL, а не разделяемую библиотеку, выбирают симулятор HDL и вашу целевую операционную систему.

Для кросс-платформенной генерации выберите Package code and artifacts, чтобы сгенерировать .zip файл, чтобы портировать сгенерированные файлы на целевую машину. Смотрите Генерируют Кросс-платформенные Компоненты DPI.

Можно опционально добавить дополнительные флаги компиляции. Под Build Configuration выберите Specify. Чтобы отобразить текущие флаги, нажмите Show Settings.

Завершите этот шаг, если вы определяли внутренние сигналы в своей модели как тестовые точки, и хотят получить доступ к ним в сгенерированном компоненте DPI.

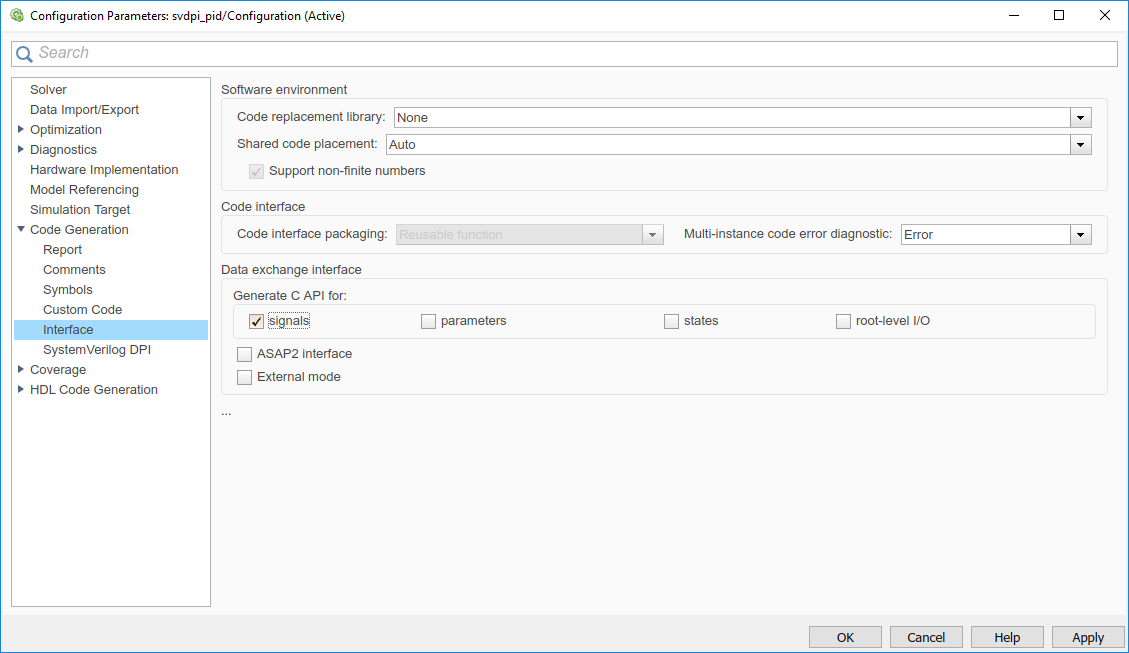

На левой панели выберите Code Generation> Interface.

В разделе Generate C API for проверьте, что флажок signals устанавливается.

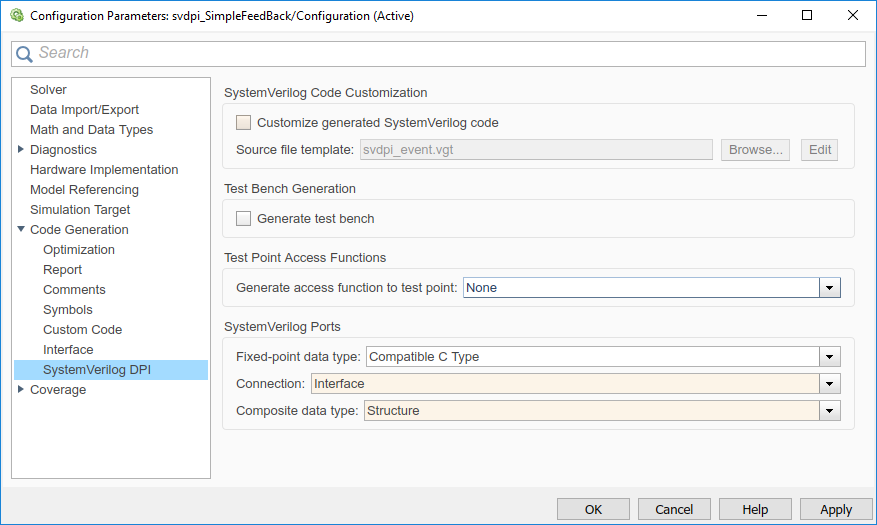

Выберите Code Generation> SystemVerilog DPI.

Для Generate access function to test point выберите One function per Test Point или One function for all Test Points.

Смотрите тестовую точку компонента SystemVerilog DPI доступ.

На левой панели выберите Code Generation> SystemVerilog DPI.

Чтобы сгенерировать испытательный стенд, выберите Generate test bench. Испытательный стенд проверяет сгенерированный компонент C по векторам данных от вашей подсистемы Simulink®.

В разделе SystemVerilog Ports:

Выберите типы данных SystemVerilog. (дополнительный)

Задайте Port list или Interface для Connection.

Выберите Structure для Composite data types. Эта опция создает SystemVerilog struct типы данных для любых невиртуальных шин или для сложных типов данных. В качестве альтернативы выберите Flattened создать сглаженные порты.

Нажмите OK, чтобы принять эти настройки и закрыть диалоговое окно Configuration Parameters.

В вашей модели щелкните правой кнопкой по блоку, содержащему подсистему, от которой вы хотите сгенерировать компонент и установить подсистему как атомарную:

Кликните по подсистеме.

Выберите Block Parameters (Subsystem).

Выберите Treat as atomic unit.

Выберите Code> C/C++ Code> Build Selected Subsystem.

Нажмите Build.

Компонент SystemVerilog сгенерирован как subsystem_build/subsystem_dpi.svsubsystem имя подсистемы, от которой вы сгенерировали компонент DPI. Эта сборка также приводит к сгенерированному файлу с именем пакета subsystem_build/subsystem_dpi_pkg.sv

Если вы создали компонент для хост-машины, можно теперь использовать компонент. Чтобы скопировать созданный компонент в другую машину с той же операционной системой, скопируйте эти файлы:

Разделяемая библиотека, subsystem.so, или subsystem.dll

Сгенерированная обертка SystemVerilog, subsystem.sv

Сгенерированный файл пакета SystemVerilog, subsystem_pkg.sv

Сгенерированная папка испытательного стенда, dpi_tb (дополнительный)

Чтобы портировать компонент на другую машину с различной операционной системой, следуйте инструкциям в, Генерируют Кросс-платформенные Компоненты DPI.