Ограничьте значения сигналов в тестах

Simulink Design Verifier

При работе в режиме генерации тестов программное обеспечение Simulink® Design Verifier™ производит тесты, которые удовлетворяют заданным критериям (см. то, Что Генерация Теста?). В этом режиме можно использовать блоки Условия испытания, чтобы задать условия испытания для сигналов в модели. Параметр Values позволяет вам задать ограничения на значения сигналов во время симуляции теста. Блок применяет заданный параметр Values к своему входному сигналу, и программное обеспечение Simulink Design Verifier пытается произвести тесты, которые удовлетворяют условию.

Диалоговое окно параметра блока также позволяет вам

Включите или отключите условие.

Укажите, что блок должен отобразить свой параметр Values в Редакторе Simulink.

Укажите, что блок должен отобразить свой выходной порт.

Программное обеспечение Simulink и Simulink Coder™ игнорирует блок Test Condition во время симуляции модели и генерации кода, соответственно. Программное обеспечение Simulink Design Verifier использует блок Test Condition только при генерации тестов для модели.

Используйте параметр Values, чтобы ограничить значения сигналов в тестах. Задайте любую комбинацию скаляров и интервалов в форме массива ячеек MATLAB®. Для получения информации о массивах ячеек см. Массивы ячеек (MATLAB).

Если параметр Values задает только одно скалярное значение, вы не должны вводить его в форме массива ячеек MATLAB.

Скалярные значения каждый включает отдельную ячейку в массиве, например:

{0, 5}Закрытый интервал включает двухэлементный вектор как ячейку в массиве, где каждый элемент задает конечную точку интервала:

{[1, 2]}В качестве альтернативы можно задать скалярные значения с помощью Sldv.Point конструктор, который принимает одно значение как его аргумент. Можно задать интервалы с помощью Sldv.Interval конструктор, который требует двух входных параметров, т.е. нижней границы и верхней границы для интервала. Опционально, можно ввести одно из следующих значений как третий входной параметр, который задает включение или исключение конечных точек интервала:

'()' — Задает открытый интервал.

'[]' — Задает закрытый интервал.

'(]' — Задает лево-открытый интервал.

'[)' — Задает правильно-открытый интервал.

По умолчанию, Sldv.Interval полагает, что интервал закрывается, если вы не используете его третий входной параметр.

Как пример, параметр Values

{0, [1, 3]}задает:

0 — скаляр

[1, 3] — закрытый интервал

Параметр Values

{Sldv.Interval(0, 1, '[)'), Sldv.Point(1)}задает:

Sldv.Interval(0, 1, '[)') — правильно-открытый интервал [0, 1)

Sldv.Point(1) — скаляр

Если вы задаете несколько скаляров и интервалов для блока Test Condition, программное обеспечение Simulink Design Verifier комбинирует их использующий логическую операцию OR при генерации тестов. Следовательно, программное обеспечение полагает, что целое условие испытания удовлетворено, удовлетворяют ли какому-либо одному скаляру или интервалу.

В одном скаляре или интервале, условие испытания сгенерировано с логической операцией И. В этом случае все сигналы должны удовлетворить ограничениям для входа, чтобы удовлетворить условию.

Например, рассмотрите двумерный открытый интервал:

Sldv.Interval([-5 -5],[5 2],'()')

Нулевой векторный [0 0] удовлетворяет условию, потому что нулевыми элементами является в интервалах -5 к 5 и -5 к 2.

Векторный [0 3] не удовлетворяет условию, потому что второй элемент 3 выходит за пределы интервала -5 к 2.

Блок Test Condition принимает сигналы всех встроенных типов данных, поддержанных программным обеспечением Simulink. Для обсуждения типов данных, поддержанных программным обеспечением Simulink, смотрите Типы данных, Поддержанные Simulink (Simulink). Блок не поддерживает комплексные входные сигналы.

Задайте, включен ли блок. Если выбрано (значение по умолчанию), программное обеспечение Simulink Design Verifier использует блок при генерации тестов для модели. Очистка этой опции отключает блок, то есть, заставляет программное обеспечение Simulink Design Verifier вести себя, как будто блок Test Condition не существовал. Если эта опция не выбрана, блок появляется grayed в Редакторе Simulink.

Задайте, ведет ли блок себя как блок Test Condition или Proof Assumption. Выберите Assumption преобразовать блок Test Condition в блок Proof Assumption.

Задайте условие испытания (см. Условия испытания Определения).

Задайте, отображает ли блок содержимое своего параметра Values в Редакторе Simulink. По умолчанию эта опция выбрана.

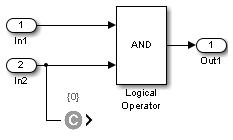

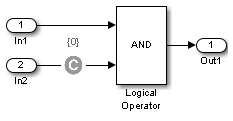

Задайте, отображает ли блок выходной порт в Редакторе Simulink. Если выбрано (значение по умолчанию), блок отображает свой выходной порт, позволяя его входному сигналу пройти как блок выход. Если не выбранный, блок скрывает свой выходной порт и отключает входной сигнал. Следующая графика иллюстрирует внешний вид блока в каждом случае.

Pass through style: Selected

Pass through style: Deselected