Этот пример показывает верификацию подсистемы путем обеспечения выхода программного обеспечения в цикле (SIL) соответствия кода та из подсистемы модели. Вы генерируете обвязку верификации SIL, собираете результаты симуляции и сравниваете результаты с помощью инспектора данных моделирования. Можно применить подобный процесс для процессора в цикле (PIL) верификация.

С SIL симуляцией можно проверить поведение производственного исходного кода на хосте - компьютере. Кроме того, с PIL симуляцией можно проверить скомпилированный объектный код, который вы намереваетесь развернуть в производстве. Можно запустить объектный код PIL на действительном целевом компьютере или на симуляторе процессора.

Если у вас есть лицензия Embedded Coder®, можно создать тестовую обвязку в режиме SIL или PIL для верификации модели. Можно сравнить результаты блока SIL или PIL с результатами модели и собрать метрики, включая время выполнения и покрытие кода. Используя тестовую обвязку, чтобы выполнить SIL и верификацию PIL, вы можете:

Управляйте обвязкой со своей моделью. Генерация тестовой обвязки генерирует блок SIL. Тестовая обвязка сопоставлена с компонентом при верификации. Можно сохранить тестовую обвязку с основной моделью.

Используйте встроенные инструменты для этих рабочих процессов тестового теста проекта:

Проверка эквивалентности блока SIL или PIL

Обновление блока SIL или PIL к последнему проекту модели

Просмотрите и сравните записанные данные и сигналы с помощью менеджера по Тесту и Инспектора Данных моделирования.

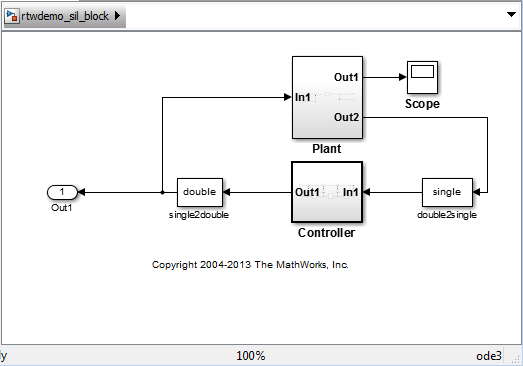

Этот пример моделирует систему объекта контроллера с обратной связью. Контроллер регулирует объект выход.

Создайте обвязку верификации SIL с помощью данных, которые вы регистрируете от симуляции модели подсистемы контроллера. Вам нужна лицензия Embedded Coder на этот пример. Другой способ создать обвязку SIL с Создать Тестом для Мастера Компонента модели (см., Генерируют Тесты для Компонента и Создают и Запущенный Компенсационный Тест).

Откройте модель в качестве примера путем ввода

rtwdemo_sil_block

Сохраните копию модели с помощью имени controller_model в новой папке, в перезаписываемом месте на пути MATLAB.

Включите логгирование сигнала для модели. В командной строке войти

set_param(bdroot,'SignalLogging','on','SignalLoggingName',... 'SIL_signals','SignalLoggingSaveFormat','Dataset')

Щелкните правой кнопкой по сигналу в порт Controller In1 и выберите Properties. В диалоговом окне Signal Properties, для Signal name, вводят controller_model_input. Выберите Log signal data и нажмите OK.

Щелкните правой кнопкой по сигналу из порта Controller Out1 и выберите Properties. В диалоговом окне Signal Properties, для Signal name, вводят controller_model_output. Выберите Log signal data и нажмите OK.

Симулируйте модель.

Получите регистрируемые сигналы от симуляции выход в рабочую область. В командной строке войти

out_data = out.get('SIL_signals');

control_in1 = out_data.get('controller_model_input');

control_out1 = out_data.get('controller_model_output');Создайте программное обеспечение в тестовой обвязке цикла. Щелкните правой кнопкой по Подсистеме контроллера и выберите Test Harness > Create Test Harness (Controller).

Установите свойства обвязки:

Имя: SIL_harness

Sources and Sinks: Inport и Outport

Выберите Open harness after creation

Advanced Properties – Verification Mode: Software-in-the-loop (SIL)

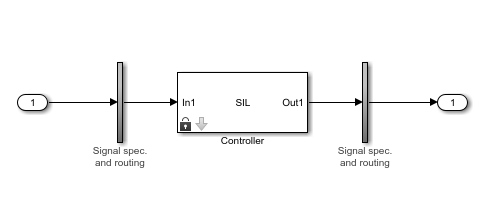

Нажмите OK. Получившаяся тестовая обвязка имеет блок SIL.

Сконфигурируйте и симулируйте обвязку верификации SIL для подсистемы контроллера.

Сконфигурируйте тестовую обвязку, чтобы импортировать регистрируемые входные значения контроллера. От верхнего уровня тестовой обвязки, в диалоговом окне модели Configuration Parameters, в панели Data Import/Export, выбирают Input. Введите control_in1.Values как вход и нажимают OK.

Включите логгирование сигнала для тестовой обвязки. В командной строке войти

set_param('SIL_harness','SignalLogging','on','SignalLoggingName',...

'harness_signals','SignalLoggingSaveFormat','Dataset')Щелкните правой кнопкой по выходному сигналу блока SIL и выберите Properties. В диалоговом окне Signal Properties, для Signal name, вводят SIL_block_out. Выберите Log signal data и нажмите OK.

Симулируйте обвязку.

Сравните выходные параметры для обвязки верификации и подсистемы контроллера.

В модели тестовой обвязки, в разделе Review Results, нажимают Data Inspector

![]() , чтобы открыть Инспектора Данных моделирования.

, чтобы открыть Инспектора Данных моделирования.

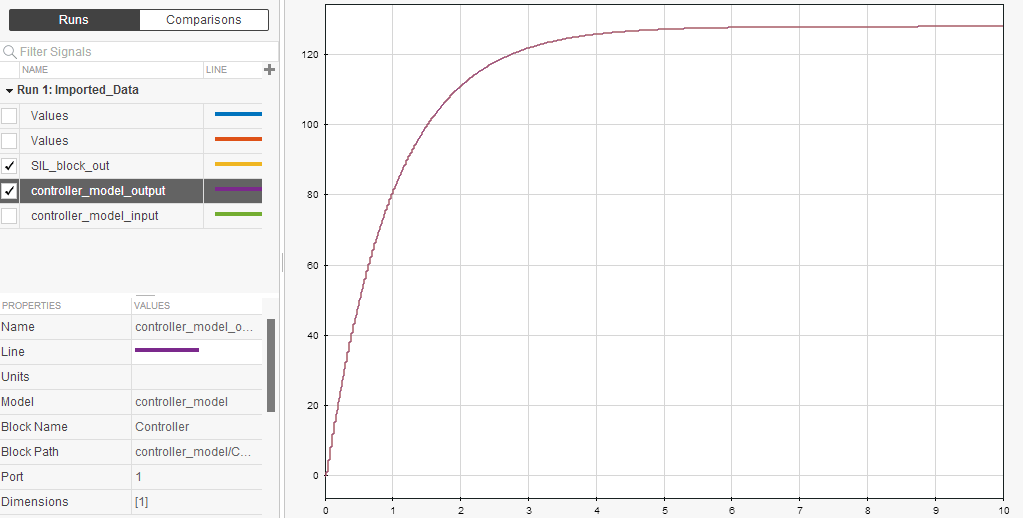

В Инспекторе Данных моделирования нажмите Import. В диалоговом окне Import.

Установите Import from на: Base workspace.

Установите Import to на: New Run.

Под Data to import выберите Signal Name, чтобы импортировать данные из всех источников.

Нажмите Import.

Выберите SIL_block_out и controller_model_out сигналы в панели Runs инспектора данных окно.

График отображает два сигнала, которые накладываются. Этот результат предлагает эквивалентность для кода SIL. Можно построить различия сигнала с помощью вкладки Compare в SDI и выполнить более детальные анализы для верификации. Для получения дополнительной информации смотрите, Сравнивают Данные моделирования (Simulink).

Закройте окно тестовой обвязки. Вы возвращаетесь к основной модели. Значок![]() на блоке Controller указывает, что обвязка SIL сопоставлена с подсистемой.

на блоке Controller указывает, что обвязка SIL сопоставлена с подсистемой.