Десятикратно уменьшите сигнал с помощью каскадного интегрально-гребенчатого фильтра, оптимизированного для генерации HDL-кода

Поддержка HDL DSP System Toolbox / фильтрация

Блок CIC Decimation HDL Optimized десятикратно уменьшает входной сигнал при помощи децимирующего фильтра каскадной расчески интегратора (CIC). CIC-фильтры являются классом КИХ-фильтров линейной фазы, состоящих из части расчески и части интегратора. Структура децимирующего фильтра CIC состоит из разделов N каскадных интеграторов, фактора изменения уровня R и разделов N каскадных гребенчатых фильтров. Для получения дополнительной информации о Децимирующем фильтре CIC, см. Алгоритмы.

Блок поддерживает и фиксируемые и переменные ставки децимации. Это обеспечивает архитектуру, подходящую для аппаратного развертывания и генерации HDL-кода.

data — Входные данныеВходные данные в виде целого числа со знаком или подписанной фиксированной точки с размером слова, меньше чем или равным 32.

Типы данных: int8 | int16 | int32 | fixed point

Поддержка комплексного числа: Да

valid — Индикация относительно допустимых входных данныхИндикация относительно допустимых входных данных в виде булева скаляра.

Этот порт является управляющим сигналом, который указывает, допустимы ли входные данные. Когда этим значением является 1, блок получает значения от входного порта data. Когда этим значением является 0, блок игнорирует значения от входного порта data.

Типы данных: Boolean

decimFactor — Переменный уровень децимацииИспользуйте этот порт, чтобы динамически задать переменный уровень децимации в течение времени выполнения.

Это значение должно иметь тип данных ufix12 и в диапазоне от 2 до значения параметров Decimation factor (R).

Чтобы включить этот порт, выберите параметр Variable decimation.

Типы данных: fixdt(0,12,0)

reset — Очистите внутренние состоянияОчистите внутренние состояния в виде булева скаляра.

Когда этим значением является 1, блок останавливает текущее вычисление и очищает все внутренние состояния. Когда этим значением является 0 и входом valid является 1, блок запускает новую операцию фильтрации.

Чтобы включить этот порт, выберите параметр Enable reset input port.

Типы данных: Boolean

data — CIC десятикратно уменьшил выходные данныеCIC десятикратно уменьшил выходные данные, возвращенные как скаляр.

Можно задать тип выходных данных блока путем установки параметра Output data type.

Типы данных: int8 | int16 | int32 | fixed point

Поддержка комплексного числа: Да

valid — Индикация относительно допустимых выходных данныхИндикация относительно допустимых входных данных, возвращенных как булев скаляр.

Этот порт является управляющим сигналом, который указывает, допустимы ли данные из выходного порта data. Когда этим значением является 1, блок возвращает допустимые данные по выходному порту data. Когда этим значением является 0, значения на выходном порте data не допустимы.

Типы данных: Boolean

Variable decimation — Переменный уровень децимацииoff (значение по умолчанию) | onВыберите этот параметр, чтобы управлять блоком с переменным уровнем децимации, заданным от порта decimFactor. Очистите этот параметр, чтобы управлять блоком с фиксируемой ставкой децимации, заданной от параметра Decimation factor (R).

Decimation factor (R) — Фактор децимацииЗадайте уровень фактора децимации, с которым вы хотите десятикратно уменьшить вход.

Установите этот параметр на максимальное возможное значение, поддержанное от порта decimFactor, когда вы выберете параметр Variable decimation.

Differential delay (M) — Дифференциальная задержка2Задайте дифференциальную задержку части расчески блока.

Number of sections (N) — Количество интегратора и разделов расчески1| 3 Задайте количество разделов или в части расчески или в части интегратора блока.

Output data type — Тип данных выходаFull precision (значение по умолчанию) | Same word length as input | Minimum section word lengthsВыберите тип данных для выходных данных.

Full precision — Тип выходных данных перебрасывается парой слов длина, равная входному размеру слова плюс биты усиления.

Same word length as input — Тип выходных данных перебрасывается парой слов длина, равная входному размеру слова.

Minimum section word lengths — Тип выходных данных использует размер слова, который вы задаете в параметре Output word length. Когда вы выбираете эту опцию, блок применяет алгоритм Сокращения. Для получения дополнительной информации об алгоритме Сокращения, см. [1]. Эта опция не поддержана, когда вы выбираете параметр Variable decimation.

Output word length — Размер слова выходаЗадайте размер слова выхода.

Когда этим значением является 2, 3, 4, 5, или 6 блок может переполнить выходных данных.

Чтобы включить этот параметр, установите параметр Output data type на Minimum section word lengths.

Gain correction — Выведите компенсацию усиленияoff (значение по умолчанию) | onВыберите этот параметр, чтобы компенсировать выходное усиление блока.

В зависимости от типа децимации вы задаете и значение этого параметра, задержка изменений блока.

Для фиксированной децимации (параметр Variable decimation очищен):

Когда вы очищаете этот параметр, задержка блока равняется 3 + такты N.

Когда вы выбираете этот параметр, задержка блока равняется 3 + N + 9 тактов.

Для переменной децимации (параметр Variable decimation выбран):

Когда вы очищаете этот параметр, задержка блока равняется 4 + такты N.

Когда вы выбираете этот параметр, задержка блока равняется 4 + N + 9 тактов.

Enable reset input port — Сбросьте сигналoff (значение по умолчанию) | onВыберите этот параметр, чтобы включить входной порт reset.

Передаточная функция децимирующего фильтра CIC

где:

H я - передаточная функция части интегратора фильтра.

H C является передаточной функцией части расчески фильтра.

N является количеством разделов. Количество разделов в CIC-фильтре задано как количество разделов или в части расчески или в части интегратора фильтра. Это значение не представляет общее количество разделов в целом фильтре.

R является фактором децимации.

M является дифференциальной задержкой.

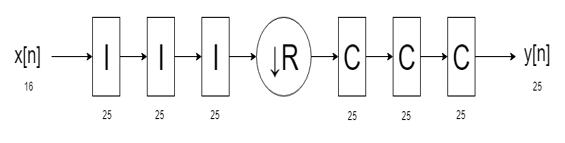

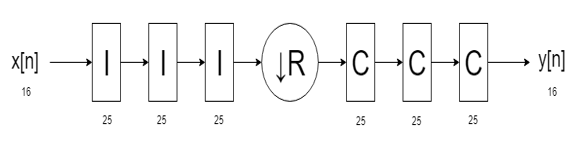

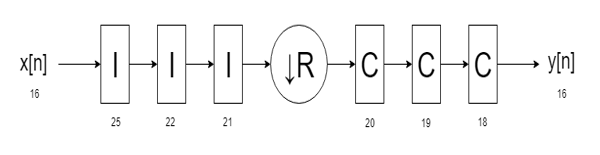

Блоку CIC Decimation HDL Optimized показали структуру CIC-фильтра в этом рисунке. Структура состоит из разделов N каскадных интеграторов, фактора изменения уровня R и разделов N каскадных гребенчатых фильтров [1].

Можно определить местоположение единичной задержки в части интегратора CIC-фильтра или в feedforward или в пути к обратной связи. Эти две настройки дают к идентичной частотной характеристике фильтра. Однако числовые выходные параметры от этих двух настроек отличаются из-за задержки блока. Поскольку, настройка предпочтена для реализации HDL, этот блок помещает единичную задержку в путь feedforward интегратора.

Блок прореживает этап интегратора выход с помощью R, или фиксируемая ставка децимации обеспечила, использование параметра Decimation factor (R) или переменного уровня децимации обеспечило использование входного порта decimFactor. На этапе downsampler блок использует в противоречии с количеством допустимые входные выборки, которые зависят от уровня децимации. Каждый раз, когда уровень децимации изменяется, блок сбрасывает и запускает новое вычисление со следующей выборки. Этот механизм препятствует тому, чтобы блок накопил ложные значения. Затем блок предоставляет подкошенный выход части расчески.

Усилением блока дают ,

где:

R является значением параметров Decimation factor (R).

M является значением параметров Differential delay (M).

N является значением параметров Number of sections (N).

Блок реализует коррекцию усиления в двух частях: крупное усиление и прекрасное усиление. В крупной коррекции усиления блок вычисляет значение сдвига, добавляет значение сдвига к дробным битам, чтобы создать числовой тип и выполняет оставленный сдвиг разряда и reinterpretcast. В прекрасной коррекции усиления блок делит остающееся усиление с крупным усилением, если усиление не является степенью 2. Затем блок умножается, откорректированное крупное усиление откорректировало значение обратным значением прекрасного усиления. Прежде чем блок начинает обрабатывать, весь возможный сдвиг и прекрасные значения усиления предварительно вычисляются первоначально и хранятся в массиве.

Можно изменить это уравнение как . В этом уравнении cGain является крупным усилением, и fGain является прекрасным усилением. Эти усиления даны этими уравнениями.

Чтобы выполнить коррекцию усиления, когда параметр Variable decimation выбран, блок устанавливает тип выходных данных, сконфигурированный с максимальным уровнем децимации, и сдвиги разряда уехали во все значения под максимальным уровнем децимации. Значение сдвига разряда равно .

Этот раздел объясняет как блок выходные данные на основе выбора типа выходных данных. Рассмотрите блок с R, M и значениями N 8, 1, и 3, соответственно, и вход width 16. Выходной размер слова вычисляется как ,

где:

B IN является входным размером слова.

B OUT является выходным размером слова.

Когда вы устанавливаете параметр Output data type на Full precision, блок выходные данные с размером слова 25 путем добавления девяти битов усиления во входной размер слова 16.

Когда вы устанавливаете параметр Output data type на Same word length as input, выходные данные о блоке с размером слова 16, который является той же длиной как входной размер слова. Внутренний интегратор и этапы расчески используют тип данных полной точности с 25 битами.

Когда вы устанавливаете параметр Output data type на Minimum section word lengths и параметр Output word length к 16, блок выходные данные с размером слова 16. В этом случае блок изменяет битную ширину на каждом этапе, на основе алгоритма Сокращения.

Если значение параметров Output word length меньше количества битов, требуемых в блоке выход, младшие значащие биты (LSBs) в более ранних стадиях сокращены. Количество LSBs, чтобы отбросить на каждом этапе обеспечивается в алгоритме Hogenauer [1]. Этот алгоритм минимизирует потерю информации в выходных данных.

Этот раздел показывает задержки блока, когда управляется с фиксированными и переменными уровнями децимации.

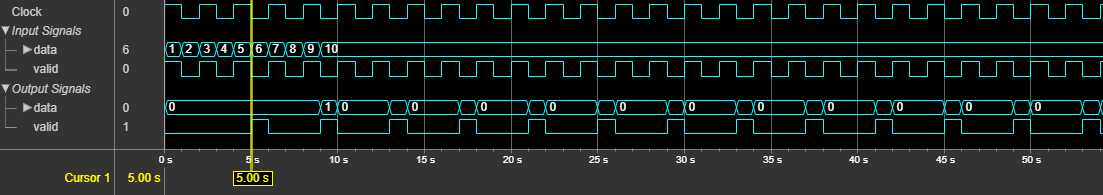

Этот рисунок показывает выход блока для настройки по умолчанию, то есть, фиксируемой ставки децимации с R, M и значениями N 2, 1, и 2, соответственно. Блок возвращает допустимые выходные данные в каждом втором цикле на основе фиксированного значения Decimation factor (R) 2. Задержка блока является 5 тактами и вычисляется как 3 + N.

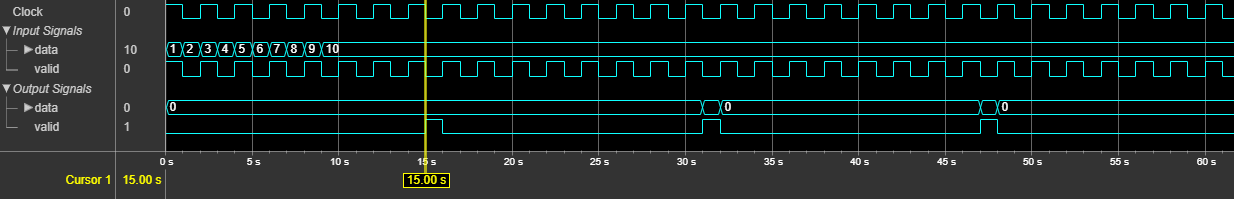

Этот рисунок показывает выход блока для фиксированной децимации с R, M и значениями N 8, 1, и 3, соответственно, и выбранным параметром Gain correction. Блок возвращает допустимые выходные данные в каждом восьмом цикле на основе фиксированного значения Decimation factor (R) 8. Задержка блока является 15 тактами и вычисляется как 3 + N + 9.

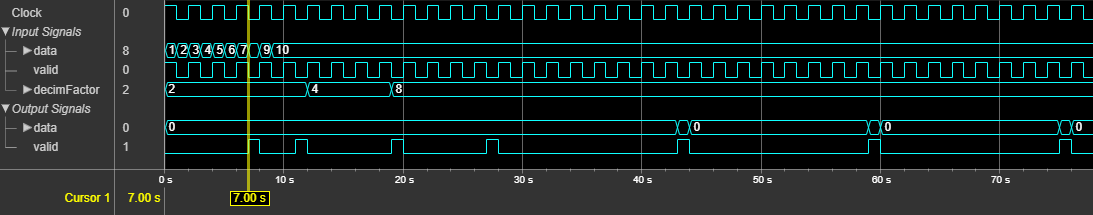

Этот рисунок показывает выход блока для переменной децимации (decimFactor) значения входного порта 2, 4, и 8 и M и значения N 1 и 3, соответственно. В этом случае параметр Gain correction очищен. Блок возвращает допустимые выходные данные во втором, четвертом, и восемь циклов, соответствующих значениям порта decimFactor 2, 4, и 8, соответственно. Блок признает, что значение порта decimFactor изменяется только, когда входным портом valid является 1Задержка.The блока является 7 тактами и вычисляется как 4 + N.

Производительность синтезируемого HDL-кода меняется в зависимости от вашей цели и опций синтеза. Эта таблица показывает результаты синтеза данных ресурсов и данных о производительности блока с фиксированными и переменными уровнями децимации, когда R, M и значения N равняются 2, 1, и 2, соответственно. Сгенерированный HDL предназначен на оценочную плату Xilinx® Zynq®-7000 ZC706.

| Тип децимации | Срез LUTs | Регистры среза | Максимальная частота в МГц |

|---|---|---|---|

| Фиксированная процентная ставка | 101 | 166 | 711.74 |

| Плавающий курс | 206 | 186 | 441.70 |

Ресурсы и частоты варьируются на основе R, M, и значений N и других значений параметров, выбранных в маске блока.

[1] Hogenauer, E. “Экономичный Класс Цифровых фильтров для Децимации и Интерполяции”. Транзакции IEEE на Акустике, Речи и издании 29 Обработки сигналов, № 2, апрель 1981, стр 155–162.

Этот блок поддерживает генерацию кода C/C++ для акселератора Simulink® и быстрых режимов Accelerator и для генерации компонента DPI.

HDL Coder™ обеспечивает дополнительные параметры конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

dsp.CICCompensationDecimator | dsp.CICCompensationInterpolator | dsp.CICDecimator | dsp.CICInterpolator | dsp.HDLCICDecimation1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.