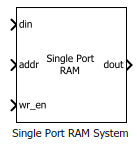

Один блок Port RAM на основе hdl. Системный объект RAM со способностью ввести начальное значение

HDL Coder / RAM HDL

Блоки являются блоками MATLAB System, которые используют hdl.RAM Система object™. Можно задать тип RAM как Dual port, Simple dual port, или Single port. В терминах поведения симуляции блок Single Port RAM System ведет себя похожий на Single Port RAM.

При помощи реализации блока MATLAB System вы можете:

Задайте начальное значение для RAM. В диалоговом окне Block Parameters введите значение для Specify the RAM initial value.

Получите более быстрые результаты симуляции, когда вы будете использовать эти блоки в своей модели Simulink®.

Создайте параллельные банки RAM, когда вы будете использовать векторные данные путем усиления hdl.RAM Функциональность системного объекта.

Получите более высокую производительность и поддержку больших памятей данных.

Блок не поддерживает boolean входные параметры. Бросьте любой boolean типы к ufix1 для входа с блоком.

Когда вы создаете поток битов FPGA для RAM, глобальная логика сброса не сбрасывает содержимое RAM. Чтобы сбросить RAM, убедитесь, что вы реализуете логику сброса.

Адресом RAM может быть любой fixed-point (fi) или integer, должно быть без знака, и должен быть между 2 и 31 биты долго.