Когда вы задаете свой пользовательский исходный проект, можно опционально использовать свойства в hdlcoder.ReferenceDesign объект задать пользовательские параметры и функции обратного вызова.

Этот код MATLAB® показывает, как задать пользовательские параметры и указать указатель на функцию пользовательских функций обратного вызова в функции определения исходного проекта.

function hRD = plugin_rd() % Reference design definition % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'My Reference Design'; hRD.BoardName = 'ZedBoard'; % Tool information hRD.SupportedToolVersion = {'2018.3'}; %% Add custom design files % ... % ... %% Add optional custom parameters by using addParameter property. % Specify custom 'DUT path' and 'Channel Mapping' parameters. % The parameters get populated in the 'Set Target Reference Design' % task of the HDL Workflow Advisor. hRD.addParameter( ... 'ParameterID', 'DutPath', ... 'DisplayName', 'Dut Path', ... 'DefaultValue', 'Rx', ... 'ParameterType', hdlcoder.ParameterType.Dropdown, ... 'Choice', {'Rx', 'Tx'}); hRD.addParameter( ... 'ParameterID', 'ChannelMapping', ... 'DisplayName', 'Channel Mapping', ... 'DefaultValue', '1'); %% Enable JTAG MATLAB as AXI Master IP Insertion. The IP % insertion setting is visible in the 'Set Target Reference Design' % task of the HDL Workflow Advisor. By default, the % AddJTAGMATLABasAXIMasterParameter property is set to 'true'. hRD.AddJTAGMATLABasAXIMasterParameter = 'true'; hRD.JTAGMATLABasAXIMasterDefaultValue = 'on'; %% Add custom callback functions. These are optional. % With the callback functions, you can enable custom % validations, customize the project creation, software % interface model generation, and the bistream build. % Register the function handle of these callback functions. % Specify an optional callback for 'Set Target Reference Design' % task in Workflow Advisor. Use property name % 'PostTargetReferenceDesignFcn'. hRD.PostTargetReferenceDesignFcn = ... @my_reference_design.callback_PostTargetReferenceDesign; % Specify an optional callback for 'Set Target Interface' task in Workflow Advisor. % Use the property name 'PostTargetInterfaceFcn'. hRD.PostTargetInterfaceFcn = ... @my_reference_design.callback_PostTargetInterface; % Specify an optional callback for 'Create Project' task % Use the property name 'PostCreateProjectFcn' for the ref design object. hRD.PostCreateProjectFcn = ... @my_reference_design.callback_PostCreateProject; % Specify an optional callback for 'Generate Software Interface Model' task % Use the property name 'PostSWInterfaceFcn' for the ref design object. hRD.PostSWInterfaceFcn = ... @my_reference_design.callback_PostSWInterface; % Specify an optional callback for 'Build FPGA Bitstream' task % Use the property name 'PostBuildBitstreamFcn' for the ref design object. hRD.PostBuildBitstreamFcn = ... @my_reference_design.callback_PostBuildBitstream; % Specify an optional callback for 'Program Target Device' % task to use a custom programming method. hRD.CallbackCustomProgrammingMethod = ... @my_reference_design.callback_CustomProgrammingMethod; %% Add interfaces % ... % ...

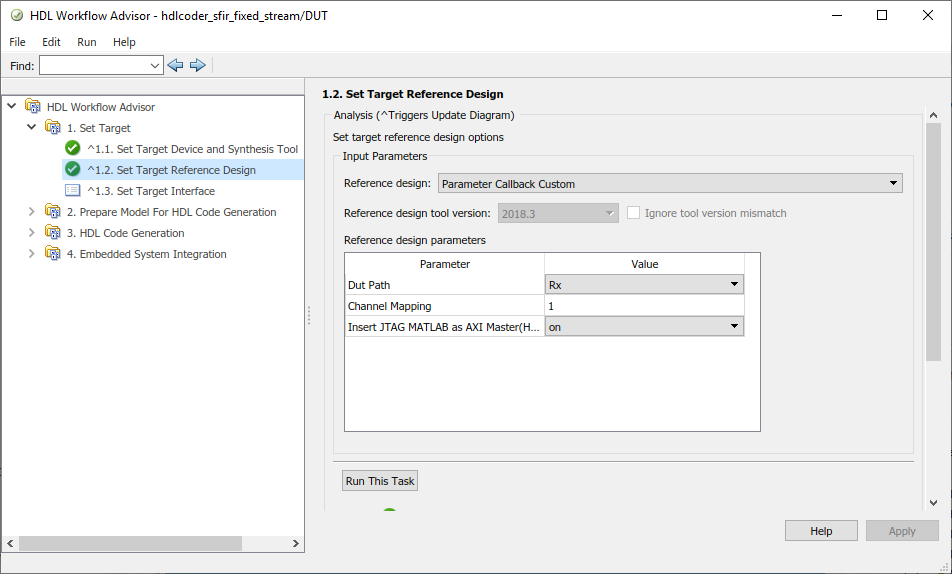

С addParameter метод hdlcoder.ReferenceDesign класс, можно задать пользовательские параметры. В предыдущем примере кода исходный проект задает два пользовательских параметра, DUT Path и Channel Mapping. Узнать больше о addParameter метод, смотрите addParameter.

По умолчанию HDL Coder™ добавляет параметр Insert JTAG MATLAB as AXI Master (HDL Verifier Required) во все исходные проекты. Когда вы устанавливаете этот параметр на on, генератор кода автоматически вводит MATLAB JTAG Ведущий IP AXI в ваш исходный проект. При помощи MATLAB JTAG Ведущий IP AXI можно легко получить доступ к регистрам AXI в сгенерированном ядре IP DUT на плате FPGA от MATLAB до связи JTAG. См. также Настроенный для MATLAB Ведущее устройство AXI (HDL Verifier).

Чтобы использовать эту возможность, у вас должны быть пакеты аппаратной поддержки HDL Verifier™, установленные и загруженные. Смотрите Пакет поддержки плат FPGA Загрузки (HDL Verifier).

Генератор кода настраивает AXI4 Slave ID Width, чтобы разместить MATLAB как Ведущее IP-соединение AXI. После того, как вы сгенерируете ядро IP HDL и создадите проект исходного проекта, можно открыть блочную конструкцию Vivado®, чтобы видеть MATLAB JTAG Ведущий IP AXI, вставленный в исходный проект.

В коде предыдущего примера исходный проект задает AddJTAGMATLABasAXIMasterParameter и JTAGMATLABasAXIMasterDefaultValue свойства hdlcoder.ReferenceDesign класс. Эти свойства управляют поведением по умолчанию установки Insert JTAG MATLAB as AXI Master (HDL Verifier Required) в задаче Set Target Reference Design HDL Workflow Advisor. Если вы не задаете ни одного из этих свойств в hdlcoder.ReferenceDesign класс, параметр Insert JTAG MATLAB as AXI Master (HDL Verifier Required) отображен в задаче Set Target Reference Design, и значение установлено к off. Этот пример кода иллюстрирует поведение по умолчанию.

%% Default behavior of Insert JTAG as AXI Master option % This parameter controls visibility of the option in % 'Set Target Reference Design Task' of HDL Workflow Advisor % By default, the parameter value is set to 'true', % which means that the option is displayed in the UI. If % you do not want the parameter to be displayed, set this % value to 'false'. hRD.AddJTAGMATLABasAXIMasterParameter = 'true'; % This parameter controls the value of the option in the % the 'Set Target Reference Design Task' task. By default, % the value is 'off', which means that the parameter is % displayed in the task and the value is off. To enable % automatic insertion of JTAG AXI Master IP in the reference % design, set this value to 'on'. In that case, the % AddJTAGMATLABasAXIMasterParameter must be set to 'true'. hRD.JTAGMATLABasAXIMasterDefaultValue = 'off';

Для примеров см.:

Когда вы открываете HDL Workflow Advisor, HDL Coder заполняет задачу Set Target Reference Design с именем исходного проекта, версией инструмента, пользовательские параметры, которые вы задали, и набор опции Insert JTAG MATLAB as AXI Master (HDL Verifier Required) к on.

HDL Coder затем передает эти значения параметров функциям обратного вызова во входной структуре.

Если вашим инструментом синтеза является Xilinx® Vivado, HDL Coder устанавливает значения параметров исходного проекта на переменные. Переменные затем вводятся к блочной конструкции файл Tcl. Этот фрагмент кода является примером от создания проекта исходного проекта файл Tcl.

update_ip_catalog

set DutPath {Rx}

set ChannelMapping {1}

source vivado_custom_block_design.tcl

Код показывает, как HDL Coder устанавливает параметры исходного проекта прежде, чем получить файл Tcl проекта пользовательского блока.

В определении исходного проекта можно указать указатель на функцию, чтобы сослаться на пользовательские функции обратного вызова. Вы затем можете:

Включите пользовательские валидации.

Настройте исходный проект динамически.

Настройте настройки создания проекта исходного проекта.

Измените модель интерфейса сгенерированного программного обеспечения.

Настройте процесс сборки потока битов FPGA.

Задайте пользовательский метод программирования FPGA.

С hdlcoder.ReferenceDesign класс, можно задать имена свойства коллбэка. Свойства коллбэка имеют соглашение о присвоении имен. Функции обратного вызова могут иметь любое имя. В HDL Workflow Advisor можно задать функции обратного вызова, чтобы настроить эти задачи.

| Советник по вопросам рабочего процесса задача | Имя свойства коллбэка | Функциональность |

|---|---|---|

Установите целевой исходный проект |

|

|

Установите целевой интерфейс | PostTargetInterfaceFcn | Включите пользовательские валидации. Для примера, который показывает, как можно подтвердить не выбор определенного интерфейса для определенной пользовательской установки параметра, смотрите |

Создайте проект | PostCreateProjectFcn | Задайте пользовательские настройки, когда HDL Coder создаст проект. Для примера смотрите |

Сгенерируйте модель программного интерфейса | PostSWInterfaceFcn | Измените модель интерфейса сгенерированного программного обеспечения. Для примера смотрите |

Создайте поток битов FPGA | PostBuildBitstreamFcn | Задайте пользовательские настройки, когда вы создадите поток битов FPGA. Для примера смотрите |

Целевое устройство программы | CallbackCustomProgrammingMethod | Задайте пользовательский метод программирования FPGA. Для примера смотрите |

Для каждой функции обратного вызова, которую вы хотите, чтобы HDL Coder выполнил после выполнения задачи, создайте файл, который задает функцию MATLAB с любым именем.

Убедитесь, что функция обратного вызова имеет зарегистрированные аргументы ввода и вывода.

Проверьте, что функции доступны от пути MATLAB.

Укажите указатель на функцию функций обратного вызова в функции определения исходного проекта.

Следуйте соглашениям о присвоении имен для имен свойства коллбэка.

Чтобы узнать больше об этих функциях обратного вызова, смотрите hdlcoder.ReferenceDesign.

hdlcoder.Board | hdlcoder.ReferenceDesign