HDL Coder™ поддерживает несколько оптимизации, реализаций блока и опций, которые вводят дискретные задержки в модель, с целью более эффективного аппаратного использования или достижения более высоких тактовых частот. Примеры включают:

Оптимизация: Оптимизация такой, как выведено конвейеризация, потоковая передача или разделение ресурсов может ввести задержки.

Расположение каскадом: Некоторые блоки поддерживают каскадные реализации, которые вводят цикл задержки сгенерированного кода.

Реализации блока: Некоторые реализации блока, такие как архитектура Ньютона-Raphson по сути вводят задержки сгенерированного кода.

Когда оптимизация или опции реализации блока вводят задержки вдоль критического пути в модели, численных данных исходной модели и сгенерированной модели, или HDL-код может отличаться, потому что эквивалентные задержки не введены на другом, параллельны путям прохождения сигнала. Ручная вставка компенсации задержек вдоль других путей возможна, но подвержена ошибкам и не масштабируется хорошо к большим моделям со многими путями прохождения сигнала или несколькими частотами дискретизации.

Чтобы помочь вам решить эту задачу, HDL Coder поддерживает delay balancing. По умолчанию задержитесь, балансировка включена на модели. Генератор кода обнаруживает введение новых задержек вдоль одного пути, и затем вставляет соответствие с задержками на других путях. Когда балансировка задержки включена, сгенерированная модель функционально эквивалентна исходной модели. Не рекомендуется, чтобы вы отключили задержку, балансирующуюся на модели. Если вы отключаете эту установку, HDL Coder генерирует предупреждение, что числовые различия могут произойти в модели валидации. Чтобы зафиксировать это предупреждение, включите Balance delays на модели или запустите установку балансировки задержки Проверки проверки модели.

Можно установить задержку, балансирующуюся для целой модели. Для более прекрасного управления можно также установить задержку, балансирующуюся для подсистем в подсистеме DUT верхнего уровня.

Используйте следующий makehdl свойства установить задержку, балансирующуюся для модели:

BalanceDelays: По умолчанию балансировка задержки уровня модели включена, и подсистемы в модели наследовали установку уровня модели. Чтобы изучить, как установить задержку, балансирующуюся для модели, смотрите задержки Баланса.

GenerateValidationModel: По умолчанию генерация модели валидации отключена. Когда вы включаете балансировку задержки, генерируете модель валидации, чтобы просмотреть задержки и другие различия между вашей исходной моделью и сгенерированной моделью. Чтобы изучить, как включить генерацию модели валидации, смотрите Сгенерировать раздел модели валидации в Генерации Модели для HDL-кода.

Например, следующие команды генерируют HDL-код с балансировкой задержки и генерируют модель валидации.

dut = 'ex_rsqrt_delaybalancing/Subsystem'; makehdl(dut,'BalanceDelays','on','GenerateValidationModel','on');

Можно отключить задержку, балансирующуюся для целой модели, или отключить подсистему в подсистеме DUT верхнего уровня. Например, если вы не хотите балансировать задержки пути к управлению, можно поместить путь к управлению в подсистему и отключить задержку, балансирующуюся для той подсистемы.

Чтобы отключить задержку, балансирующуюся для подсистемы в подсистеме DUT верхнего уровня, отключите задержку, балансирующуюся на уровне модели. Когда вы отключаете задержку, балансирующуюся для модели, модель валидации не компенсирует задержку, вставленную в сгенерированную модель из-за оптимизации, или блокирует реализации. Модель валидации может поэтому показать несоответствия между исходной моделью и сгенерированной моделью.

Отключить задержку, балансирующуюся для подсистемы в подсистеме DUT верхнего уровня:

Отключите задержку, балансирующуюся для модели.

Включите задержку, балансирующуюся для подсистемы DUT верхнего уровня.

Отключите задержку, балансирующуюся для подсистемы в подсистеме DUT.

Чтобы изучить, как установить задержку, балансирующуюся для подсистемы, смотрите, что Задержка Набора Балансируется Для Подсистемы.

Если балансировка задержки неудачна, hdlcoder.optimizeDesign не может оптимизировать сгенерированный HDL-код.

Следующие блоки и подсистемы не поддерживают балансировку задержки:

Triggered Subsystem

Atomic Subsystem

HDLCosimulation

Data Type Duplicate

Decrement To Zero

Frame Conversion

Ground

FFT HDL Optimized

LMS Filter

Model Reference

To VCD File

Magnitude-Angle to Complex

Следующие реализации блока не поддерживают балансировку задержки:

hdldefaults. ConstantSpecialHDLEmission

hdldefaults. NoHDL

HDL Coder не поддерживает балансировку задержки, если:

Существует несколько экземпляров Atomic Subsystem в различных условных подсистемах.

В диалоговом окне Block Parameters Atomic Subsystem можно установить Function packaging на Nonreusable function.

Свойство блока BalanceDelays для всех экземпляров Atomic Subsystem или Model Reference решает к различному значению.

Чтобы зафиксировать эту ошибку, отключите BalanceDelays для всех экземпляров Atomic Subsystem или Model Reference.

Блок в условной подсистеме и имеет конвейерные задержки.

Подсистема с BlackBox

Architecture имеет набор свойств блока ImplementationLatency к отрицательной величине.

Чтобы зафиксировать эту ошибку, для ImplementationLatency, вводят неотрицательное целое число.

HDL Coder не поддерживает балансировку задержки, если:

Задержки введены в обратной связи, и HDL Coder не может сбалансировать задержки пути. Например, если вы применяете конвейеризацию тактовой частоты в обратной связи, HDL Coder вводит задержку на тактовой частоте и может заставить задержку, балансирующуюся перестать работать.

Чтобы сократить количество задержек тактовой частоты, увеличьте фактор Сверхдискретизации.

Шаг расчета не дискретен, или отношение шагов расчета самого быстрого к самому медленному уровню является слишком большим.

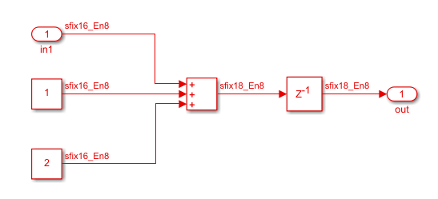

Когда у вас есть блоки Constant как входные параметры в Подсистеме DUT, для которой включена балансировка задержки, вы видите, что начальная симуляция не сочетается в модели валидации. Рассмотрите эту модель в Подсистеме DUT. Блок Constant, который выводит значение 1 имеет набор свойства OutputPipeline блока HDL к 1 .

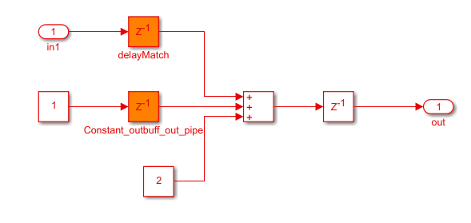

Этот рисунок отображает сгенерированную модель валидации. Вы видите, что балансировка задержки добавила соответствующую задержку с входным портом, чтобы сбалансировать конвейерный регистр, вставленный для блока Delay. Генератор кода не вставляет соответствующую задержку на параллельном пути, содержащем блок Constant со значением 2 потому что выходное значение блока является константой. Эта задержка не вставленные результаты в начальном несоответствии симуляции

Чтобы разрешить несоответствие симуляции, в модели валидации, вручную добавляют соответствующую задержку при выходе блока Constant со значением 2.

Чтобы видеть, что задержка балансирует информацию в отчете, прежде чем вы сгенерируете код для каждой подсистемы или модели - ссылки, включают отчет оптимизации. Чтобы включить этот отчет, во вкладке HDL Code, выбирают Report Options, и затем выбирают Generate optimization report.

Когда вы генерируете код для каждой подсистемы, модели - ссылки или блока MATLAB Function, HDL Coder представляет отчет оптимизации. В отчете выберите раздел Delay Balancing отчета.

Отчет Балансировки Задержки показывает изменения задержки, конвейерную задержку и задержку фазы в выходных портах и количество конвейеров, добавленных в выходных портах, чтобы совпадать с задержками. Если балансировка задержки перестала работать, отчет упоминает критерии, который был нарушен и отображает ссылку на любой блок или подсистему, которая заставила задержку, балансирующуюся перестать работать.