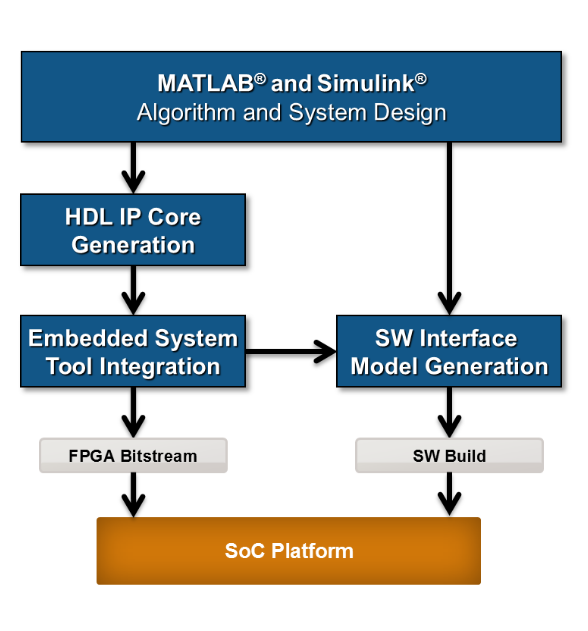

Рабочий процесс элемента кода аппаратного программного обеспечения HDL Coder™ помогает автоматизировать развертывание вашего MATLAB® и проекта Simulink® на платформу Zynq®-7000 или платформу Intel® SoC. Можно исследовать лучшие способы разделить и развернуть проект путем итерации через следующий рабочий процесс.

MATLAB и Алгоритм Simulink и Разработка системы: Вы начинаете путем реализации проекта в MATLAB или Simulink. Когда поведение проекта удовлетворяет ваши требования, решите, как разделить ваш проект: какие части вы хотите запустить в оборудовании, и какие части вы хотите запустить во встроенном программном обеспечении.

Часть проекта, который вы хотите запустить в оборудовании, должна использовать синтаксис MATLAB или блоки Simulink, которые поддерживаются и сконфигурированный для генерации HDL-кода. См.:

Генерация Ядра IP HDL: Заключите аппаратную часть своего проекта в атомарном блоке Subsystem или функции MATLAB, и используйте HDL Workflow Advisor, чтобы задать и сгенерировать ядро IP HDL.

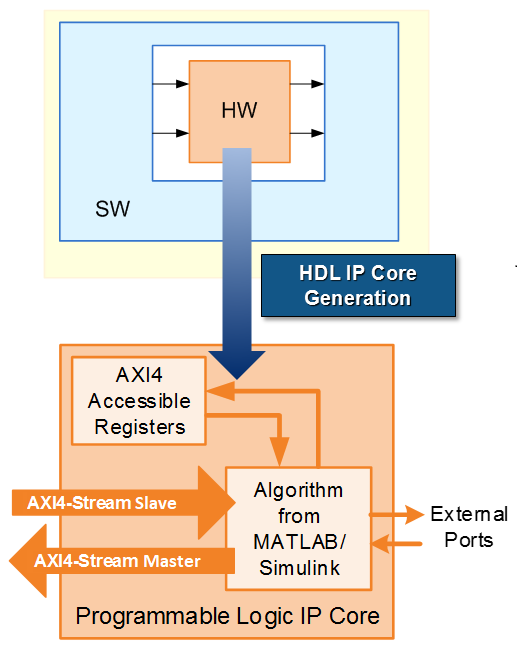

Следующая схема показывает проект, который был разделен в аппаратную часть, в оранжевой, и программной части, в синем. Генерация ядра IP HDL создает ядро IP из аппаратной части модели. Ядро IP включает компоненты аппаратного интерфейса, такие как AXI4 доступные регистры, AXI4 или AXI4-облегченные интерфейсы, AXI4-поток или AXI4-потоковые Видеоинтерфейсы, Ведущие интерфейсы AXI4 и внешние порты.

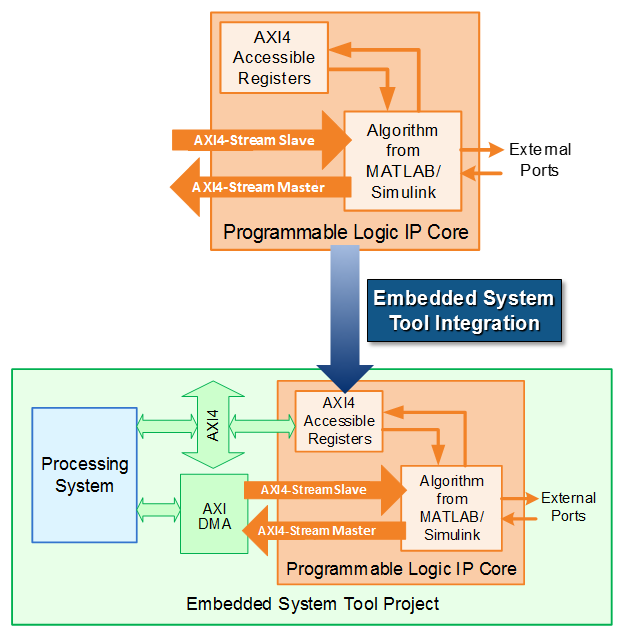

Интеграция средств Встраиваемой системы: Как часть рабочего процесса генерации ядра IP HDL Workflow Advisor, вы вставляете свое сгенерированное ядро IP в исходный проект и генерируете поток битов FPGA для оборудования SoC.

Исходный проект является предопределенным проектом интегрирования встраиваемой системы. Это содержит все элементы, программное обеспечение Intel или Xilinx® должно развернуть ваш проект в платформу SoC, за исключением пользовательского IP базовое и встроенное программное обеспечение, которое вы генерируете.

Следующая схема иллюстрирует отношение между исходным проектом, в зеленом, и сгенерированным ядром IP, в оранжевом.

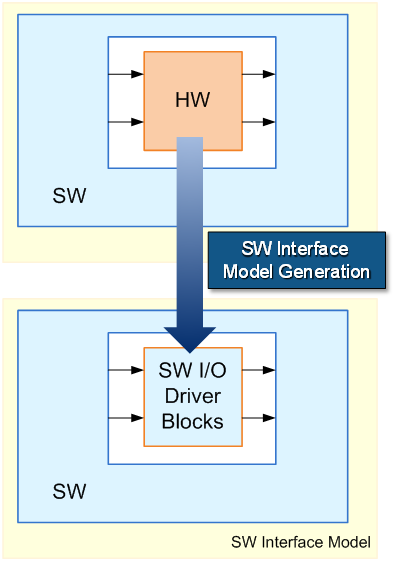

Генерация Интерфейса SW Модели (требует лицензии Simulink и лицензии Embedded Coder®): В HDL Workflow Advisor, после того, как вы сгенерируете ядро IP и вставите его в исходный проект, можно опционально сгенерировать модель программного интерфейса. Модель программного интерфейса является вашей исходной моделью с блоками драйверов AXI, заменяющими аппаратную часть.

Если у вас есть лицензия Embedded Coder, можно автоматически сгенерировать модель программного интерфейса, сгенерировать встроенный код от нее, и создать и запустить исполняемый файл на ядре Linux® на процессоре ARM®. Сгенерированное встроенное программное обеспечение включает код драйвера AXI, сгенерированный от блоков драйверов AXI, который управляет ядром IP HDL.

Если у вас нет лицензии Embedded Coder или лицензии Simulink, можно записать встроенное программное обеспечение и вручную создать его для процессора ARM.

Следующая схема показывает различие между исходной моделью и моделью программного интерфейса.

Платформа SoC и Режим external mode PIL: Используя HDL Workflow Advisor, вы программируете свой поток битов FPGA на платформу SoC. Можно затем запустить модель программного интерфейса в режиме external mode или процессор в режиме (PIL) цикла, чтобы протестировать развернутый проект.

Если ваш развернутый проект не соответствует вашим конструктивным требованиям, можно повторить рабочий процесс с модифицированной моделью или различный раздел аппаратного программного обеспечения.