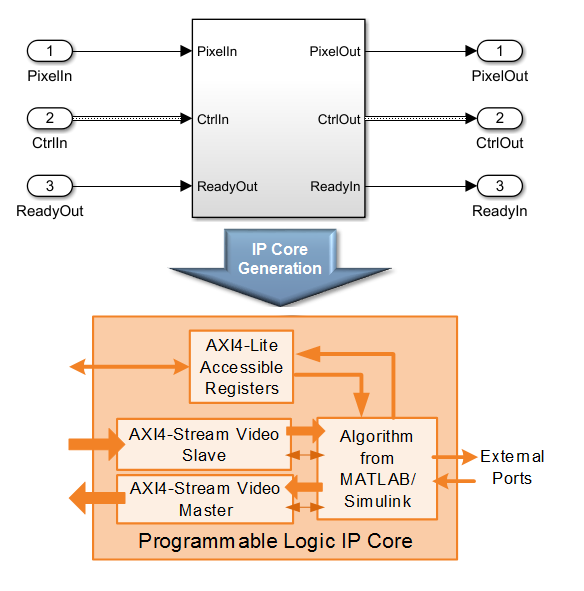

С программным обеспечением HDL Coder™ можно реализовать упрощенный, передающий потоком пиксельный протокол в модели. Программное обеспечение генерирует ядро IP HDL с AXI4-потоковыми Видеоинтерфейсами.

Можно использовать пиксельный протокол потоковой передачи в AXI4-потоковом отображении Видеоинтерфейса. Видео алгоритмы обрабатывают данные последовательно и генерируют видеоданные как последовательный поток пиксельных данных и управляющих сигналов. Чтобы узнать о пиксельном протоколе потоковой передачи, смотрите Пиксельный Интерфейс Потоковой передачи (Vision HDL Toolbox).

Чтобы сгенерировать ядро IP с AXI4-потоковыми Видеоинтерфейсами, в вашем интерфейсе DUT, реализуют эти сигналы:

Пиксельные данные

Пиксельная шина управления

Пиксельная Шина управления является шиной, которая имеет эти сигналы:

hStart

hEnd

vStart

vEnd

valid

Сигналы hStart и hEnd представляют запуск активной линии и конец активной линии соответственно. Сигналы vStart и продают, представляют запуск системы координат и конец системы координат.

Можно опционально смоделировать сигнал противодавления, Готовый, и сопоставить его с AXI4-потоковым Видеоинтерфейсом.

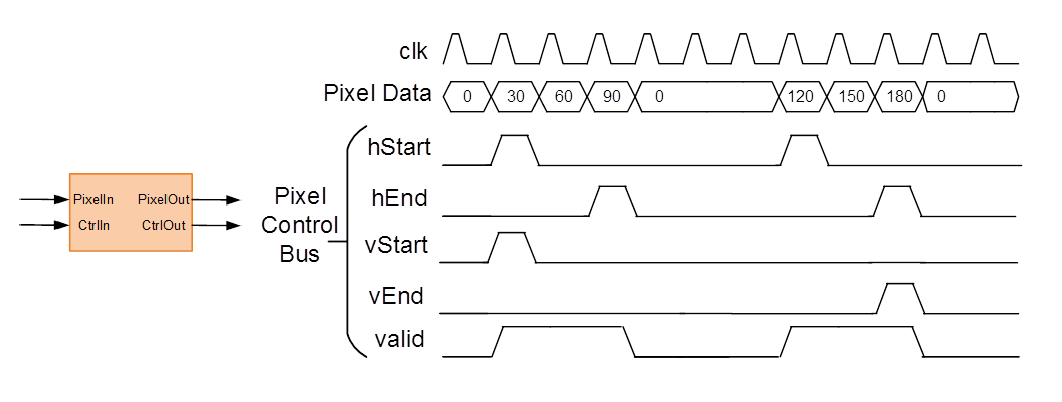

Этот рисунок 2 3 пиксельное изображение. Областью активного изображения является прямоугольник с пунктирной линией вокруг этого и неактивными пикселями, которые окружают его. Пиксели помечены своими полутоновыми значениями.

![]()

Этот рисунок показывает схему синхронизации для Пиксельных данных, и Пиксельная Шина управления сигнализирует, что вы моделируете в интерфейсе DUT.

Сигнал Пиксельных данных является первичным видеосигналом, который передается через AXI4-потоковый Видеоинтерфейс. Когда сигнал Пиксельных данных допустим, допустимый сигнал утверждается.

Сигнал hStart становится высоким в начале активных линий. Сигнал hEnd становится высоким в конце активных линий.

Сигнал vStart становится высоким в начале активной системы координат во второй линии. Продавать сигнал становится высоким в конце активной системы координат в третьей линии.

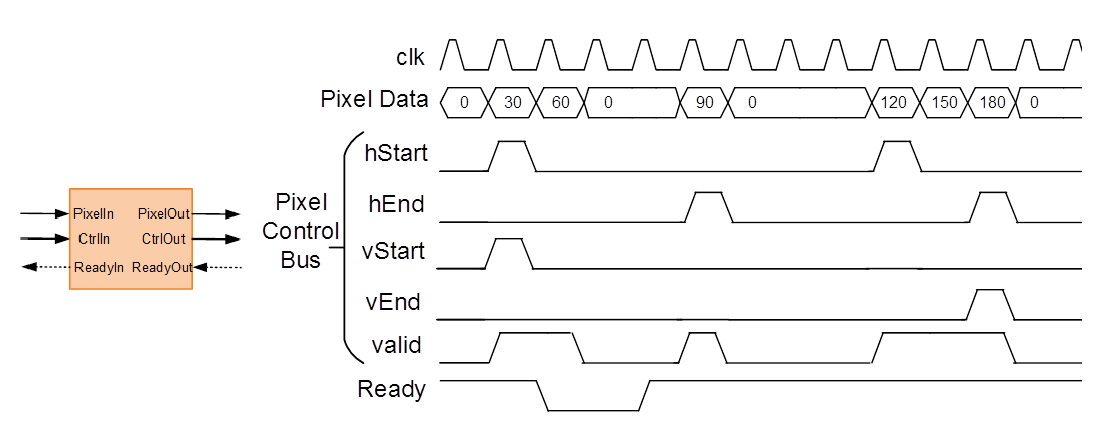

Этот рисунок показывает схему синхронизации для Пиксельных данных, Пиксельной Шины управления и Готового сигнала, что вы моделируете в интерфейсе DUT.

Когда вы сопоставляете порты DUT с AXI4-потоковым Видеоинтерфейсом, можно опционально смоделировать сигнал противодавления, Готовый, и сопоставить его с AXI4-потоковым Видеоинтерфейсом.

В интерфейсе Slave, с Готовым сигналом, можно применить противодавление. В интерфейсе Master, с Готовым сигналом, можно ответить на противодавление.

Если вы моделируете Готовый сигнал в своих AXI4-потоковых Видеоинтерфейсах, ваш интерфейс Master должен deassert его допустимый сигнал один цикл после того, как Готовый сигнал является deasserted.

Если вы не моделируете Готовый сигнал, HDL Coder генерирует связанную логику противодавления.

Можно смоделировать видео алгоритм с Пиксельными данными и Пиксельными сигналами Шины управления в портах DUT и сопоставить сигналы с AXI4-потоковыми Видеоинтерфейсами. Можно опционально смоделировать сигнал противодавления, Готовый, и сопоставить его с AXI4-потоковым Видеоинтерфейсом.

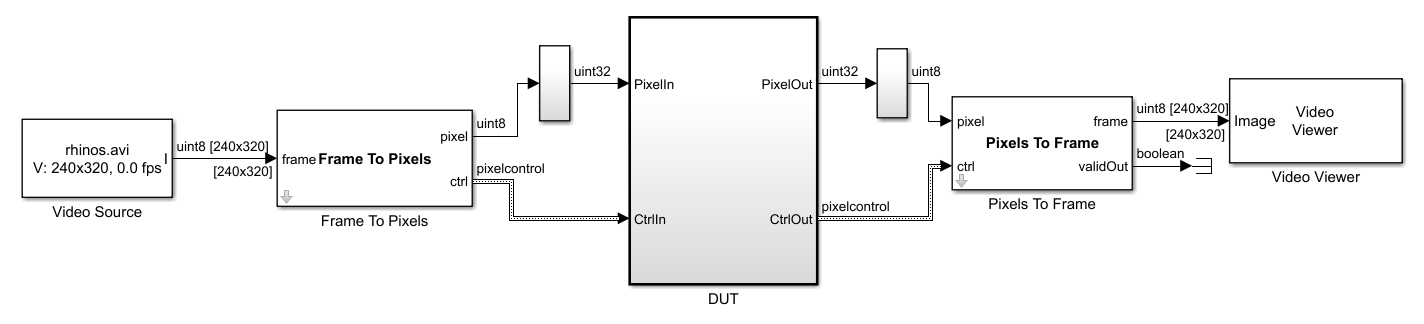

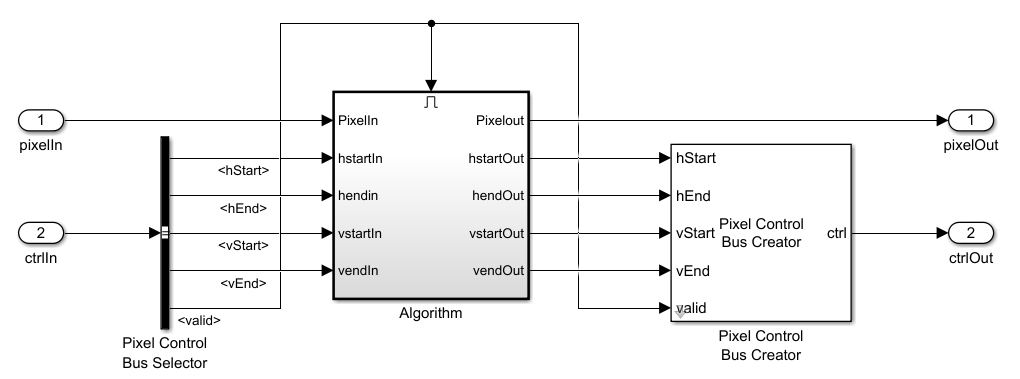

Этот рисунок показывает пример модели Simulink® верхнего уровня с входом Video Source.

Frame To Pixels и блоки Pixels To Frame выполняют преобразование между видеокадрами и Пиксельными данными и Пиксельной Шиной управления в интерфейсе DUT. Чтобы использовать эти блоки, необходимо было установить Vision HDL Toolbox™.

См. также Frame To Pixels и Pixels To Frame в документации Vision HDL Toolbox.

Этот рисунок показывает, как смоделировать Пиксельные данные и Пиксельные сигналы Шины управления в подсистеме DUT.

Можно непосредственно соединить допустимый сигнал от Пиксельной Шины управления до порта Enable. Если у вас нет программного обеспечения Vision HDL Toolbox, замените Pixel Control Bus Selector и блоки Pixel Control Bus Creator с Bus Selector и блоки Bus Creator соответственно.

AXI4-потоковые Видеоинтерфейсы в вашем DUT могут опционально включать Готовый сигнал.

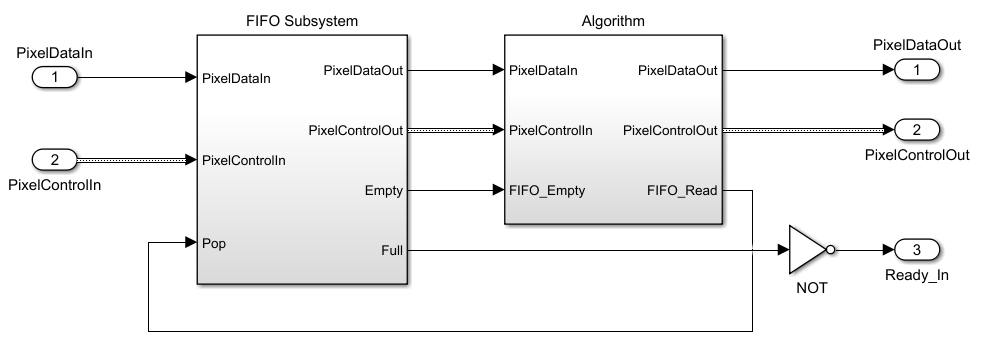

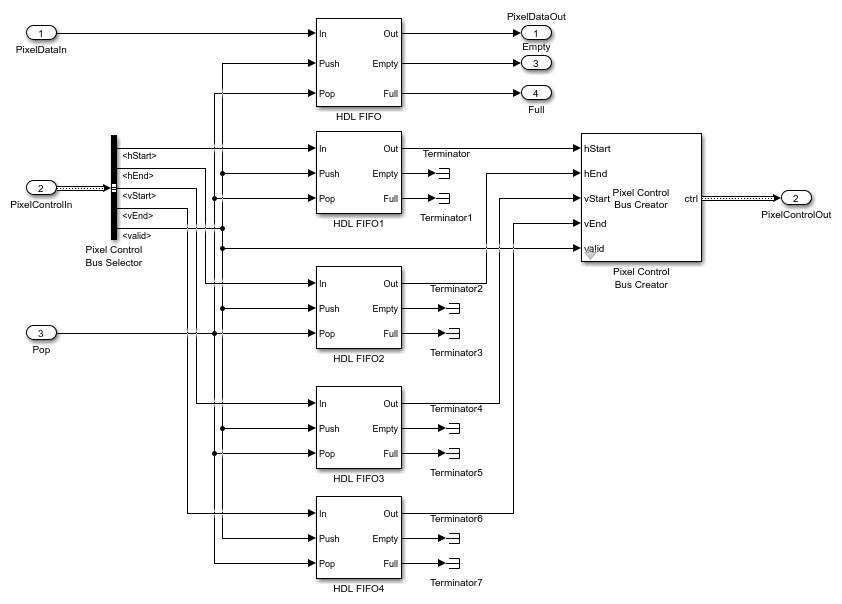

Например, у вас может быть FIFO в вашем DUT, чтобы сохранить некоторые видеоданные прежде, чем обработать сигналы. Используйте Подсистему FIFO, которая содержит блоки HDL FIFO, чтобы сохранить Пиксельные данные и Пиксельные сигналы Шины управления. Чтобы применить противодавление к восходящему компоненту, смоделируйте Готовый сигнал на основе FIFO Полный сигнал.

Этот рисунок показывает, как смоделировать Готовый сигнал в подсистеме DUT.

Блок Subsystem FIFO использует блоки HDL FIFO в Пиксельных данных и в Пиксельных сигналах Шины управления.

Отключите задержку, балансирующуюся для Готового пути прохождения сигнала. Если вы включаете балансировку задержки, кодер может вставить одну или несколько задержек на Готовом сигнале.

Когда вы запускаете IP Core Generation рабочий процесс, можно сопоставить несколько портов DUT с AXI4-потоковыми Ведущими и AXI4-потоковыми Ведомыми каналами Видео Видео. Порты DUT, сопоставленные с несколькими интерфейсными каналами, должны использовать скалярный тип данных. Когда вы используете векторные порты, можно сопоставить порты с самое большее одним AXI4-потоковым Ведущим каналом Видео и одним AXI4-потоковым Ведомым каналом Видео.

Чтобы узнать больше, Ядро seeGenerate HDL IP с Несколькими AXI4-передает-потоком и Основные Интерфейсы AXI4.

Программное обеспечение HDL Coder поддерживает проекты с несколькими частотами дискретизации, когда вы запускаете рабочий процесс Генерации Ядра IP. Когда вы сопоставляете интерфейсные порты с AXI4-потоковыми Ведущими или AXI4-потоковыми Ведомыми интерфейсами Видео Видео, чтобы использовать несколько частот дискретизации, гарантировать, что порты DUT, которые сопоставляют с этими интерфейсами AXI4, запущенными на самом быстром уровне проекта после генерации HDL-кода.

Чтобы узнать больше, смотрите Многоскоростную Генерацию Ядра IP.

Системы видеосъемки сканируют видеосигналы слева направо и сверху донизу. Когда эти системы сканируют, они генерируют неактивные интервалы между линиями и системами координат активного видео. Этот неактивный интервал называется видео подъездом. Горизонтальный подъезд состоит из неактивных циклов между концом одной линии и начало следующей строки. Вертикальный подъезд состоит из неактивных циклов между конечной активной линией одной системы координат и стартовой активной линией следующей системы координат.

Этот рисунок показывает видеокадр с горизонтальным разделением подъезда в переднюю сторону и заднее крыльцо.

![]()

AXI4-потоковый Видеоинтерфейс не требует видео подъезда, но алгоритмы Vision HDL Toolbox требуют подъезда для обработки видеопотоков. Если входящий пиксельный поток не имеет достаточного подъезда, HDL Coder вставляет необходимое количество подъезда к пиксельному потоку. При помощи AXI4-облегченных регистров в сгенерированном ядре IP можно настроить эти параметры подъезда для каждого видеокадра:

Активные пиксели на строку (Значение по умолчанию: 1920)

Активные видео линии: (Значение по умолчанию: 1080)

Горизонтальная длина подъезда (Значение по умолчанию: 280)

Вертикальная длина подъезда (Значение по умолчанию: 45)

Можно интегрировать сгенерированное ядро IP HDL с AXI4-потоковыми Видеоинтерфейсами в Default video system исходный проект.

Этот рисунок является блок-схемой Default video system архитектура исходного проекта.

Можно использовать этот Default video system архитектура исходного проекта с этими целевыми платформами:

Xilinx Zynq ZC702 evaluation kit

Xilinx Zynq ZC706 evaluation kit

ZedBoard

Использовать Default video system исходный проект, необходимо установить Пакет Поддержки Computer Vision Toolbox™ для Оборудования Xilinx® Zynq®-Based.

Когда вы сопоставляете порты DUT с AXI4-потоковыми Видеоинтерфейсами:

Порт DUT, сопоставленный с сигналом Пиксельных данных, должен использовать скалярный тип данных.

Xilinx Zynq-7000 должен быть вашей целевой платформой.

Необходимо использовать Xilinx Vivado® в качестве инструмента синтеза.

Processor/FPGA synchronization должен быть Free running.