Настройте перезаписываемую рабочую папку вне своей папки установки MATLAB®, чтобы хранить файлы, которые будут сгенерированы, когда вы завершаете свою учебную работу. Учебные инструкции принимают, что вы создаете папку hdlfilter_tutorials на диске C.

Этот пример проводит вас по шагам для разработки БИХ-фильтра, генерации кода Verilog для фильтра и проверки кода Verilog со сгенерированным испытательным стендом.

Этот раздел проводит вас по процедуре разработки и создания фильтра для БИХ-фильтра. Этот раздел принимает, что вы знакомы с интерфейсом пользователя MATLAB и Filter Designer.

Запустите программное обеспечение MATLAB.

Установите свою текущую папку на папку, в которой вы создали, Создают Папку для Ваших Учебных Файлов.

Запустите Filter Designer путем ввода filterDesigner команда в Окне Команды MATLAB. Диалоговое окно The Filter Design & Analysis Tool появляется.

В диалоговом окне Filter Design & Analysis Tool, набор следующие опции фильтра:

| Опция | Значение |

|---|---|

| Response Type | Highpass |

| Design Method | IIR Butterworth |

| Filter Order |

|

| Frequency Specifications | Модули: Fs: ФК : |

Нажмите Design Filter. Filter Designer создает фильтр для заданного проекта. Следующее сообщение появляется в строке состояния Filter Designer, когда задача завершена.

Designing Filter... Done

Для получения дополнительной информации о разработке фильтров с Filter Designer смотрите Использование Filter Designer с DSP System Toolbox Software (DSP System Toolbox).

Необходимо квантовать фильтры для генерации HDL-кода. Квантовать ваш фильтр,

Откройте БИХ-создание фильтра, которое вы создали в Проекте, БИХ Просачивается Filter Designer, если это не уже открыто.

Нажмите кнопку Set Quantization Parameters![]() на панели инструментов левой стороны. Filter Designer отображает список Filter arithmetic в нижней половине его диалогового окна.

на панели инструментов левой стороны. Filter Designer отображает список Filter arithmetic в нижней половине его диалогового окна.

Выберите Fixed-point из списка. Filter Designer отображает первую из трех панелей с вкладками его диалогового окна.

Используйте опции квантования, чтобы протестировать эффекты различных настроек на производительности и точности квантованного фильтра.

Выберите вкладку Filter Internals и установите Rounding mode на Floor и Overflow Mode к Saturate.

Нажмите Apply. Квантованный фильтр появляется следующим.

Для получения дополнительной информации о квантовании фильтров с Filter Designer смотрите Использование Filter Designer с DSP System Toolbox Software (DSP System Toolbox).

После того, как вы квантуете свой фильтр, вы готовы сконфигурировать опции кодера и сгенерировать код VHDL. Этот раздел проводит вас по запуску пользовательского интерфейса Filter Design HDL Coder™, установке опций, и генерация кода VHDL и испытательного стенда для БИХ фильтрует вас спроектированный и квантованный в Проекте, БИХ Просачивается Filter Designer и Квантует БИХ-Фильтр.

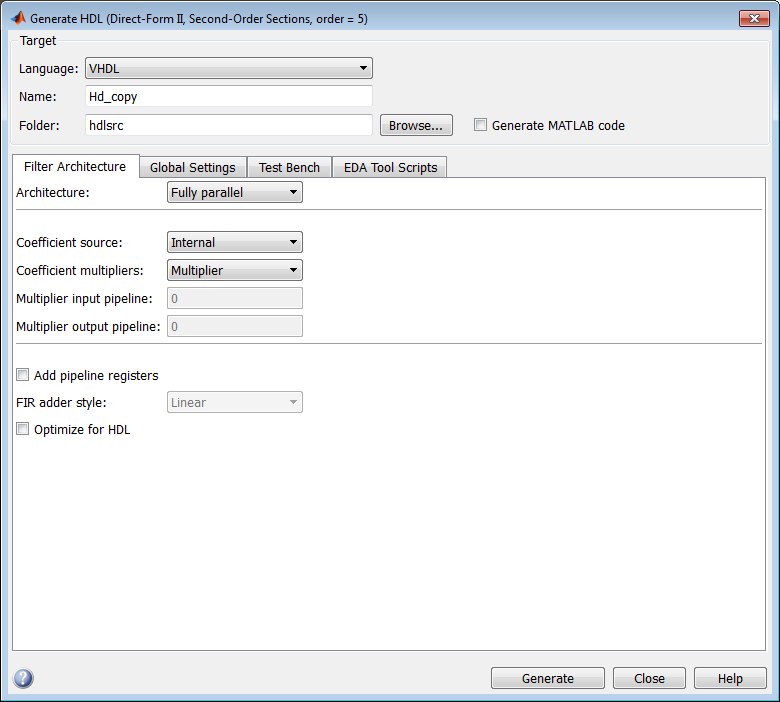

Запустите пользовательский интерфейс Filter Design HDL Coder путем выбора Targets> Generate HDL в диалоговом окне Filter Designer. Filter Designer отображает диалоговое окно Generate HDL.

В текстовом поле Name панели Target введите iir. Эта опция называет сущность VHDL и файл, который содержит код VHDL для фильтра.

Выберите вкладку Global settings пользовательского интерфейса. Затем выберите вкладку General раздела Additional settings.

В текстовом поле Comment in header введите Tutorial - IIR Filter. Кодер добавляет комментарий в конец блока комментария заголовка в каждом сгенерированном файле.

Выберите вкладку Ports. Панель Ports появляется.

Снимите флажок для опции Add output register. Панель Ports теперь появляется как в следующем рисунке.

Выберите вкладку Advanced. Панель Advanced появляется.

Выберите опцию Use 'rising_edge' for registers. Панель Advanced теперь появляется как в следующем рисунке.

Кликните по вкладке Test bench в диалоговом окне Generate HDL. В текстовом поле File name замените имя по умолчанию на iir_tb. Эта опция называет сгенерированный файл испытательного стенда.

В диалоговом окне Generate HDL нажмите Generate, чтобы запустить процесс генерации кода. Когда генерация кода завершится, нажмите OK, чтобы закрыть диалоговое окно.

Кодер отображает следующие сообщения в Окне Команды MATLAB, когда оно генерирует фильтр и файлы VHDL испытательного стенда:

### Starting VHDL code generation process for filter: iir ### Starting VHDL code generation process for filter: iir ### Generating: H:\hdlsrc\iir.vhd ### Starting generation of iir VHDL entity ### Starting generation of iir VHDL architecture ### Second-order section, # 1 ### Second-order section, # 2 ### First-order section, # 3 ### HDL latency is 1 samples ### Successful completion of VHDL code generation process for filter: iir ### Starting generation of VHDL Test Bench ### Generating input stimulus ### Done generating input stimulus; length 2172 samples. ### Generating Test bench: H:\hdlsrc\filter_tb.vhd ### Please wait ... ### Done generating VHDL Test Bench ### Starting VHDL code generation process for filter: iir ### Starting VHDL code generation process for filter: iir ### Generating: H:\hdlsrc\iir.vhd ### Starting generation of iir VHDL entity ### Starting generation of iir VHDL architecture ### Second-order section, # 1 ### Second-order section, # 2 ### First-order section, # 3 ### HDL latency is 1 samples ### Successful completion of VHDL code generation process for filter: iir

Как сообщения указывают, кодер создает папку hdlsrc под вашей текущей рабочей папкой и местами файлы iir.vhd и iir_tb.vhd в той папке.

Заметьте, что сообщения включают гиперссылки на файлы испытательного стенда и сгенерированный код. Путем нажатия на эти гиперссылки можно открыть файлы кода непосредственно в редактор MATLAB.

Сгенерированный код VHDL имеет следующие характеристики:

Сущность VHDL назвала iir.

Регистры, которые используют асинхронный сброс, когда сигнал сброса активен высокий (1).

Порты имеют следующие имена по умолчанию:

| Порт VHDL | Имя |

|---|---|

| Входной параметр | filter_in |

| Вывод | filter_out |

| Вход Clock | clk |

| Часы включают вход | clk_enable |

| Вход Reset | reset |

Вводится дополнительный регистр для обработки фильтра.

Вход часов, часы включают вход и сбросили порты, имеют тип STD_LOGIC и ввод данных и выходные порты имеют тип STD_LOGIC_VECTOR.

Коэффициенты называют coeff, где nn содействующий номер, начиная с 1.

Безопасное с точки зрения типов представление используется, когда нули конкатенированы: '0' & '0'...

Регистры сгенерированы с rising_edge функционируйте, а не оператор ELSIF clk'event AND clk='1' THEN.

Постфиксный '_process' добавлен, чтобы обработать имена.

Сгенерированный испытательный стенд:

Портативный файл VHDL.

Часы сил, часы включают и сбросили входные сигналы.

Силы часы включают входной сигнал к активному высоко.

Управляет входным сигналом часов высоко (1) в течение 5 наносекунд и низко (0) в течение 5 наносекунд.

Обеспечивает сигнал сброса для двух циклов плюс время задержки 2 наносекунд.

Применяет время задержки 2 наносекунд к сигналам ввода данных.

Для БИХ-фильтра, применяет импульс, шаг, пандус, щебет и белые шумовые типы стимула.

Познакомьтесь со сгенерированным кодом VHDL путем открытия и просматривания файла iir.vhd в ASCII или редакторе симулятора HDL.

Откройте сгенерированный файл фильтра VHDL iir.vhd.

Ищите iir. Эта линия идентифицирует модуль VHDL, с помощью значения, которое вы задали для опции Name в панели Target. Смотрите, что шаг 2 в Конфигурирует и Генерирует Код VHDL.

Ищите Tutorial. Этот раздел - то, куда кодер помещает текст, вы ввели для опции Comment in header. Смотрите, что шаг 5 в Конфигурирует и Генерирует Код VHDL.

Ищите HDL Code. Этот раздел перечисляет опции кодера, в которых вы изменили, Конфигурируют и Генерируют Код VHDL.

Ищите Filter Settings. Этот раздел кода VHDL описывает настройки создания фильтра и квантования, когда вы задали в Проекте, БИХ Просачивается Filter Designer и Квантует БИХ-Фильтр.

Ищите ENTITY. Эта линия называет сущность VHDL, с помощью значения, которое вы задали для опции Name в панели Target. Смотрите, что шаг 2 в Конфигурирует и Генерирует Код VHDL.

Ищите PORT. Этот PORT объявление задает часы фильтра, часы включают, сбрасывают, и ввод данных и выходные порты. Порты для часов, часы включают, сбрасывают, и ввод данных и выходные сигналы называют с векторами символов по умолчанию.

Ищите CONSTANT. Этот код задает коэффициенты. Их называют с помощью схемы именования по умолчанию, coeff_, где xm_sectionnx isa или bM содействующий номер и n номер раздела.

Ищите SIGNAL. Этот код задает сигналы фильтра.

Ищите input_reg_process. PROCESS имя блока input_reg_process включает PROCESS по умолчанию постфикс блока '_process'. Этот код читает вход фильтра из входного регистра. Код для этого регистра сгенерирован по умолчанию. На шаге 7 в Конфигурируют и Генерируют Код VHDL, вы очистили опцию Add output register, но оставили опцию Add input register выбранной.

Ищите IF reset. Этот код утверждает сигнал сброса. Значение по умолчанию, активное высокий (1), было задано. Также обратите внимание что PROCESS блок применяет асинхронный стиль сброса по умолчанию при генерации кода VHDL для регистров.

Ищите ELSIF. Этот код проверяет на возрастающие ребра, когда фильтр работает с регистрами. rising_edge функция используется, когда вы задали в панели Advanced диалогового окна Generate HDL. Смотрите, что шаг 10 в Конфигурирует и Генерирует Код VHDL.

Ищите Section 1. Этот раздел - то, где секция второго порядка 1 данные отфильтрована. Подобные разделы кода VHDL применяются к другой секции второго порядка и разделу первого порядка.

Ищите filter_out. Этот диск кода выходные данные фильтра.

Этот раздел объясняет, как проверить сгенерированный код VHDL для БИХ-фильтра со сгенерированным испытательным стендом VHDL. Этот пример использует средство моделирования Mentor Graphics® ModelSim® в качестве инструмента для компиляции и симуляции кода VHDL. Можно использовать другие пакеты инструмента симуляции HDL.

Чтобы проверить код фильтра, завершите следующие шаги:

Запустите свое средство моделирования. Когда вы запускаете средство моделирования Mentor Graphics ModelSim, отображение на экране, похожее на следующее, появляется.

Установите текущую папку на папку, которая содержит ваши сгенерированные файлы VHDL. Например:

cd hdlsrc

При желании создайте библиотеку проекта, чтобы сохранить скомпилированные сущности VHDL, пакеты, архитектуры и настройки. В средстве моделирования Mentor Graphics ModelSim можно создать библиотеку проекта с vlib команда.

vlib work

Скомпилируйте сгенерированный фильтр и файлы VHDL испытательного стенда. В средстве моделирования Mentor Graphics ModelSim вы компилируете код VHDL с vcom команда. Следующие команды компилируют фильтр и фильтруют код VHDL испытательного стенда.

vcom iir.vhd vcom iir_tb.vhd

Следующее отображение на экране показывает эту последовательность команды и информационные сообщения, отображенные во время компиляции.

Загрузите испытательный стенд для симуляции. Процедура для загрузки испытательного стенда варьируется в зависимости от средства моделирования, которое вы используете. В средстве моделирования Mentor Graphics ModelSim вы загружаете испытательный стенд для симуляции с vsim команда. Например:

vsim work.iir_tb

Следующее отображение показывает результаты загрузки work.iir_tb с vsim команда.

Откройте окно экрана для контроля симуляции, когда испытательный стенд запускается. В средстве моделирования Mentor Graphics ModelSim используйте следующую команду, чтобы открыть окно wave и просмотреть результаты симуляции как формы волны HDL.

add wave *

Следующие отображения окна wave.

Чтобы начать запускать симуляцию, дайте команду симуляции запуска для своего средства моделирования. Например, в средстве моделирования Mentor Graphics ModelSim, можно начать симуляцию с run команда.

Следующее отображение показывает run -all команда, используемая, чтобы запустить симуляцию.

Когда ваша симуляция испытательного стенда запускается, см. за сообщениями об ошибке. Если сообщения об ошибке появляются, интерпретируют их, когда они принадлежат вашему созданию фильтра и опциям генерации HDL-кода, вы выбрали. Определите, ожидаются ли результаты на основе индивидуальных настроек, которые вы задали при генерации кода VHDL фильтра.

Предупреждающие сообщения то примечание Time: 0 ns в предыдущем отображении не ошибки, и можно проигнорировать их.

Сообщение отказа, которое появляется в предыдущем отображении, не отмечает ошибка. Если сообщение включает textTest Complete, испытательный стенд выполнение до завершения, не сталкиваясь с ошибкой. Failure часть сообщения связывается к механизму что использование кодера, чтобы закончить симуляцию.

Следующее окно wave показывает результаты симуляции формами волны HDL.