Откройте FPGA в мастере цикла путем выбора одного из следующих методов вызова:

В окне команды MATLAB введите следующее:

>> filWizard

В панели инструментов Simulink®, на вкладке Apps, под Code Verification, Validation and Test нажимают FIL Wizard.

Чтобы восстановить предыдущий сеанс, используйте эту команду:

filWizard('./Subsystem_fil/Subsystem_fil.mat')

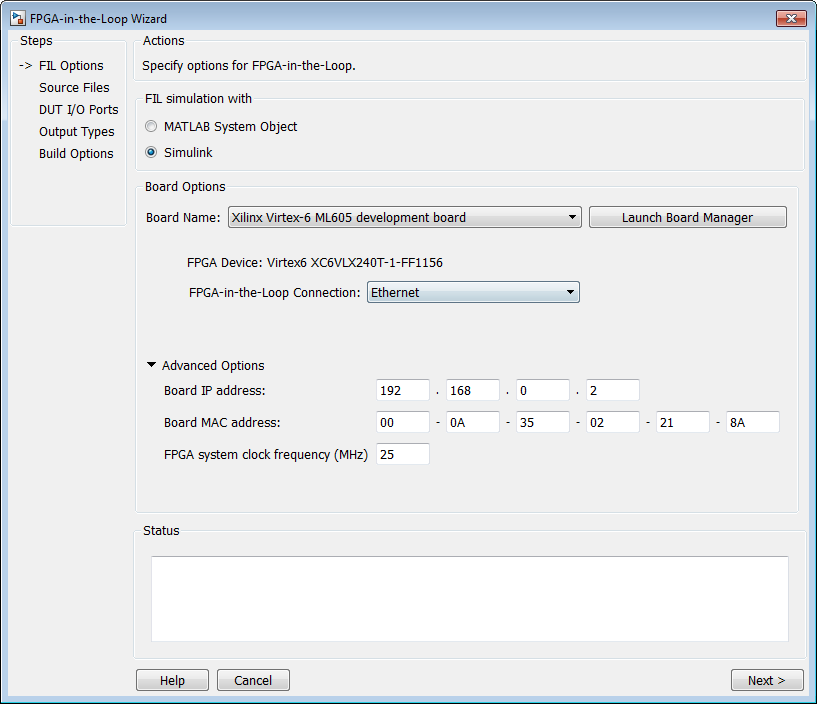

На странице FIL Options:

FIL Simulation: выберите Simulink.

Board Name: Выберите макетную плату FPGA. Если вы еще не загрузили пакет поддержки плат FPGA HDL Verifier™, смотрите Пакет поддержки плат FPGA Загрузки. (Если вы не видите перечисленных плат, затем вы еще не загрузили пакет поддержки). Если вы планируете задать пользовательскую плату сами, смотрите Индивидуальную настройку Совета FPGA.

FPGA-in-the-Loop Connection: метод связи симуляции FIL. Опции в выпадающем меню обновляются в зависимости от методов связи, поддержанных для требуемой платы, которую вы выбрали. Если требуемая плата и HDL Verifier поддерживают связь, можно выбрать Ethernet, JTAG, или PCI Express.

Advanced Options:

Когда вы выбираете соединение Ethernet, можно настроить IP платы и Мак адреса при необходимости.

| Опция | Инструкции |

|---|---|

| Board IP address | Используйте эту опцию в установке IP-адреса платы, если это не IP-адрес по умолчанию (192.168.0.2). Если IP-адрес платы по умолчанию (192.168.0.2) используется другим устройством, или вы нуждаетесь в различной подсети, изменяете IP-адрес Совета согласно следующим инструкциям:

|

| Board MAC address | При большинстве обстоятельств вы не должны изменять Мак адрес платы. Если вы соединяете больше чем одну макетную плату FPGA с одним хостом - компьютером, изменяете Мак адрес платы для каких-либо дополнительных плат так, чтобы каждый адрес был уникален. У вас должен быть отдельный NIC для каждой платы. Чтобы изменить Мак адрес Совета, щелкните в поле Board MAC address. Задайте адрес, который отличается с той принадлежности на любое другое устройство, присоединенное к вашему компьютеру. Чтобы получить Мак адрес Совета для определенной макетной платы FPGA, обратитесь к метке, присоединенной к плате, или консультируйтесь с документацией по продукту. |

FPGA system clock frequency (MHz): Введите целевую частоту часов. Для плат Intel и поддерживаемых плат ISE Xilinx, filWizard проверяет требуемую частоту по возможным для требуемой платы. Если требуемая частота не возможна для этой платы, filWizard возвращает ошибку и предлагает альтернативную частоту. Для Vivado-поддерживаемых-плат Xilinx, или плат PCI Express®, filWizard не может проверять частоту. Инструменты синтеза предпринимают попытку максимальных усилий требуемой частоты, но могут выбрать альтернативную частоту, если заданная частота не была достижима. Значением по умолчанию является 25 МГц.

Нажмите Next.

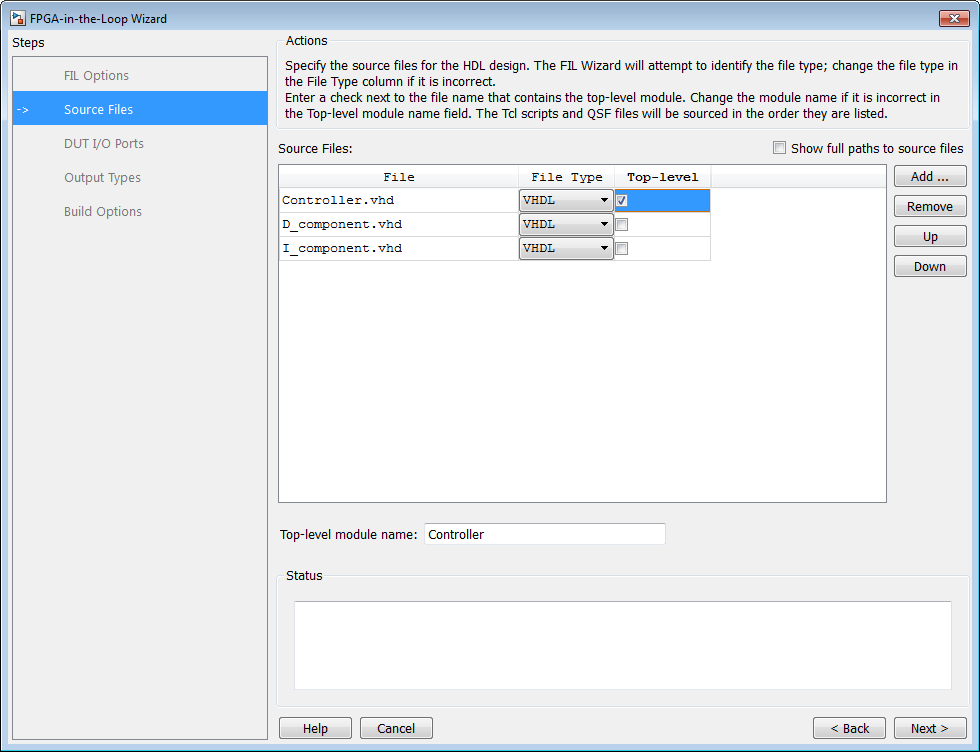

На странице Source Files:

Задайте проект HDL, чтобы быть cosimulated в FPGA. Эти файлы являются файлами проекта HDL, которые будут проверены на плате FPGA.

Укажите на исходные файлы путем нажатия на Add. Выберите файлы с помощью диалогового окна выбора файла.

Мастер FIL пытается идентифицировать типы исходного файла. Если какие-либо из типов файлов не то, что вы ожидаете, можно изменить его путем выбора из File Type выпадающего списка. Приемлемые типы файлов:

VHDL®

Verilog®

Список соединений

Скрипт Tcl

Ограничения

Другие

"Другие" обращаются к следующему:

Для Intel, файлы, заданные как Other добавляются к проекту FPGA, но они не оказывают влияния на сгенерированный блок. Например, можно поместить некоторые комментарии в “readme” файл и включать его в этот список файлов.

Для Xilinx, файлы, заданные как Other может быть любой файл, принятый Xilinx ISE. ISE смотрит на расширение файла, чтобы определить, как использовать этот файл. Например, если вы добавляете foo.vhd в список и задаете его как Other, ISE обрабатывает файл как файл VHDL.

Задайте, какой файл содержит файл HDL верхнего уровня.

Установите флажок на строке файла HDL, который содержит модуль HDL верхнего уровня в столбце, названном Top-level. Мастер FIL автоматически заполняет поле Top-level module name именем выбранного файла HDL. Если имя модуля верхнего уровня и имя файла не соответствуют, можно вручную изменить имя модуля верхнего уровня в этом диалоговом окне. Укажите на имя модуля верхнего уровня, прежде чем вы продолжите.

(Необязательно), Чтобы отобразить полные пути к исходным файлам, установите флажок, названный Show full paths to source files.

Нажмите Next.

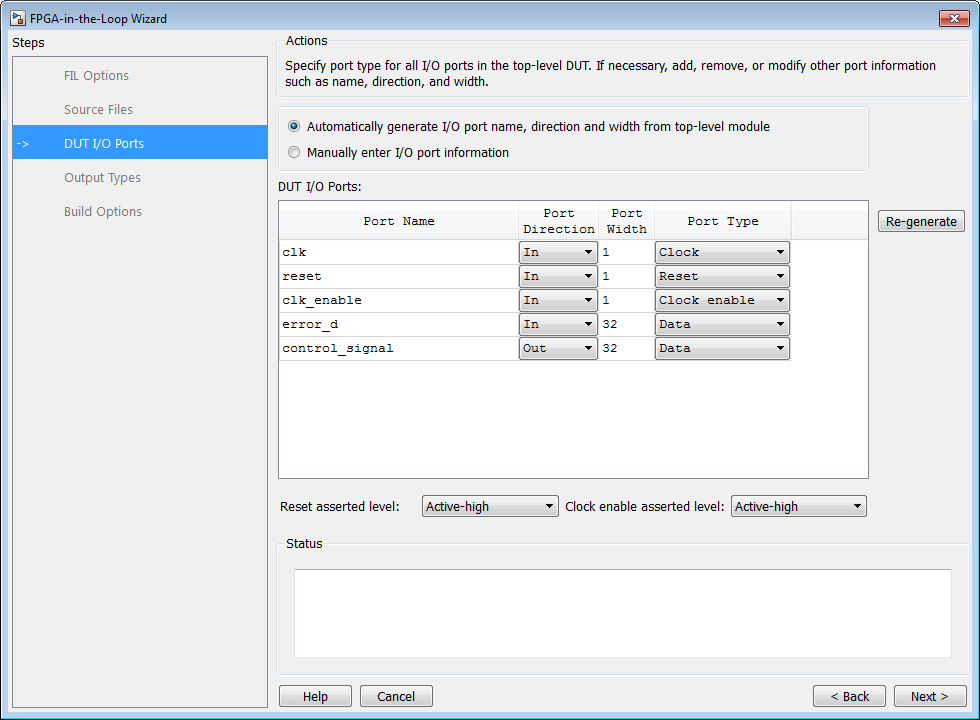

На странице DUT I/O Ports:

Рассмотрите список портов. Мастер FIL анализирует модуль HDL верхнего уровня, чтобы получить все порты I/O и отобразить их в таблице DUT I/O Ports. Синтаксический анализатор пытается определить типы порта из имен порта. Мастер затем отображает эти сигналы под Типом порта.

Убедитесь, что все входные/выходы/сброс порты/часы сопоставлены, как вы ожидаете. Если синтаксический анализатор присвоил тип неправильного порта для какого-либо порта, можно вручную изменить сигнал. Для синхронного проекта задайте Часы, Сброс, или при желании Часы включают сигнал. Типы порта, заданные в этой таблице, должны быть эквивалентными в HDL-коде. Должен быть по крайней мере один выходной порт.

Выберите Manually enter port information, чтобы добавить или удалить сигналы.

Нажмите Regenerate, чтобы перезагрузить таблицу с определениями исходного порта (от HDL-кода).

Нажмите Next.

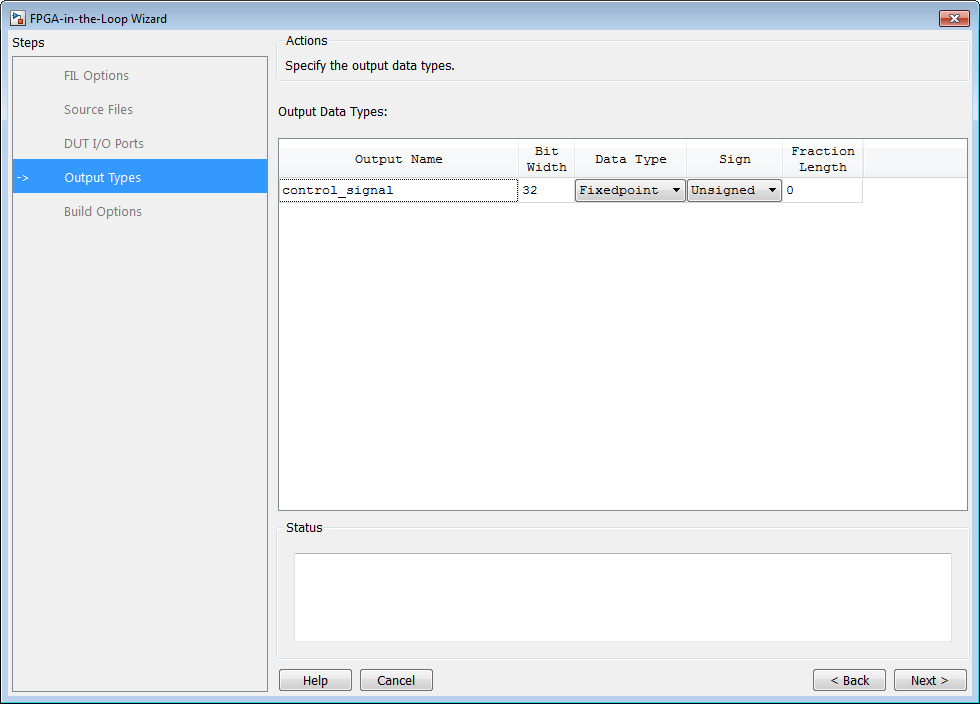

На странице Output Types:

Задайте типы выходных данных. Мастер присваивает типы данных. Если какой-либо тип выходных данных не то, что вы ожидаете, вручную изменяете тип.

Выберите из:

Fixedpoint

Integer

Logical

Тип данных может зависеть от заданной битной ширины.

Можно задать выходной тип, чтобы быть Signed, Unsigned, или Fraction Length.

Нажмите Next.

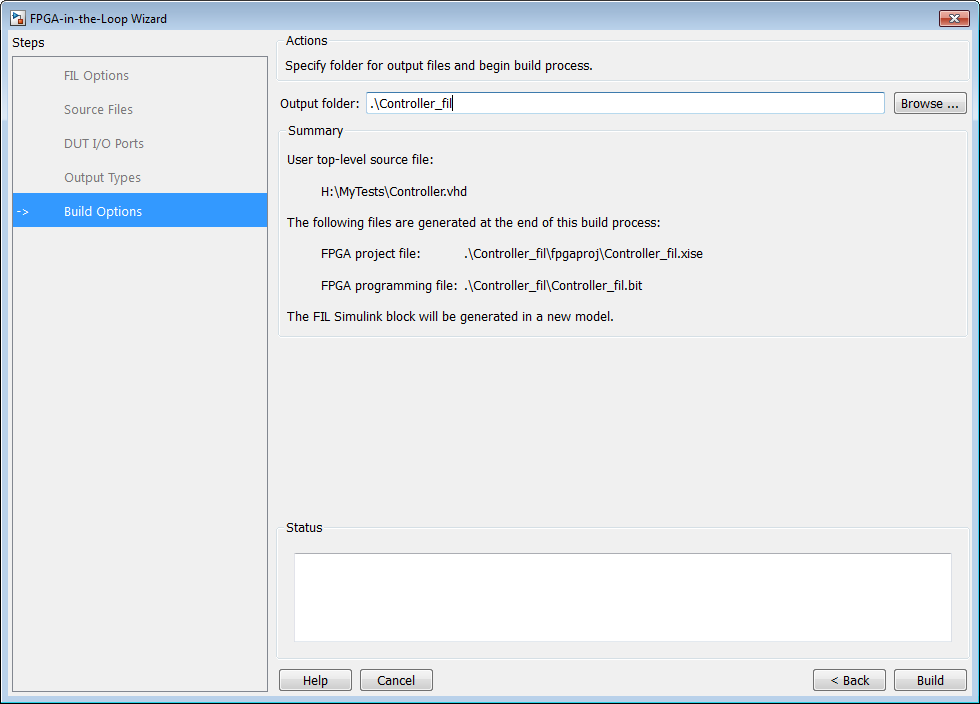

На the Build Options странице:

Задайте папку для выходных файлов. Можно использовать опцию по умолчанию. Обычно значением по умолчанию является подпапка, названная в честь модуля верхнего уровня, расположенного под текущей папкой.

Summary отображает местоположения файла проекта ISE и файла программирования FPGA. Вам, возможно, понадобятся те два файла для усовершенствованных операций на маске блока FIL.

Нажмите Build, чтобы инициировать генерацию блока FIL.

Мастер FIL генерирует блок FIL, названный в честь модуля верхнего уровня, и помещает его в новую модель.

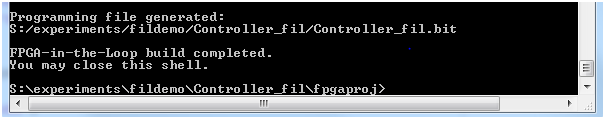

Мастер FIL открывает командное окно.

В этом окне программное обеспечение проекта FPGA выполняет синтез, подгонку, PAR и FPGA, программируя генерацию файла.

Когда процесс завершается, сообщение в командном окне предлагает вам закрывать окно.

В вашей модели замените подсистему DUT на блок FIL, сгенерированный в новой модели. Сохраните модель под другим именем. Можно затем использовать исходную модель в качестве образца модели.

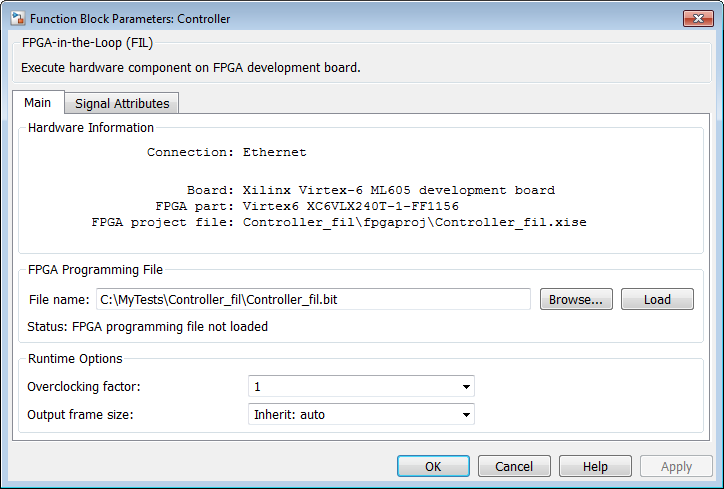

Если вы сгенерировали свой блок FIL из HDL Workflow Advisor, маловероятно, что необходимо настроить любые настройки на блоке FIL. Если вы сгенерировали свой блок FIL с помощью мастера FIL, можно хотеть настроить некоторые настройки. Для получения инструкций по корректировке настроек блока FIL смотрите FIL Simulation.

Инструкции Совета Intel для Linux

Инструкции Совета Intel для Linux

Убедитесь, что ваша макетная плата FPGA настраивается, включила и связала с вашей машиной с помощью кабеля JTAG. Программирование использует интерфейс JTAG, даже если вы выбираете различную связь для симуляции.

Выполните следующие шаги, чтобы программировать FPGA:

Дважды кликните блок FIL в своей модели Simulink, чтобы открыть маску блока.

На вкладке Main нажмите Load, чтобы загрузить файл программирования на FPGA через кабель JTAG.

Процесс загрузки может взять от нескольких минут до нескольких минут или дольше, в зависимости от того, насколько большой подсистема. Иногда, процесс может занять полтора часа или дольше для больших подсистем.

Окно сообщения указывает, когда файл программирования FPGA загрузил как ожидалось. Нажмите OK.

В Simulink, запускает модель, которая включает блок FIL Simulation. Результаты симуляции FIL должны совпадать с результатами образца модели Simulink или исходного HDL-кода.

Инициализация RAM: Simulink запускается со времени 0 каждых раз, что означает, что RAM в модели Simulink инициализируется, чтобы обнулить для каждого запуска. Однако это предположение не верно в оборудовании. RAM в FPGA содержит свое значение от конца одной симуляции к запуску следующего. Если у вас есть RAM в вашем проекте, первая симуляция совпадает с Simulink, но последующие запуски не могут соответствовать. Обходное решение должно перезагрузить поток битов FPGA прежде, чем повторно выполнить симуляцию. Чтобы перезагрузить поток битов, нажмите Load на маске блока FIL.