Откройте FPGA-in-the-Loop Wizard.

В окне команды MATLAB введите следующее:

>> filWizard

Чтобы восстановить предыдущий сеанс, используйте эту команду:

filWizard('./Subsystem_fil/Subsystem_fil.mat')

(Эта страница для Системы FIL object™. Для опций блока FIL Simulink® смотрите Шаг 3: Установите Опции FIL для Блока FIL.)

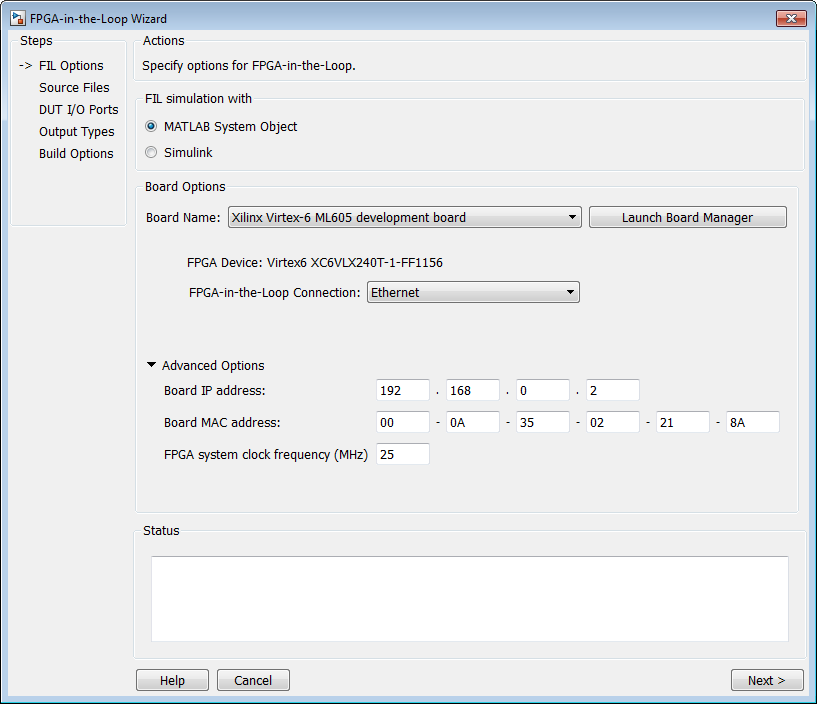

На странице FIL Options:

FIL Simulation with: выберите MATLAB System Object.

Board Name: Выберите макетную плату FPGA. Если вы еще не загрузили пакет поддержки плат FPGA HDL Verifier™, смотрите Пакет поддержки плат FPGA Загрузки. (Если вы не видите перечисленных плат, затем вы еще не загрузили пакет поддержки). Если вы планируете задать пользовательскую плату сами, смотрите Индивидуальную настройку Совета FPGA.

FPGA-in-the-Loop Connection: метод связи симуляции FIL. Опции в выпадающем меню обновляются в зависимости от методов связи, поддержанных для требуемой платы, которую вы выбрали. Если требуемая плата и HDL Verifier поддерживают связь, можно выбрать Ethernet, JTAG, или PCI Express.

Advanced Options:

Когда вы выбираете соединение Ethernet, можно настроить IP платы и Мак адреса при необходимости.

| Опция | Инструкции |

|---|---|

| Board IP address | Используйте эту опцию в установке IP-адреса платы, если это не IP-адрес по умолчанию (192.168.0.2). Если IP-адрес платы по умолчанию (192.168.0.2) используется другим устройством, или вы нуждаетесь в различной подсети, изменяете IP-адрес Совета согласно следующим инструкциям:

|

| Board MAC address | При большинстве обстоятельств вы не должны изменять Мак адрес платы. Если вы соединяете больше чем одну макетную плату FPGA с одним хостом - компьютером, изменяете Мак адрес платы для каких-либо дополнительных плат так, чтобы каждый адрес был уникален. У вас должен быть отдельный NIC для каждой платы. Чтобы изменить Мак адрес Совета, щелкните в поле Board MAC address. Задайте адрес, который отличается с той принадлежности на любое другое устройство, присоединенное к вашему компьютеру. Чтобы получить Мак адрес Совета для определенной макетной платы FPGA, обратитесь к метке, присоединенной к плате, или консультируйтесь с документацией по продукту. |

FPGA system clock frequency (MHz): Введите целевую частоту часов. Для плат Intel и поддерживаемых плат ISE Xilinx, filWizard проверяет требуемую частоту по возможным для требуемой платы. Если требуемая частота не возможна для этой платы, filWizard возвращает ошибку и предлагает альтернативную частоту. Для Vivado-поддерживаемых-плат Xilinx, или плат PCI Express®, filWizard не может проверять частоту. Инструменты синтеза предпринимают попытку максимальных усилий требуемой частоты, но могут выбрать альтернативную частоту, если заданная частота не была достижима. Значением по умолчанию является 25 МГц.

Нажмите Next.

(Эта страница для Системного объекта FIL. Для исходных файлов HDL блока Simulink смотрите Шаг 4: Добавьте Исходные файлы HDL для Блока FIL.)

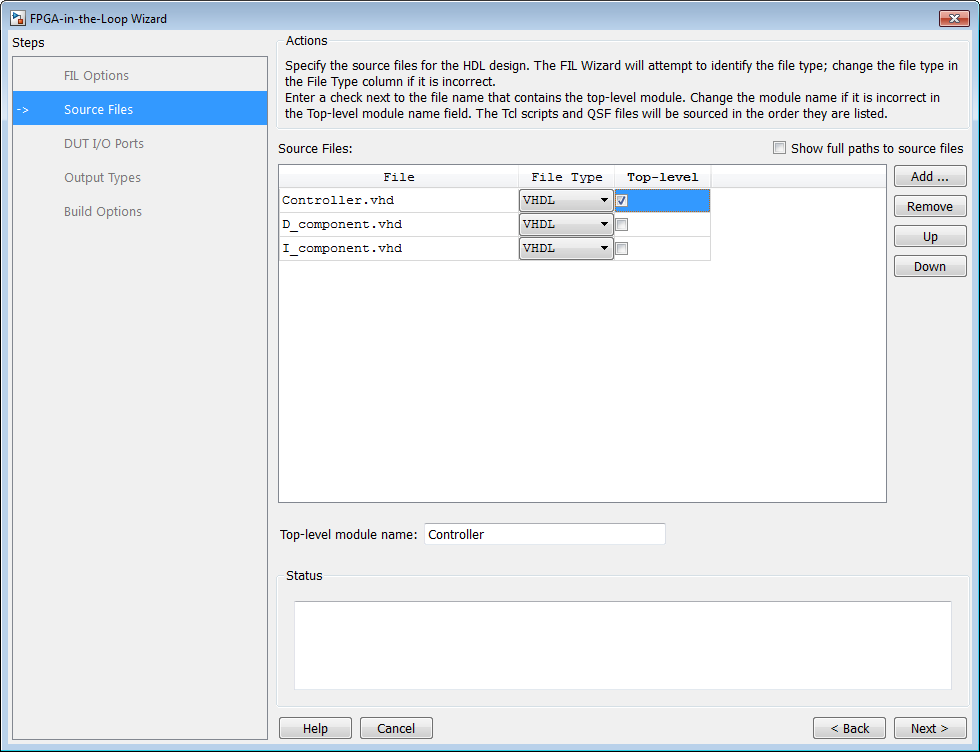

На странице Source Files:

Задайте проект HDL, чтобы быть cosimulated в FPGA. Эти файлы являются файлами проекта HDL, которые будут проверены на плате FPGA.

Укажите на исходные файлы путем нажатия на Add. Выберите файлы с помощью диалогового окна выбора файла.

Мастер FIL пытается идентифицировать типы исходного файла. Если какие-либо из типов файлов не то, что вы ожидаете, можно изменить его путем выбора из File Type выпадающего списка. Приемлемые типы файлов:

VHDL®

Verilog®

Список соединений

Скрипт Tcl

Ограничения

Другие

"Другие" обращаются к следующему:

Для Intel, файлы, заданные как Other добавляются к проекту FPGA, но они не оказывают влияния на сгенерированный блок. Например, можно поместить некоторые комментарии в “readme” файл и включать его в этот список файлов.

Для Xilinx, файлы, заданные как Other может быть любой файл, принятый Xilinx ISE. ISE смотрит на расширение файла, чтобы определить, как использовать этот файл. Например, если вы добавляете foo.vhd в список и задаете его как Other, ISE обрабатывает файл как файл VHDL.

Задайте, какой файл содержит файл HDL верхнего уровня.

Установите флажок на строке файла HDL, который содержит модуль HDL верхнего уровня в столбце, названном Top-level. Мастер FIL автоматически заполняет поле Top-level module name именем выбранного файла HDL. Если имя модуля верхнего уровня и имя файла не соответствуют, можно вручную изменить имя модуля верхнего уровня в этом диалоговом окне. Укажите на имя модуля верхнего уровня, прежде чем вы продолжите.

(Необязательно), Чтобы отобразить полные пути к исходным файлам, установите флажок, названный Show full paths to source files.

Нажмите Next.

(Эта страница для FIL с Системным объектом. Для Simulink смотрите Шаг 5: Проверьте Порты ввода-вывода DUT для Блока FIL.)

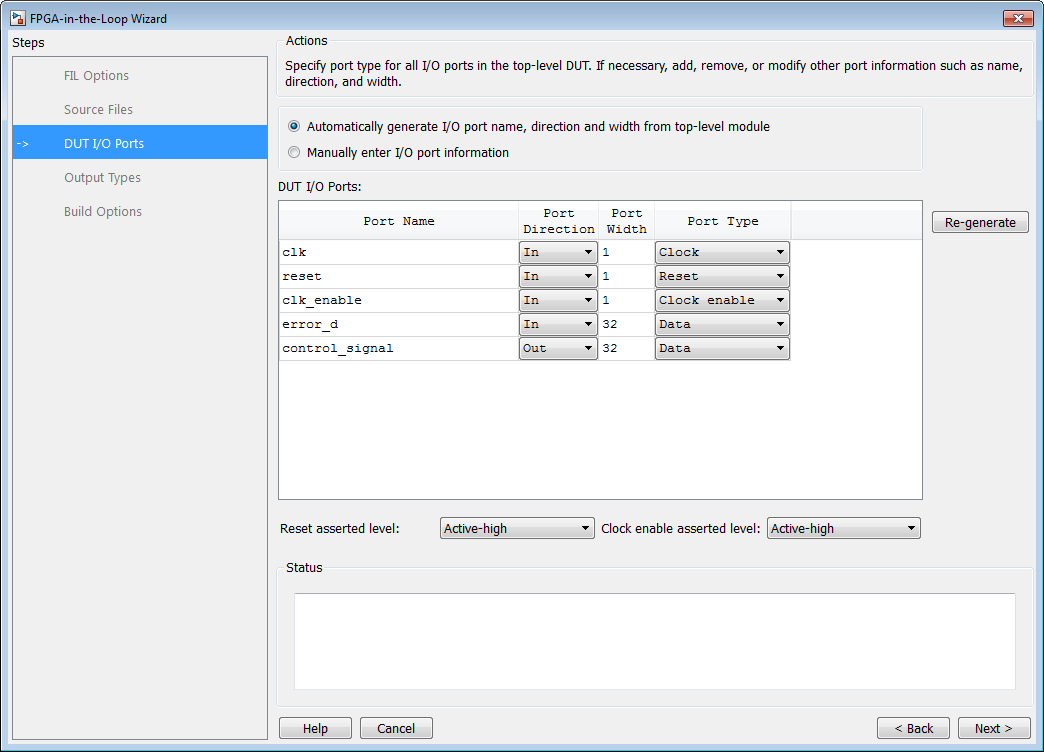

На странице DUT I/O Ports:

Рассмотрите список портов. Мастер FIL анализирует модуль HDL верхнего уровня, чтобы получить все порты I/O и отобразить их в таблице DUT I/O Ports. Синтаксический анализатор пытается определить типы порта из имен порта. Мастер затем отображает эти сигналы под Типом порта.

Убедитесь, что все входные/выходы/сброс порты/часы сопоставлены, как вы ожидаете. Если синтаксический анализатор присвоил тип неправильного порта для какого-либо порта, можно вручную изменить сигнал. Для синхронного проекта задайте Часы, Сброс, или при желании Часы включают сигнал. Типы порта, заданные в этой таблице, должны быть эквивалентными в HDL-коде. Должен быть по крайней мере один выходной порт.

Выберите Manually enter port information, чтобы добавить или удалить сигналы.

Нажмите Regenerate, чтобы перезагрузить таблицу с определениями исходного порта (от HDL-кода).

Нажмите Next.

(Эта страница для Системного объекта FIL. Поскольку блок Simulink вывел типы, смотрите Шаг 6: Задайте Выходные Типы для Блока FIL.)

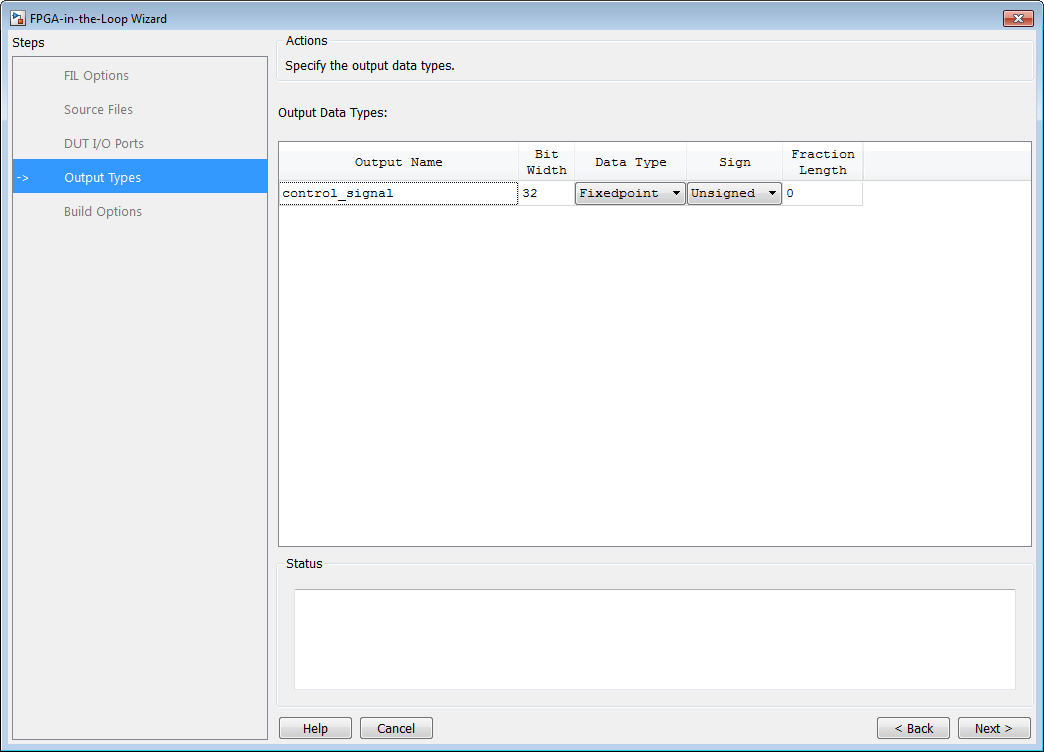

На странице Output Types:

Задайте типы выходных данных. Мастер присваивает типы данных. Если какой-либо тип выходных данных не то, что вы ожидаете, вручную изменяете тип.

Выберите из:

Fixedpoint

Integer

Logical

Тип данных может зависеть от заданной битной ширины.

Можно задать выходной тип, чтобы быть Signed, Unsigned, или Fraction Length.

Нажмите Next.

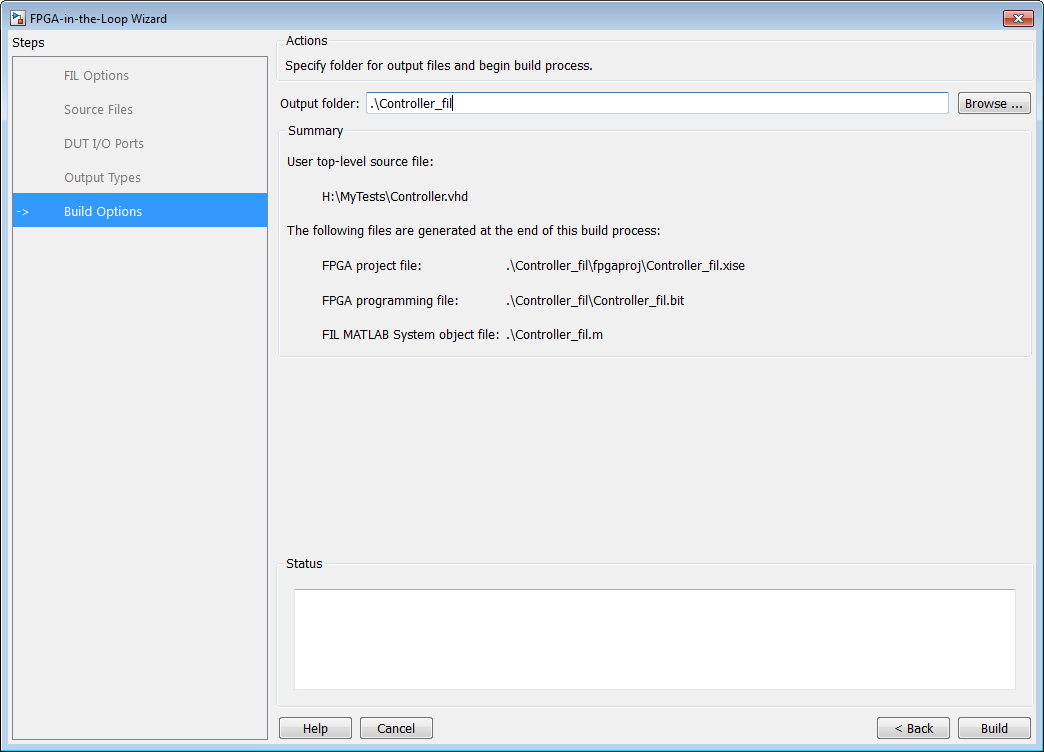

(Эта страница для Системного объекта FIL. Для Simulink смотрите Шаг 7: Задайте Опции Сборки для Блока FIL.)

На the Build Options странице:

Задайте папку для выходных файлов. Можно использовать опцию по умолчанию. Обычно значением по умолчанию является подпапка, названная в честь модуля верхнего уровня, расположенного под текущей папкой.

Summary отображает местоположения файла проекта ISE и файла программирования FPGA. Вам, возможно, понадобятся те два файла для усовершенствованных операций на маске блока FIL.

Нажмите Build, чтобы инициировать генерацию Системного объекта FIL.

Мастер FIL генерирует следующие файлы:

В./ папка, функция MATLAB под названием toplevel_fil/toplevel_programFPGA.mtoplevel имя верхнего уровня HDL. Этот файл содержит код, чтобы загрузить файл программирования FPGA на FPGA.

function toplevel_programFPGA

%Load the bitstream in the FPGA

filProgramFPGA('Xilinx', '/dir/mybitstream.bit', 1);

endФайл MATLAB под названием toplevel_fil.mtoplevel имя верхнего уровня HDL. Этот файл содержит определение класса, выведенное из hdlverifier.FILSimulation и инициализирует частные свойства. Этот файл расположен в текущей папке.

Следующее является выборкой файла определения класса, сгенерированного с помощью мастера FIL от DUT под названием fft8.

classdef fft8_fil < hdlverifier.FILSimulation

%fft8_fil is a filWizard generated class used for FPGA-In-the-Loop

% simulation with the 'fft8' DUT.

% fft8_fil connects MATLAB with a FPGA and cosimulate with it by

% writing inputs in the FPGA and reading outputs from the FPGA.

%

% MYFIL = fft8_fil

%

% Step method syntax:

%

% [out1, out2, ...] = step(MYFIL, in1, in2, ...) connect to the FPGA,

% write in1, in2, ... to the FPGA and read out1, out2, ... from

% the FPGA

%

% fft8_fil methods:

%

% step - See above description for use of this method

% release - Allow property value and input characteristics changes, and

% release connection to FPGA board

% clone - Create fft8_fil object with same property values

% isLocked - Locked status (logical)

% programFPGA - Load the programming file in the FPGA

%

% fft8_fil properties:

%

% DUTName - DUT top level name

% InputSignals - Input paths in the HDL code

% InputBitWidths - Width in bit of the inputs

% OutputSignals - Output paths in the HDL code

% OutputBitWidths - Width in bit of the outputs

% OutputDataTypes - Data type of the outputs

% OutputSigned - Sign of the outputs

% OutputFractionLengths - Fraction lengths of the outputs

% OutputDownsampling - Downsampling factor and phase of the outputs

% OverclockingFactor - Overclocking factor of the hardware

% SourceFrameSize - Frame size of the source (only for HDL source block)

% Connection - Parameters for the connection with the board

% FPGAVendor - Name of the FPGA chip vendor

% FPGABoard - Name of the FPGA board

% FPGAProgrammingFile - Path of the Programming file for the FPGA

% ScanChainPosition - Position of the FPGA in the JTAG scan chain

%

% File Name: fft8_fil.m

% Created: 26-Apr-2012 18:18:06

%

% Generated by FIL Wizard

properties (Nontunable)

DUTName = 'fft8';

end

methods

function obj = fft8_fil

%THE FOLLOWING PROTECTED PROPERTIES ARE SPECIFIC TO THE HW DUT

%AND MUST NOT BE EDITED (RERUN THE FIL WIZARD TO CHANGE THEM)

obj.InputSignals = char('Xin_re','Xin_im');

obj.InputBitWidths = [10,10];

obj.OutputSignals = char('Xout_re','Xout_im');

obj.OutputBitWidths = [13,13];

obj.Connection = char('UDP','192.168.0.2','00-0A-35-02-21-8A');

obj.FPGAVendor = 'Xilinx';

obj.FPGABoard = 'XUP Atlys Spartan-6 development board';

obj.ScanChainPosition = 1 ;

%THE FOLLOWING PUBLIC PROPERTIES ARE RELATED TO THE SIMULATION

%AND CAN BE EDITED WITHOUT RERUNING THE FIL WIZARD

obj.OutputSigned = [true,true];

obj.OutputDataTypes = char('fixedpoint','fixedpoint');

obj.OutputFractionLengths = [9,9];

obj.OutputDownsampling = [1,0];

obj.OverclockingFactor = 1;

obj.SourceFramieSize = 1;

obj.FPGAProgrammingFile = 'S:\MATLAB\demo\fft8_fil\fft8_fil.bit';

end

end

end

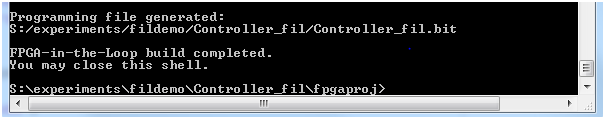

Мастер FIL открывает командное окно.

В этом окне программное обеспечение проекта FPGA выполняет синтез, подгонку, PAR и FPGA, программируя генерацию файла.

Когда процесс завершается, сообщение в командном окне предлагает вам закрывать окно.

Создайте пользовательский FILSimulation Системный объект из файла определения класса, выведенного с помощью мастера FIL. Этот фрагмент кода создает экземпляр класса и инициализирует все свойства.

MYFIL = toplevel_fil

Если вы сгенерировали свой Системный объект FIL от HDL Workflow Advisor, маловероятно, что необходимо настроить любые настройки. Если вы сгенерировали свой Системный объект FIL с помощью Мастера FIL, можно хотеть настроить некоторые настройки. Можно настроить любое перезаписываемое свойство с помощью одного из этих методов:

Измените свойство с методом установки:

MYFIL.set('FPGAProgrammingFile','c:\work\filfiles')Установите свойство непосредственно:

MYFIL.FPGAProgrammingFile='c:\work\filfiles'

Отредактируйте toplevel_fil.m.m файл, инстанцируйте объекта в рабочей области снова, если вы сделали так ранее.

Для получения дополнительной информации о свойствах объектов, смотрите hdlverifier.FILSimulation.

Можно программировать FPGA с помощью любого programFPGA функция или programFPGA метод Системного объекта FIL. Если вы еще не выполнили Ведомую Настройку оборудования, сделайте так теперь прежде, чем загрузить файлы программирования.

programFPGA функция:

./toplevel_fil/toplevel_programFPGA

programFPGA метод:

MYFIL.programFPGA

MYFIL экземпляр FILSimulation объект.

Вызовите Системный объект в своем коде MATLAB.

Запустите свой код MATLAB, как вы обычно были бы. Убедитесь, что вы выполнили Ведомую Настройку оборудования перед началом.

Первый вызов объекта устанавливает связь с платой FPGA.