В процессоре в цикле (PIL) симуляция алгоритм управления выполняется в целевом компьютере, но модель объекта управления работает на хост-машине. Модель объекта управления (работающий на хост-машине) симулирует сигналы ввода и вывода для контроллера (работающий на целевом компьютере) и связывается с контроллером при помощи последовательного интерфейса. Эта функциональность позволяет вам использовать PIL симуляцию, чтобы определить время выполнения на целевом компьютере, который можно затем сравнить со временем выполнения для симуляции модели на хост-машине.

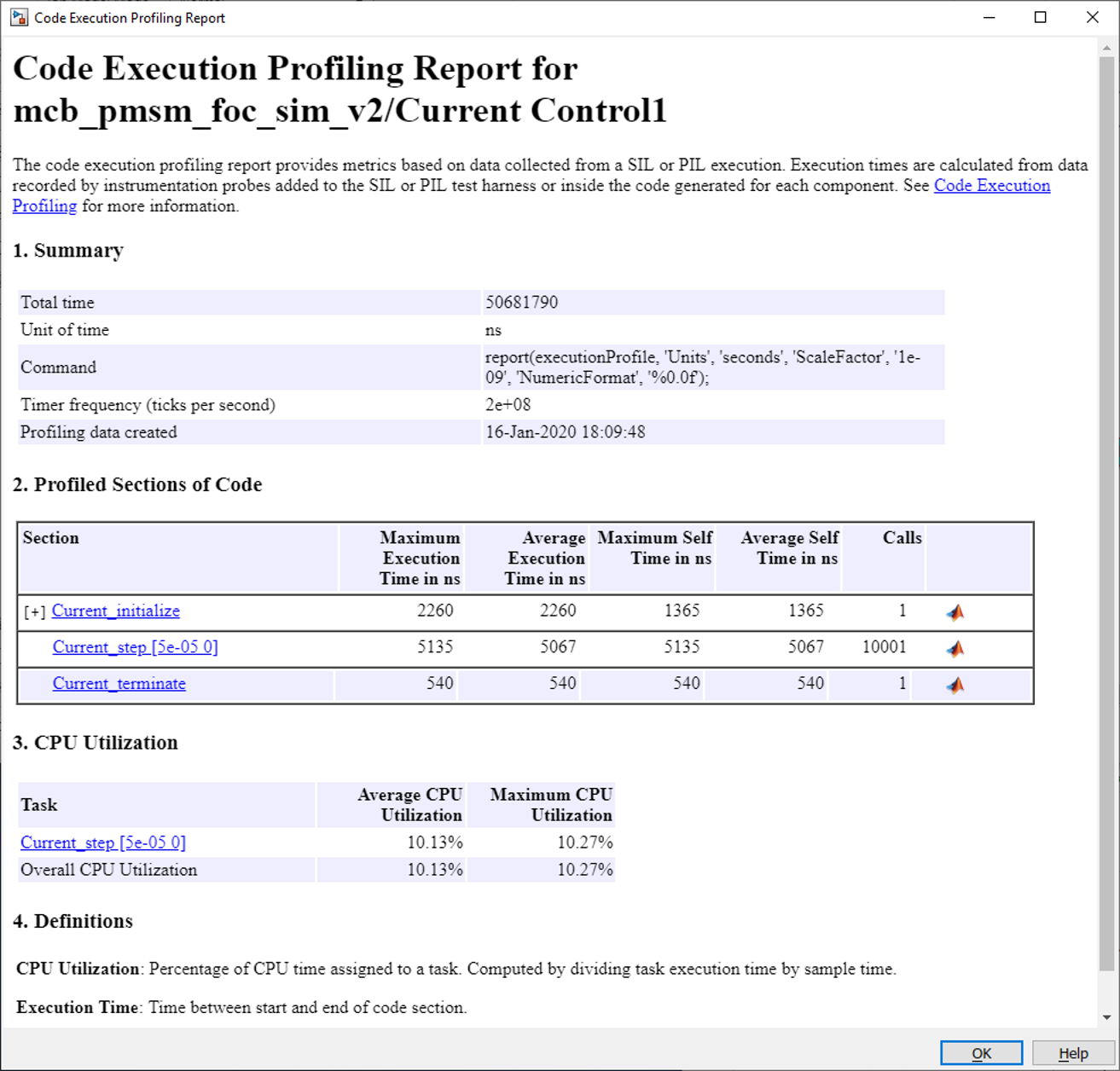

Время выполнения или показатели производительности алгоритма, который вы получаете из PIL симуляции, помогают вам обнаружить алгоритм, превышенный на целевом компьютере. PIL, профилирующий отчет, указывает на средние и максимальные времена выполнения алгоритма на целевом компьютере. Этот пример объясняет PIL, профилирующий на аппаратной плате Instruments™ LAUNCHXL-F28379D Техаса.

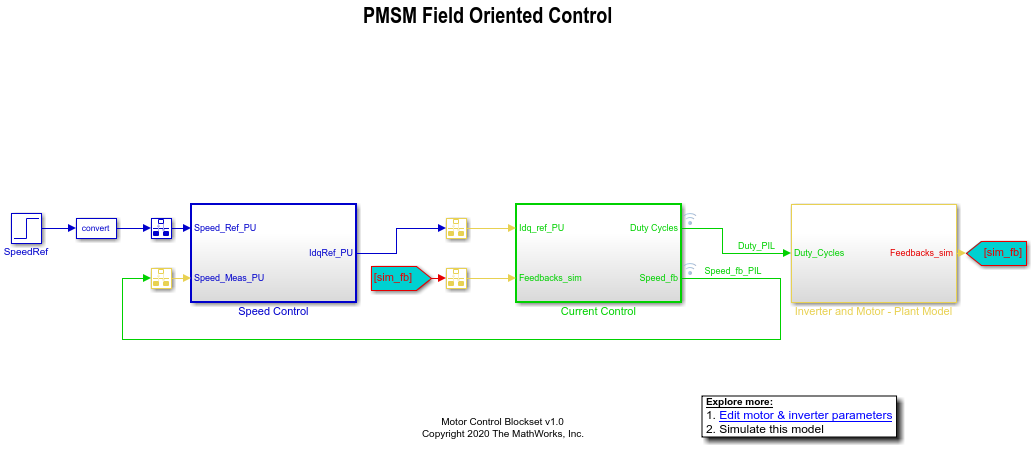

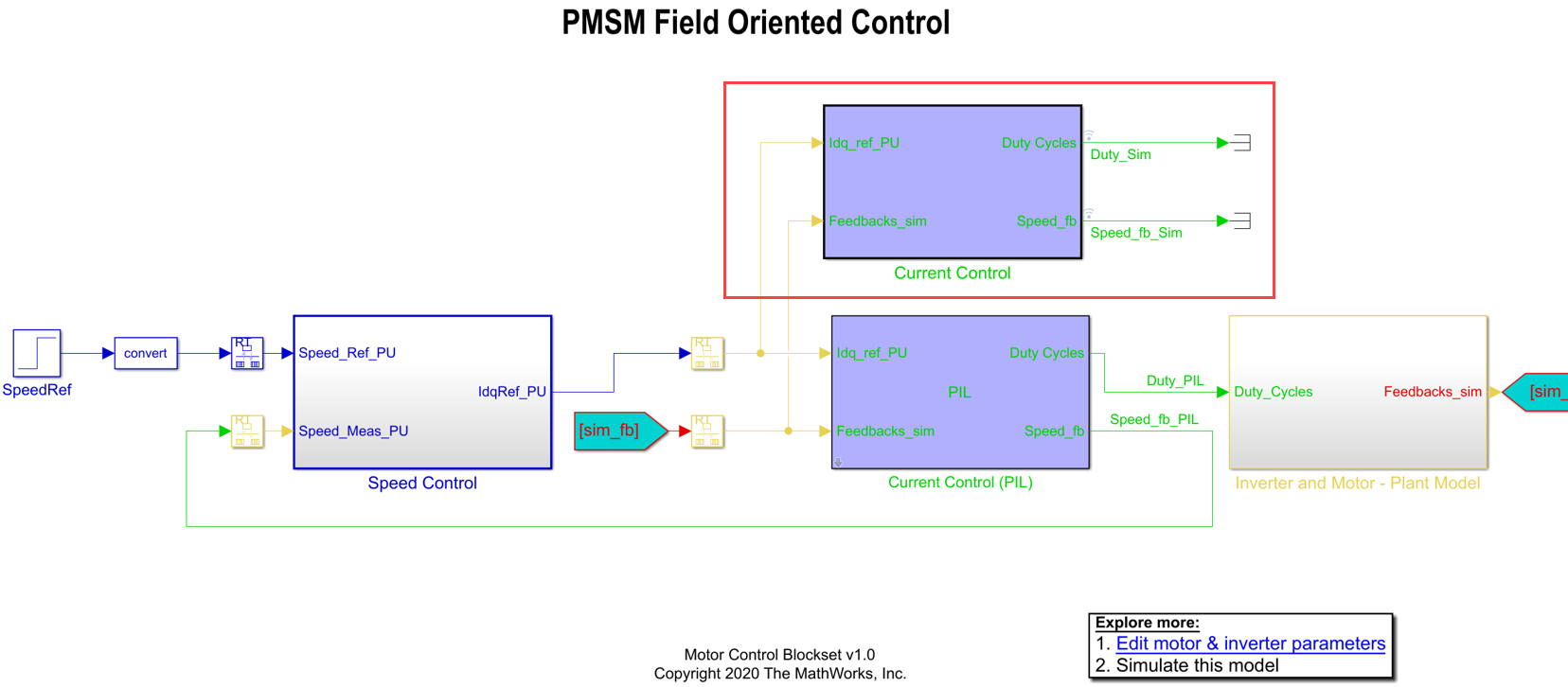

Мы используем модель mcb_pmsm_foc_sim.slx в качестве примера продемонстрировать верификацию кода в PIL симуляции. Этот пример показывает PIL, профилирующий для Текущей подсистемы Управления в модели в качестве примера. Эта подсистема включает Ориентированное на поле управление (FOC), текущее масштабирование (преобразование на модуль), измерение скорости и масштабирование положения ротора (расчет угла от количеств положения энкодера) алгоритмы. PIL, профилирующий отчет, показывает среднее выполнение и максимальные времена выполнения алгоритма управления в целевом компьютере.

Этот раздел обращается к этим задачам:

Проверьте выполнение кода при помощи Тестирования с процессором в контуре обратной связи путем сравнения алгоритма в рабочих режимах целевого компьютера и симуляции.

Выполните профилирование PIL путем измерения времени выполнения алгоритма в целевом компьютере и сгенерируйте PIL, профилирующий отчет.

Embedded Coder®

Пакет поддержки Embedded Coder для процессоров Texas Instruments C2000™

Плата оборудования контроллеров LAUNCHXL-F28379D

BOOSTXL-DRV8305 и BOOSTXL-3PHGANINV (поддерживаемые инверторы)

Моторный M-2310P Teknic, BLY171D и BLY172S (поддерживаемые двигатели с датчиками Холла) или двигатель Teknic M-2310P и BLY171D (двигатели, которые поддерживают квадратурный энкодер),

Предоставление мощности постоянного тока (24 В)

Используйте эти шаги, чтобы подготовить модель PIL к профилированию:

Откройте модель mcb_pmsm_foc_sim.slx при помощи этой команды:

open_system('mcb_pmsm_foc_sim.slx');

Эта модель симулирует двигатель PMSM и алгоритм FOC для регулировки скорости с обратной связью.

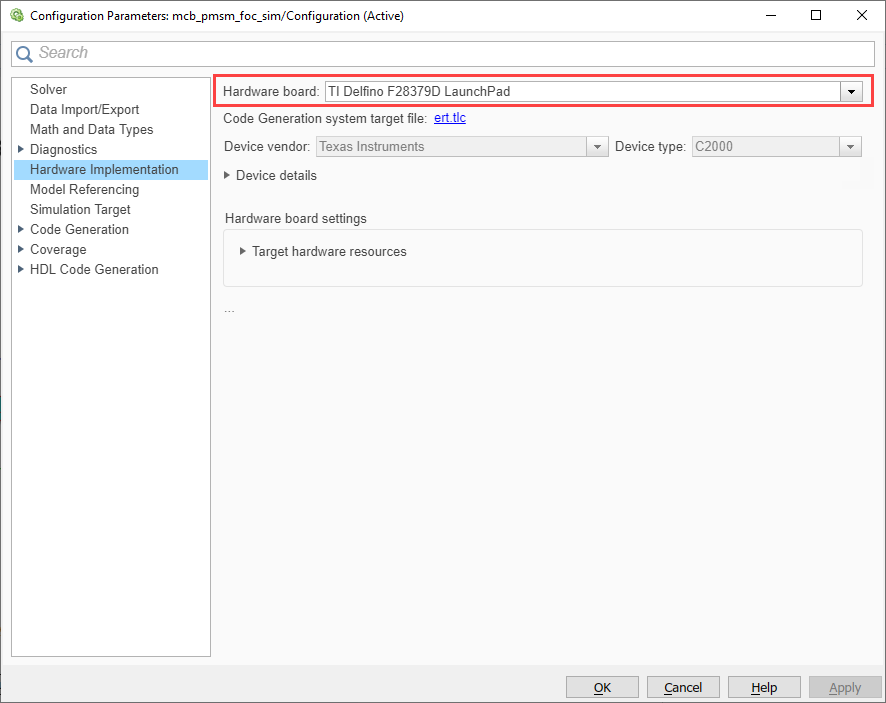

На вкладке Hardware панели инструментов Simulink нажмите Hardware Settings.

В окне Configuration Paramters, под Hardware Implementation, устанавливает поле Hardware board на TI Delfino F28379D.

Используйте эти шаги, чтобы проверить код в PIL:

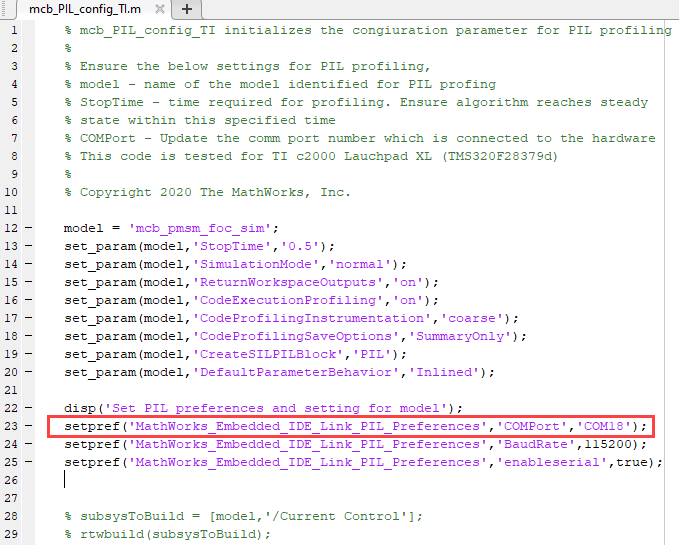

Откройте файл скрипта mcb_PIL_config_TI.m установить параметры конфигурации:

edit('mcb_PIL_config_TI.m');Обновите номер коммуникационного порта к тому, который вы используете.

Запустите скрипт, чтобы обновить параметры конфигурации имитационной модели и настроек PIL.

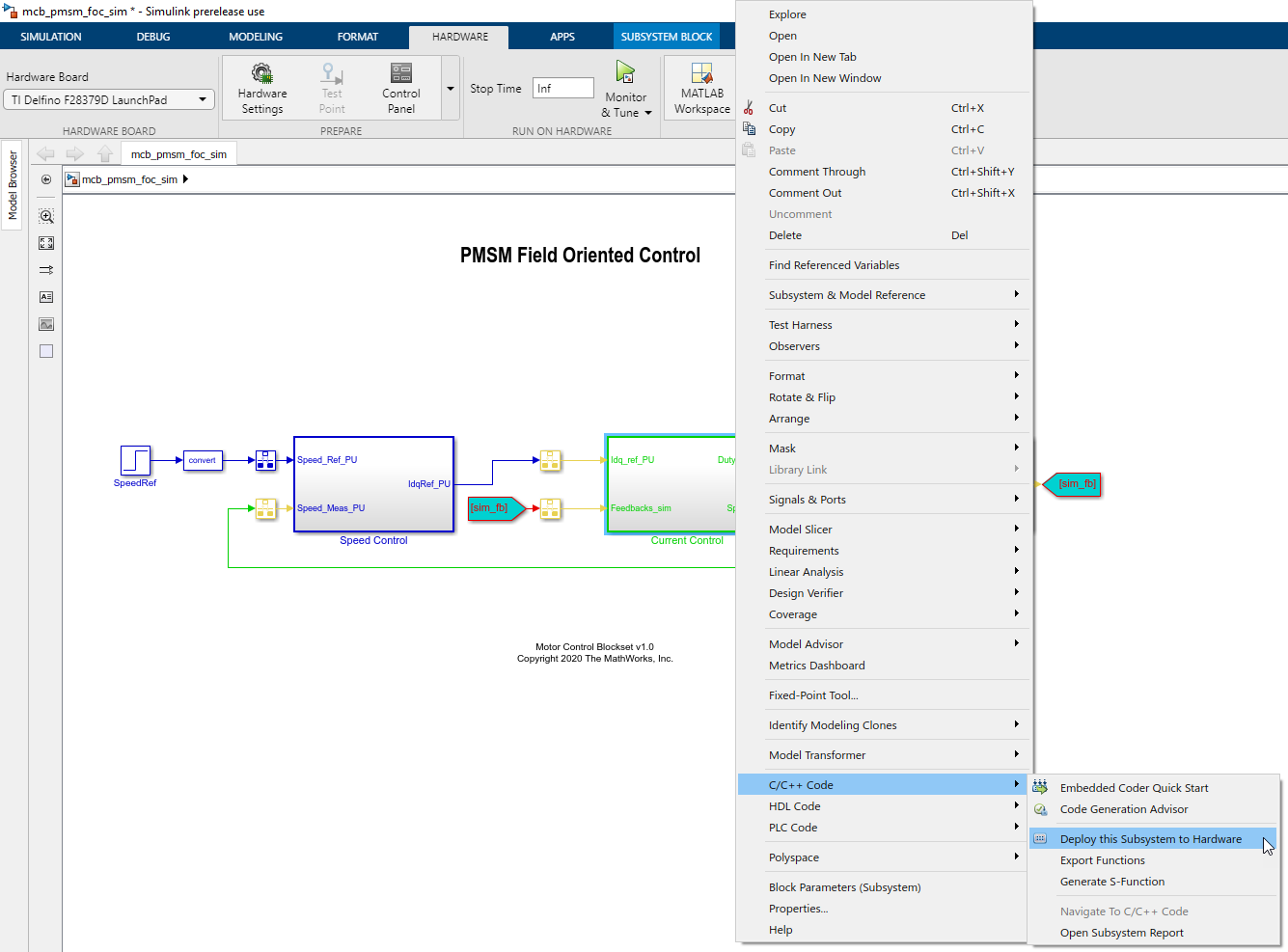

Щелкните правой кнопкой по Текущей подсистеме Управления по mcb_pmsm_foc_sim.slx модель в качестве примера. В соответствии с меню C/C++ Code, выберите Deploy this Subsystem to Hardware.

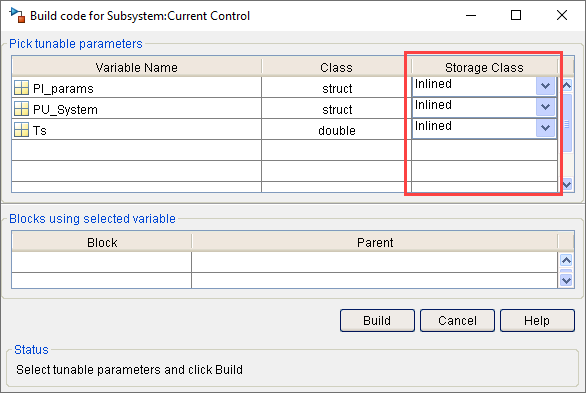

Система отображает диалоговое окно Build code for Subsystem. Установите Класс памяти на Inlined для всех параметров.

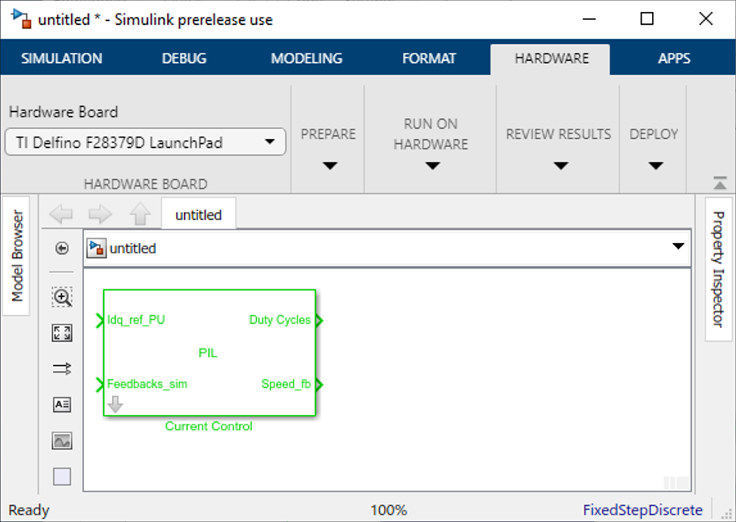

Нажмите Build, чтобы создать модель под названием untitiled это включает подсистему PIL под названием Текущее Управление.

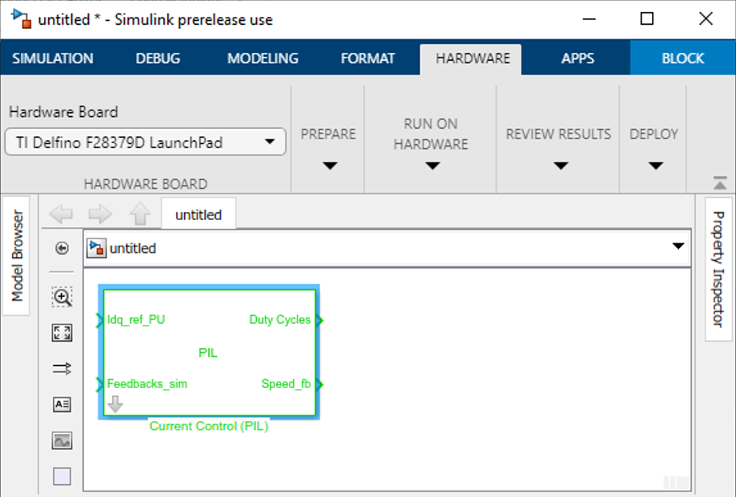

Переименуйте Текущую подсистему Управления в Текущее Управление (PIL).

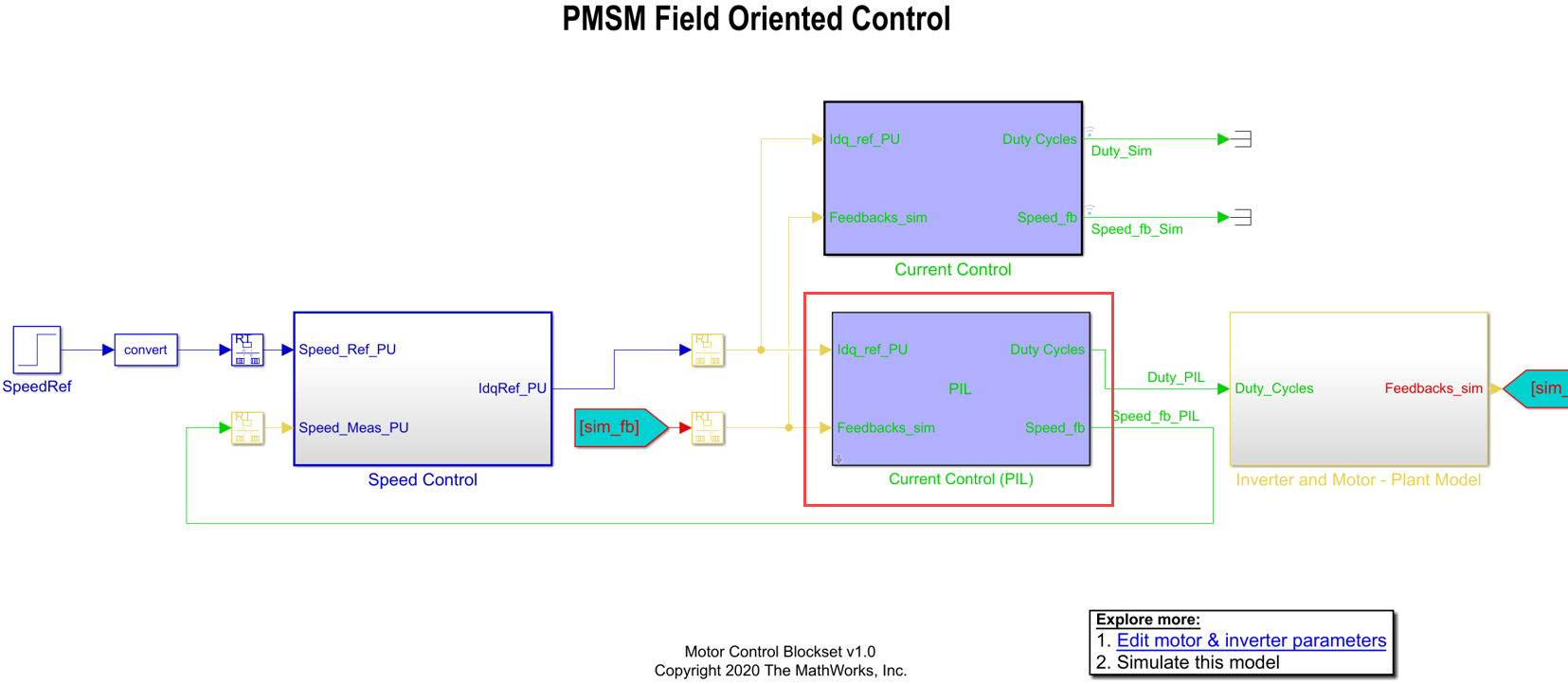

Скопируйте Текущее Управление (PIL) подсистема и замените Текущую подсистему Управления в mcb_pmsm_foc_sim.slx модель в качестве примера.

В режиме PIL система развертывает Текущее Управление (PIL) подсистема к цели и выполняет подсистему в целевом компьютере.

Чтобы сравнить осуществление алгоритма на симуляции хост-машины и в PIL симуляции, соедините Текущую подсистему Управления parallely с Текущим Управлением (PIL) подсистема. Кроме того, включите сигнал, входящий в систему подсистема выходные параметры.

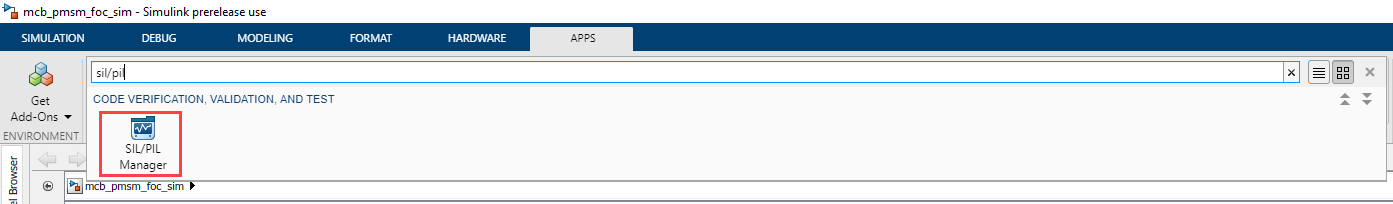

На панели инструментов Simulink выберите приложение SIL/PIL Manager из вкладки Apps.

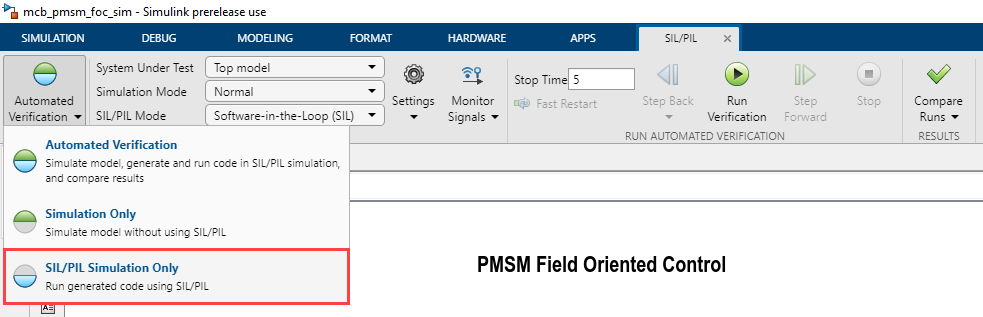

На панели инструментов SIL/PIL выберите SIL/PIL Sim Only.

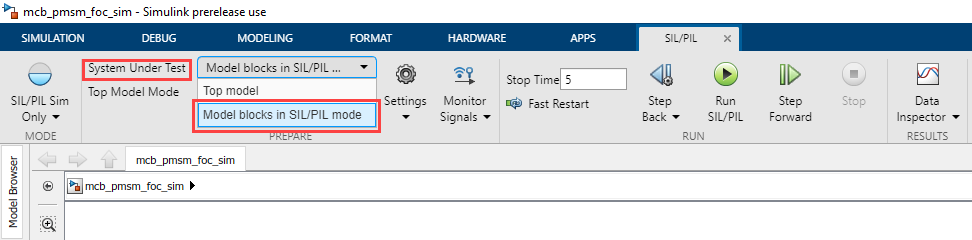

Выберите Model blocks in SIL/PIL mode в поле System Under Test.

Нажмите Run SIL/PIL на панели инструментов SIL/PIL, чтобы создать Текущее Управление (PIL) подсистема и развернуть его в цель.

После того, как система развертывает подсистему, Текущее Управление (PIL), который подсистема выполняет на процессоре целевого компьютера, в то время как модель объекта управления работает на хост-машине.

Когда PIL симуляция заканчивается, система генерирует профильный отчет.

PIL симуляция занимает больше времени, чем основанная на хост-машине симуляция. Это вызвано тем, что последовательной передачи (связанный с вводами и выводами Текущего Управления (PIL)) между хост-машиной и подсистемой, которая работает на целевом компьютере.

Профильный отчет показывает максимальные и средние времена выполнения Текущего Управления (PIL) подсистема, работающая на целевом компьютере.

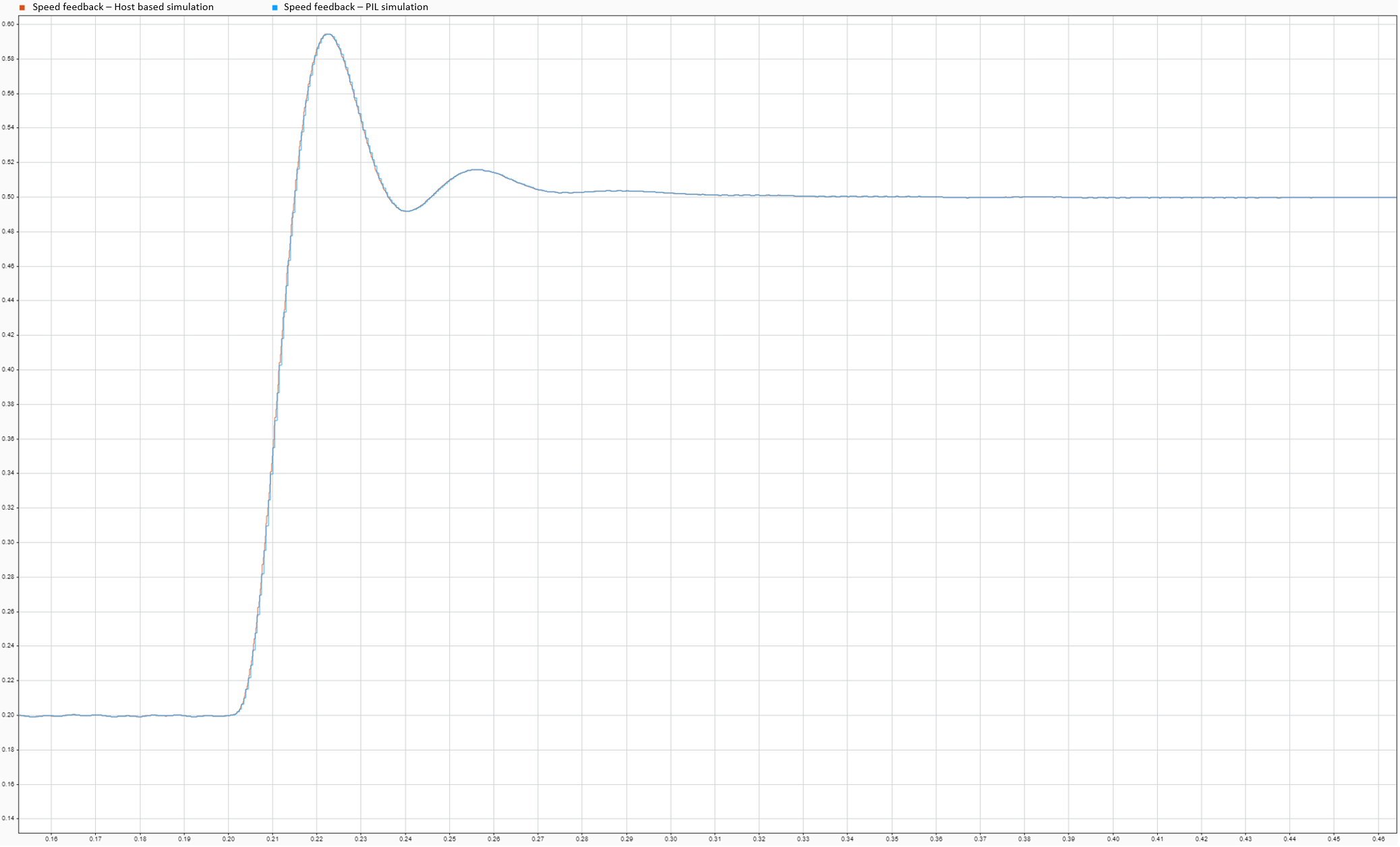

Можно использовать кнопку Data Inspector на вкладке Simulation, чтобы сравнить сигналы, регистрируемые во время основанной на хост-машине симуляции и PIL симуляции (выполняемый на цели). Это помогает вам проверить точность основанной на хост-машине симуляции и PIL симуляции.

Этот график сравнивает сигналы обратной связи скорости от Текущего Управления (PIL) и Текущих подсистем Управления.

Если время выполнения превышает 60% планируемого времени, мы рекомендуем, чтобы вы оптимизировали алгоритм с помощью одного из этих методов:

Выполнитесь от RAM.

Разгрузите некоторые функциональности к CLA или другим центральным процессорам.

Масштабируйте алгоритм, чтобы запуститься в каждом альтернативном цикле.

Переместите менее критические функциональности как расчет скорости к более медленному уровню.

Для получения дополнительной информации о верификации кода SIL/PIL см.: