Simulink® может добавить скрытый буфер сигнала перед блоком Outport в условной подсистеме или перед блоком Outport на верхнем уровне модели. Этот буфер гарантирует сопоставимую инициализацию блока-сигнала Outport.

В нескольких случаях, добавляя буфер сигнала с условным выходным сигналом или частичным сигналом записи может вызвать различный результат симуляции. Параметр Ensure outport is virtual является опцией на блоке Outport, чтобы демонтировать буфер. Выберите эту опцию, когда вы будете обеспокоены условными или частичными сигналами записи.

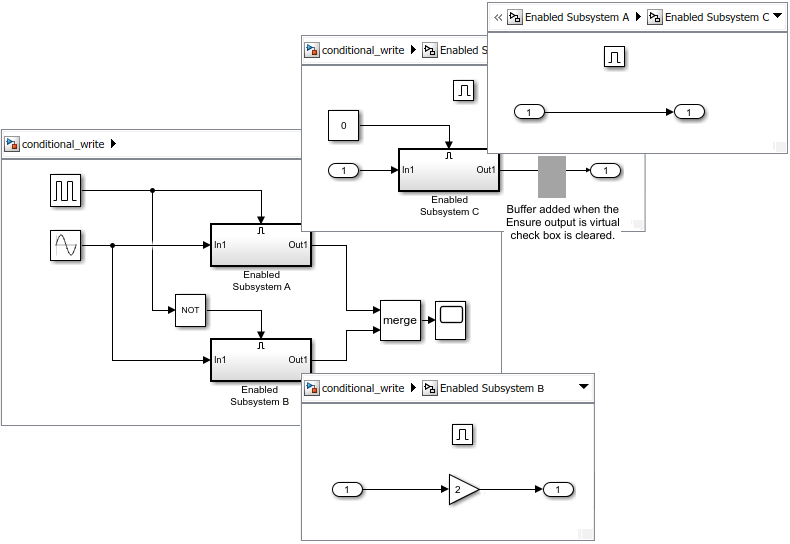

Рассмотрите следующую модель. Open model.

Блок Merge комбинирует свои входные параметры в один сигнал, значение которого в любое время равно последний раз вычисленному выходу своих ведущих блоков.

Для случая с большинством моделей снимите флажок Ensure outport is virtual на блоке Outport, соединенном с Enabled Subsystem C.

Блок Outport следует за невиртуальной семантикой. Скрытый буфер вставляется в случае необходимости перед блоком Outport.

Буфер обеспечивает сопоставимую инициализацию блока-сигнала Outport.

Время 0: A запуски, C не запускается, но потому что буфер находится в A, это запускает и копирует начальное значение нуля с блоком Outport. B не запускается. Сигнал слияния является нулем от выхода от A.

Время 0.5: A не запускается. B запуски и выходные параметры синусоида. Сигнал слияния является синусоидой от B.

Время 1. A запуски, C не запускается, но буфер снова запускает и копирует по начальному значению нуля с блоком Outport. B не запускается. Сигнал слияния является снова начальным значением A, не последнее значение от B.

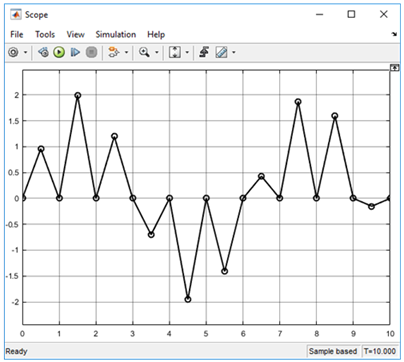

При симуляции модели с фиксированным шагом, приводит к следующему результату.

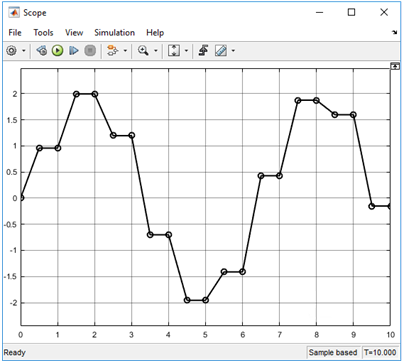

Для случая, где вы обеспокоены условным выражением и частичными записями, выберите (проверяют) флажок Ensure outport is virtual на блок Outport, соединенный с Enabled Подсистемой C.

Блок Outport следует за виртуальной семантикой.

Скрытый буфер не вставляется перед блоком Outport Подсистемы.

Если Simulink решает, что буфер необходим, ошибка отображена.

Время 0: A запуски, C не запускается. B не запускается. Сигнал слияния является начальным значением сигнала.

Время 0,5 секунды: A не запускается. B запуски и выходные параметры синусоида. Сигнал слияния является значением синусоиды от B.

Время 1: A запуски, C не запускается. B не запускается. Сигналом слияния является последний раз вычисленный выход, который был синусоидой от B.

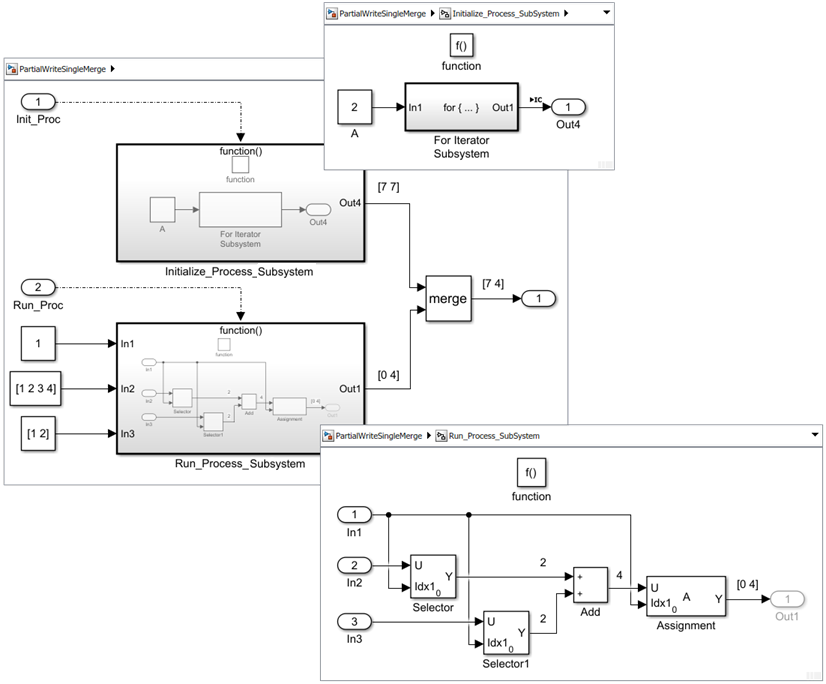

Типичный шаблон моделирования - то, где вы хотите инициализировать векторный сигнал и затем периодически обновлять частичные элементы сигнала, основанного на определенных обстоятельствах или входных параметрах. Один способ смоделировать этот шаблон состоит в том, чтобы использовать блок Merge, входные параметры которого от двух блоков Function-Call Subsystem. Одна подсистема является инициализировать задачей, в то время как другая подсистема является периодической задачей записи.

Модель ниже демонстрирует этот шаблон. Initialize_Process_Subsystem называется однажды в начале симуляции, чтобы инициализировать векторный сигнал. Run_Process_Subsystem называется, чтобы частично записать в элементы вектора. Однако для выхода от блока Assignment нужен путь, где скрытые буферы не делают копии вектора. Установка флажка Ensure outport is virtual на блоке Outport демонтирует скрытый буфер. Если Simulink решает, что буфер необходим, ошибка отображена. Open model.

Initialize_Process_SubSystem

Инициализирует каждый элемент 2 векторов элемента со значением 7.

Выводит векторный [7 7].

Run_Process_Subsystem

Вводит значение индекса 1, но потому что параметр Index mode для блоков Selector устанавливается на Zero-based, они выбирают 2-е элементы из входных векторов.

Добавляют выходные скалярные значения от блоков Selector для результата 4.

Поскольку блок Assignment параметр Index mode установлен в Zero-based и входным индексом Idx1 является 1, выходной сигнал должен быть вектором с длиной 2. После установки параметра Output size на 2, блок Assignment может записать в 2-й элемент.

Выбор флажка Ensure outport is virtual демонтирует скрытый буфер.

Код, сгенерированный из этой модели, включает две функции. Init_Proc и Run_Proc.

/* Model step function */

void Init_Proc(void)

{

int32_T s3_iter;

/* Initialize signal vector elements with 7.0 */

for (s3_iter = 0; s3_iter < 2; s3_iter++) {

PartialWriteSingleMerge_DW.Assignment[s3_iter] = 7.0;

}

for (s3_iter = 0; s3_iter < 2; s3_iter++) {

PartialWriteSingleMerge_Y.Out4[s3_iter] =

PartialWriteSingleMerge_DW.Assignment[s3_iter];

}

}

/* Model step function */

void Run_Proc(void)

{

/* Write to element 1 of the output signal vector */

PartialWriteSingleMerge_Y.Out4[1] = 4.0;

}