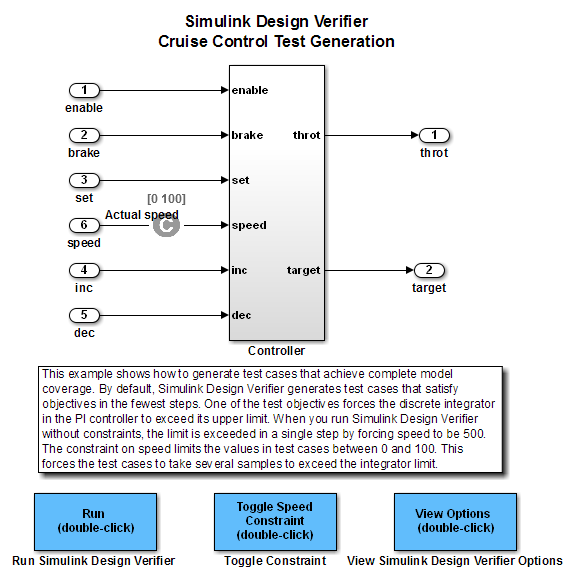

Следующие разделы описывают модель в качестве примера, Генерацию тестов Круиз-контроля. Этот пример иллюстрирует, как использовать Simulink® Design Verifier™, чтобы сгенерировать тесты, которые достигают полного покрытия модели. Через этот пример вы изучаете, как анализировать модели с Simulink Design Verifier и интерпретировать результаты.

Чтобы открыть модель Cruise Control Test Generation, в MATLAB® запрашивают, введите:

Чтобы сгенерировать тесты для модели Cruise Control Test Generation, откройте окно модели и дважды кликните, блок пометил Run.

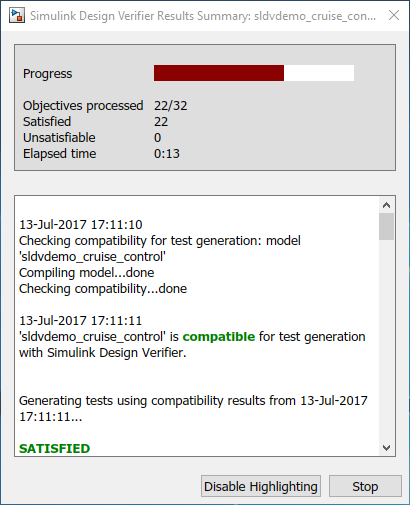

Simulink Design Verifier начинает анализировать модель, чтобы сгенерировать тесты, и окно Simulink Design Verifier Results Summary открывается. Окно Results Summary отображает синхронный журнал, показывающий прогресс анализа.

Если необходимо отключить анализ, в то время как он запускается, нажмите Stop. Программное обеспечение спрашивает, хотите ли вы привести к результатам. Если вы нажимаете Yes, программное обеспечение создает файл данных на основе результатов, достигнутых до сих пор. Путь файла данных появляется в окне Results Summary.

Файлом данных является MAT-файл, который содержит структуру под названием sldvData. Эта структура хранит данные, которые программное обеспечение собирает и производит во время анализа.

Для получения дополнительной информации смотрите Файлы данных Simulink Design Verifier.

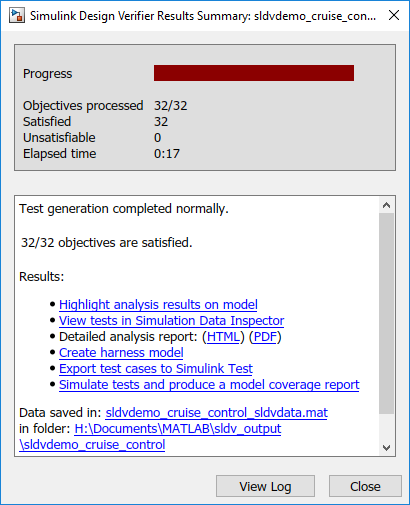

Когда Simulink Design Verifier завершает свой анализ sldvdemo_cruise_control модель, окно Results Summary отображает несколько опций:

Highlight analysis results on model

Generate detailed analysis report

Create harness model

Simulate tests and produce a model coverage report

Когда вы анализируете другие модели, в зависимости от результатов анализа, можно видеть подмножество этих четырех опций.

Разделы, которые следуют, описывают эти опции подробно.

В окне Simulink Design Verifier Results Summary, если вы нажимаете Highlight analysis results on model, объекты подсветок программного обеспечения в модели в трех различных цветах, в зависимости от результатов анализа:

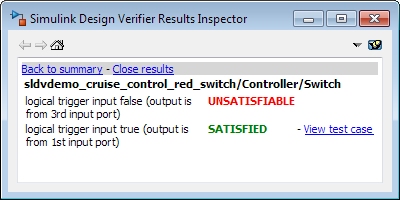

Когда вы подсвечиваете результаты анализа на модели, Инспектор Результатов Simulink Design Verifier открывается. Когда вы кликаете по объекту в модели, которая имеет результаты анализа, Инспектор Результатов отображает сводные данные результатов для того объекта.

Зеленый: Удовлетворенные Цели. Зеленая схема указывает, что анализ сгенерировал тесты для всех целей для того блока. Если блок является подсистемой или Stateflow® атомарный подграфик, зеленая схема указывает, что анализ сгенерировал тесты для всех целей, сопоставленных с дочерними объектами.

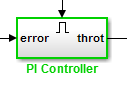

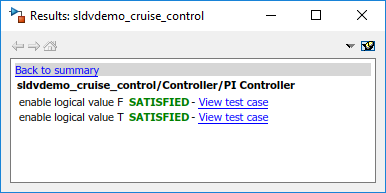

Например, в sldvdemo_cruise_control модель, зеленая схема показывает, что подсистема ПИ-контроллера удовлетворила всем целям тестирования. Инспектор Результатов перечисляет две цели тестирования, которым удовлетворяют, для подсистемы ПИ-контроллера.

Оранжевый: Нерешенные Цели. Оранжевая схема указывает, что анализ не смог определить, была ли цель выполнима или нет. Эта ситуация может произойти когда:

Анализ испытывает таймаут

Программное обеспечение удовлетворяет целям тестирования, не генерируя тесты из-за:

Автоматические блокирующие ошибки

Ограничения аналитического механизма

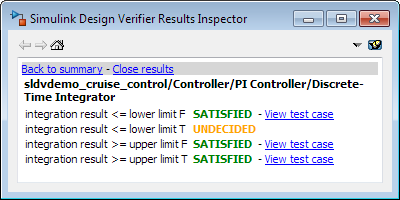

В следующем примере испытал таймаут анализ, прежде чем это могло определить, была ли одна из целей для блока Discrete-Time Integrator выполнима.

Красный: Невыполнимые Цели. Красная схема указывает, что анализ нашел некоторые цели, для которых это не могло сгенерировать тесты, скорее всего, из-за недостижимых элементов дизайна в вашей модели.

В следующем примере вход 2 всегда удовлетворяет критерию блока Switch, таким образом, блок Switch никогда не проходит через значение входа 3.

В окне Simulink Design Verifier Results Summary, если вы нажимаете Generate detailed analysis report, программное обеспечение сохраняет и затем открывает подробный отчет об анализе. Путь к отчету:

<current_folder>/sldv_output/...

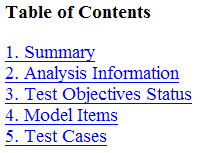

sldvdemo_cruise_control/sldvdemo_cruise_control_report.htmlОтчет HTML включает следующие главы.

Для описания каждой главы отчета см.:

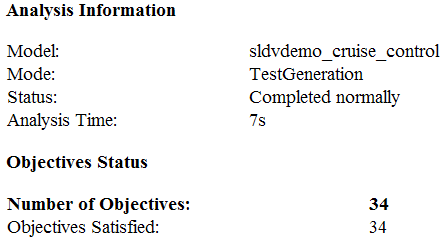

Сводные данные. В Table of Contents нажмите Summary, чтобы отобразить Итоговую главу, которая включает следующую информацию:

Имя модели

Режим анализа (генерация тестов, доказательство свойства, поиск ошибок проектирования)

Состояние анализа

Продолжительность анализа в секундах

Количеству целей удовлетворяют

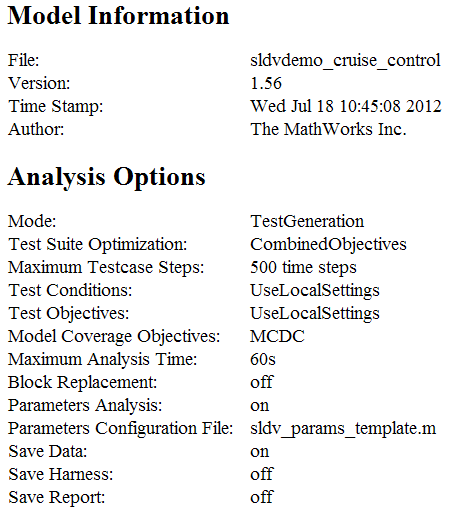

Информация об анализе. В Table of Contents нажмите Analysis Information, чтобы отобразить информацию об анализируемой модели и аналитических опциях.

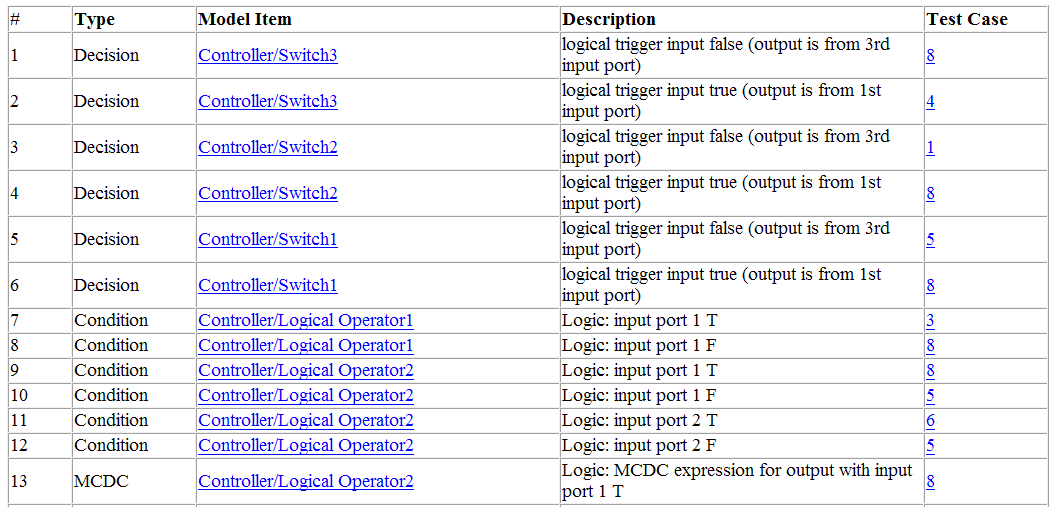

Состояние Целей тестирования. В Table of Contents нажмите Test Objectives Status, чтобы отобразить таблицу целей, которым удовлетворяют. Следующий рисунок показывает частичный список целей, которым удовлетворяют в модели Cruise Control Test Generation.

Состояние целей

Таблица Objectives Satisfied приводит следующую информацию для модели:

# — Объективный номер

Ввод Объективный тип

Model Item — Элемент в модели, на которую была протестирована цель. Щелкните по этой ссылке, чтобы отобразить модель с этим подсвеченным элементом.

Описание Описание цели

Test Case — Тест, который достигает цели. Щелкните по этой ссылке для получения дополнительной информации о том тесте.

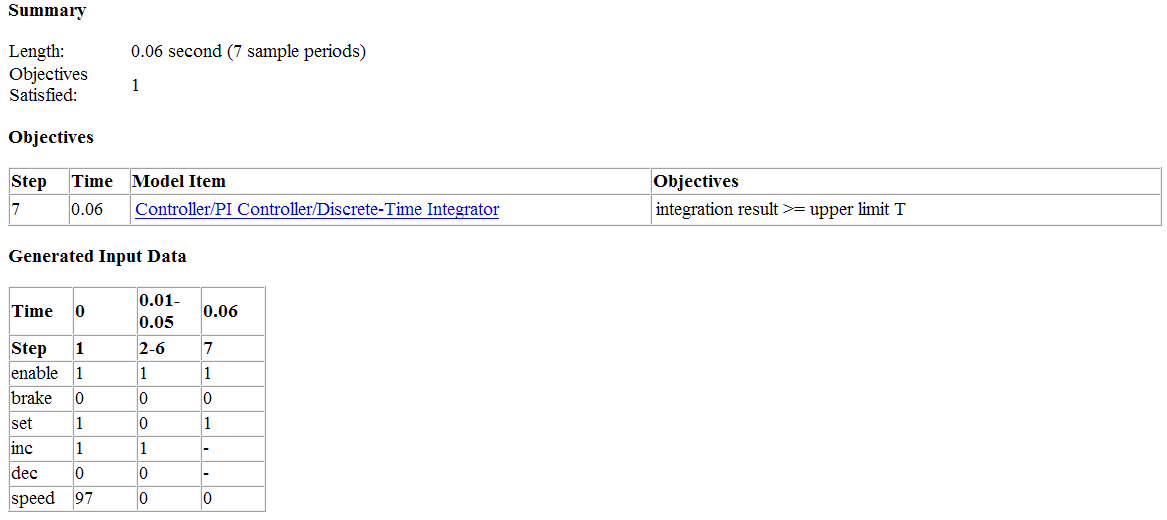

В строке для объективных 34 кликните по номеру теста (7), чтобы отобразить больше информации о Тесте 7 в главе Test Cases отчета.

Тест 7

В этом примере Тест 7 удовлетворяет одной цели, что результат интегрирования быть больше или быть равным верхнему пределу T в блоке Discrete-Time Integrator. Таблица приводит значения шести сигналов со времени 0 в течение времени 0.06.

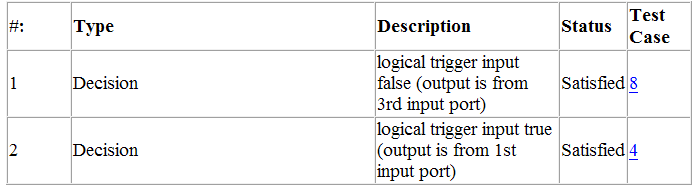

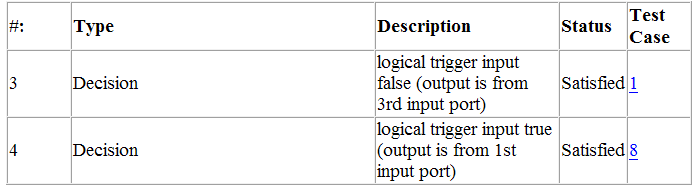

Элементы модели. В Table of Contents нажмите Model Items, чтобы видеть подробную информацию о каждом элементе в модели, которая задает цели покрытия. Эта таблица включает состояние цели в конце анализа. Щелкните по ссылкам в таблице для получения дальнейшей информации о целях, которым удовлетворяют.

Элементы модели - Controller/Switch3

Элементы модели - Controller/Switch2

Тесты. В Table of Contents нажмите Test Cases, чтобы отобразить подробную информацию о каждом сгенерированном тесте, включая:

Отрезок времени, чтобы выполнить тест

Количеству целей удовлетворяют

Подробная информация о целях, которым удовлетворяют,

Входные данные

Для примера смотрите раздел для Теста 7 в Состоянии Целей тестирования.

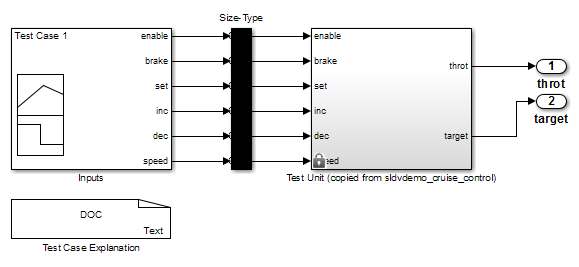

В окне Simulink Design Verifier Results Summary, если вы нажимаете Create harness model, программное обеспечение создает и открывает модель тестовой обвязки под названием sldvdemo_cruise_control_harness.

Модель тестовой обвязки содержит следующие блоки:

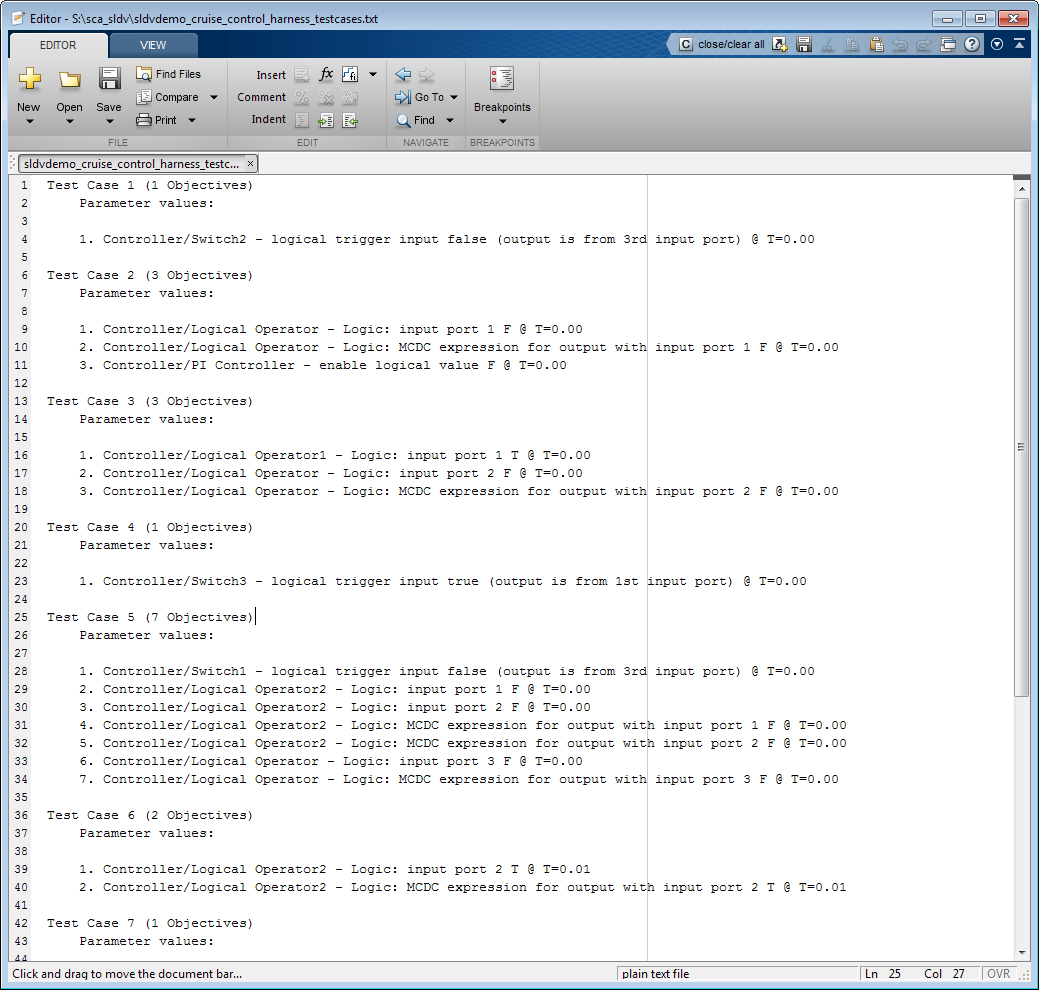

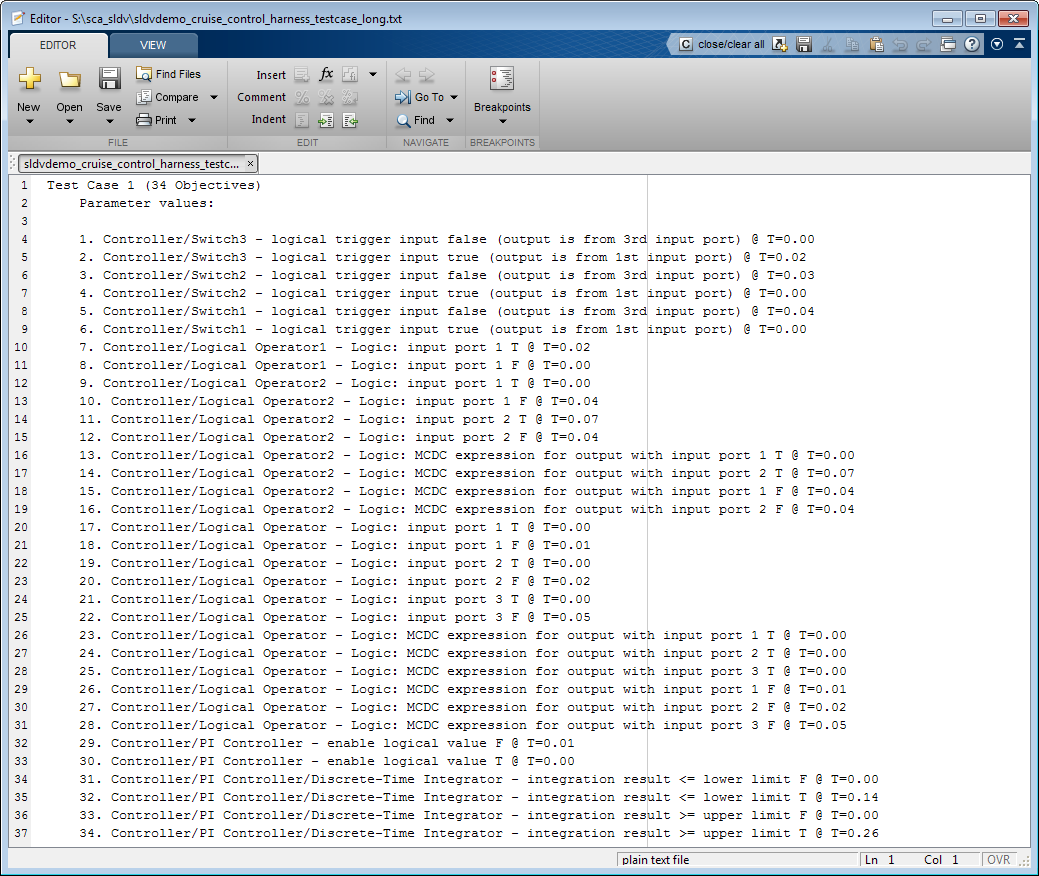

Блок Test Case Explanation является блоком DocBlock, который документирует сгенерированные тесты. Дважды кликните блок Test Case Explanation, чтобы просмотреть описание каждого теста для целей, которым удовлетворяет тест.

Блок Test Unit является блоком Subsystem, который содержит копию исходной модели, которую анализировало программное обеспечение. Дважды кликните блок Test Unit, чтобы просмотреть его содержимое и подтвердить, что это - копия модели Cruise Control Test Generation.

Можно сконфигурировать модель тестовой обвязки, чтобы сослаться на модель, что вы анализируете использование блока Model вместо того, чтобы использовать подсистему. В диалоговом окне Configuration Parameters, на панели Design Verifier > Results, выбирают Generate separate harness model after analysis и Reference input model in generated harness.

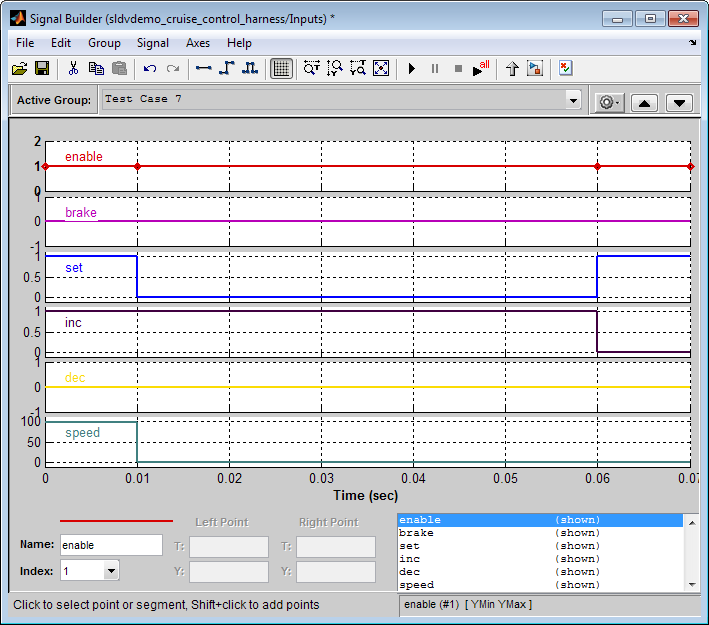

Блок Inputs является блоком Signal Builder, который содержит сгенерированные сигналы теста. Дважды кликните блок Inputs, чтобы открыть диалоговое окно Signal Builder и просмотреть восемь сигналов теста.

Блок Size-Type является подсистемой, которая передает сигналы от блока Inputs до блока Test Unit. Этот блок проверяет, что размер и тип данных сигналов сопоставимы с блоком Test Unit.

Диалоговое окно Signal Builder содержит восемь тестов.

К представлению Test Case 7, из списка Active Group, выбирают Test Case 7.

В Тесте 7 в 0,01 секунды:

Разрешение и сигналы inc остаются 1.

Тормоз и сигналы в декабре остаются 0.

Переходы сигнала набора от 1 до 0.

Переходы сигнала скорости от 100 до 0.

В блоке Signal Builder группа сигнала удовлетворяет целям тестирования, описанным в блоке Test Case Explanation.

Чтобы подтвердить что Simulink Design Verifier достигнутое полное покрытие модели, симулируйте модель тестовой обвязки с помощью всех тестов. В диалоговом окне Signal Builder нажмите кнопку Run all and produce coverage![]() .

.

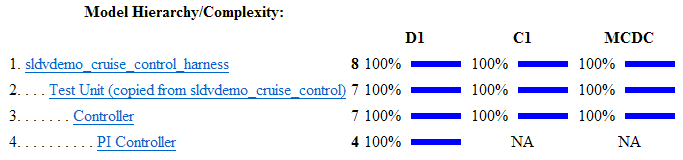

Программное обеспечение Simulink симулирует все тесты. Программное обеспечение Simulink Coverage™ собирает данные о покрытии для модели тестовой обвязки и отображает отчет покрытия. Сводные данные отчета показывают что sldvdemo_cruise_control_harness модель достигает 100%-го покрытия.

Сводные данные

В окне Simulink Design Verifier Results Summary, если вы нажимаете Simulate tests and produce a model coverage report, программное обеспечение симулирует модель и представляет отчет покрытия для sldvdemo_cruise_control модель. Программное обеспечение хранит отчет следующим именем:

<current_folder>/sldv_output/sldvdemo_cruise_control/... sldvdemo_cruise_control_report.html

Когда вы нажимаете Run all and produce coverage, чтобы симулировать тесты в модели тестовой обвязки, можно видеть следующие различия между этим отчетом покрытия и отчетом, который вы сгенерировали для самой модели:

Отчет покрытия модели тестовой обвязки может содержать дополнительные временные шаги. Когда вы собираете покрытие для модели тестовой обвязки, время остановки модели равняется времени остановки для самого длинного теста. В результате вы можете достигнуть дополнительного покрытия, когда вы симулируете более короткие тесты.

Цикломатическое покрытие сложности для Тестовой Модульной подсистемы в модели тестовой обвязки может отличаться, чем покрытие для самой модели из-за структуры модели тестовой обвязки.

Если вы предпочитаете рассматривать результаты, которые объединены в меньшее число тестов, установите параметр Test suite optimization на LongTestcases. Когда вы используете LongTestcases оптимизация, анализ генерирует меньше, но дольше, тесты, что каждый удовлетворяет нескольким целям тестирования.

Откройте sldvdemo_cruise_control модель и повторно выполненный анализ с LongTestcases оптимизация:

На вкладке Design Verifier, в разделе Prepare, в выпадающем меню для настроек режима, нажимают Settings.

В диалоговом окне Configuration Parameters, в дереве Select на левой стороне, под категорией Design Verifier, выбирают Test Generation.

Установите параметр Test suite optimization на LongTestcases.

Нажмите Apply и OK, чтобы закрыть диалоговое окно Configuration Parameters.

В sldvdemo_cruise_control модель, дважды кликните, блок пометил Run.

В окне Results Summary нажмите Create harness model.

В модели тестовой обвязки блок Signal Builder и блок Test Case Explanation теперь содержат один более длинный тест вместо восьми более коротких тестов, созданных ранее в, Генерируют Тесты.

Нажмите Run all and produce coverage, чтобы собрать покрытие.

Анализ все еще удовлетворяет всем 34 целям.