Прежде чем вы симулируете модель, используйте обнаружение мертвой логики, чтобы анализировать модель для мертвой логики. В Simulink® Design Verifier™ поиск ошибок проектирования для мертвой логики состоит из двух аналитических опций:

Обнаружение мертвой логики только: Если вы выбираете эту опцию, Simulink Design Verifier анализирует вашу модель, не делая приближений, таких как рациональное приближение для плавающих точек или приближение цикла с условием продолжения. Для получения дополнительной информации смотрите Приближения. При использовании этой опции Simulink Design Verifier не сообщает об активных логических или нерешенных целях, и это не может идентифицировать некоторую мертвую логику в вашей модели.

Эта опция доступна в:

Model Advisor. Смотрите Проверку На Ошибки проектирования с помощью Model Advisor.

Диалоговое окно Configuration Parameters, на Верификаторе Проекта> панель Поиска ошибок проектирования.

Обнаружение активной логики: Активное логическое обнаружение запускается одновременно с обнаружением мертвой логики. При использовании этой опции Simulink Design Verifier сообщает об активной логике в дополнение к мертвой логике, а также нерешенным целям. Эта опция может в некоторых случаях идентифицировать или найти дополнительную мертвую логику. Анализ может использовать приближения и сообщается соответственно.

Эта опция доступна в диалоговом окне Configuration Parameters на Верификаторе Проекта> панель Поиска ошибок проектирования.

Если вы не используете Model Advisor, чтобы обнаружить мертвую логику:

На вкладке Design Verifier, в разделе Mode, выбирают Design Error Detection.

Нажмите Error Detection Settings.

В диалоговом окне Configuration Parameters, на Верификаторе Проекта> панель Поиска ошибок проектирования:

Включите опцию Мертвой логики.

Очистите Идентифицирование активной логической опции, если это выбрано.

Чтобы применить эти настройки, нажмите OK и закройте диалоговое окно Configuration Parameters.

Нажмите Detect Design Errors.

На вкладке Design Verifier, в разделе Mode, выбирают Design Error Detection.

Нажмите Error Detection Settings.

В диалоговом окне Configuration Parameters, на Верификаторе Проекта> панель Поиска ошибок проектирования, включают Мертвую логику и Идентифицируют активные логические опции.

Чтобы применить эти настройки, нажмите OK и закройте диалоговое окно Configuration Parameters.

Нажмите Detect Design Errors.

В этом примере показано, как обнаружить мертвую логику в sldvSlicerdemo_dead_logic модель в качестве примера. Обнаружение мертвой логики находит недостижимые цели в модели, которые заставляют элемент модели оставаться неактивным.

Откройте sldvSlicerdemo_dead_logic модель.

open_system('sldvSlicerdemo_dead_logic');На вкладке Design Verifier, в разделе Mode, выбирают Design Error Detection.

Нажмите Error Detection Settings.

В диалоговом окне Configuration Parameters, на Верификаторе Проекта> панель Поиска ошибок проектирования, включают опцию Мертвой логики, и ясный Идентифицируют активную логическую опцию.

Нажмите Detect Design Errors.

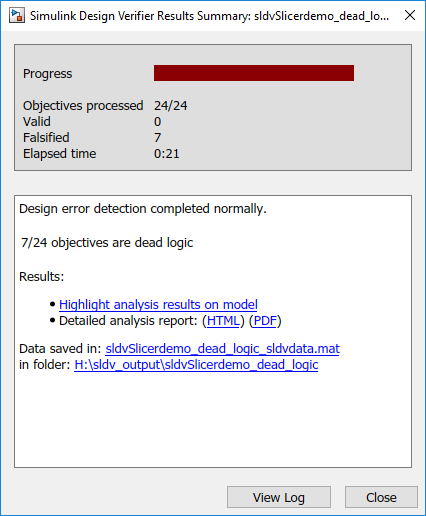

Программное обеспечение анализирует модель для мертвой логики и отображает результаты в окне Results Summary. Результат показывает что семь из 24 цели являются мертвой логикой.

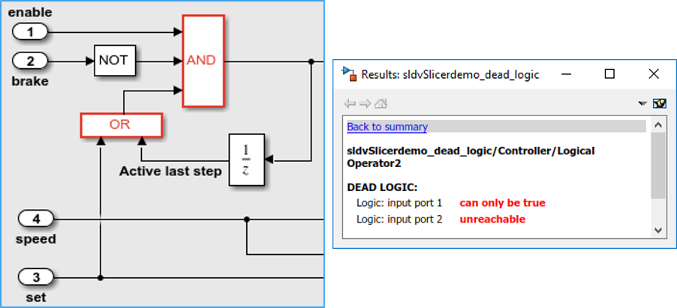

Нажмите Highlight analysis results on model. Элементы модели мертвой логики подсвечены в красном.

Откройте Controller

subsystem и нажатие кнопки блок OR, подсвеченный в красном. Инспектор Результата отображает сводные данные мертвой логики.

set вход равен 1, так input port 1 из блока OR can only be true. Состояние подразумевает что input port 1 ложным условием является мертвая логика. Точно так же input port 2 unreachable, когда цель никогда не выполняется и является мертвой логикой.

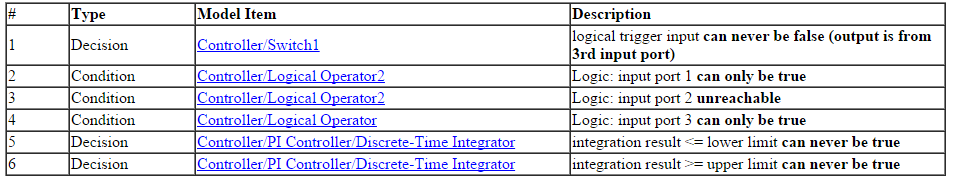

Чтобы просмотреть отчет детального анализа, в окне Results Summary, нажимают HTML.

Отчет отображает сводные данные всех результатов, которые являются мертвой логикой в модели.

Мертвая логика

Программное обеспечение хранит результаты детального анализа в DeadLogic field в Файлах данных Simulink Design Verifier. Можно использовать файл данных в последующем анализе результатов.