Интерфейс черного квадрата для подсистемы является сгенерированным компонентом VHDL® или модулем Verilog®, который включает только определения порта ввода и вывода HDL для подсистемы. Путем генерации такого компонента можно использовать подсистему в модели, чтобы сгенерировать интерфейс к существующему вручную записанному HDL-коду, стороннему IP или другому коду, сгенерированному HDL Coder™.

Реализация черного квадрата доступна только для блоков подсистемы ниже уровня DUT. Блоки виртуальной и атомарной подсистемы пользовательских библиотек, которые являются ниже уровня DUT также, работают с реализациями черного квадрата.

Можно сгенерировать самое большее один порт часов, и часы включают порт для подсистемы черного квадрата. Поэтому подсистема черного квадрата должна быть односкоростной, даже если это находится в многоскоростном DUT.

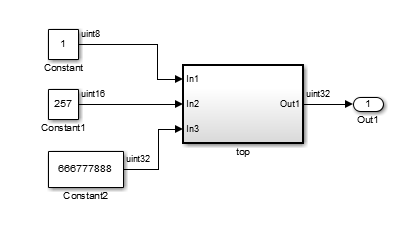

Чтобы сгенерировать интерфейс, выберите BlackBox реализация для одного или нескольких блоков Subsystem. Рассмотрите следующую модель, которая содержит подсистему top, который является устройством под тестом.

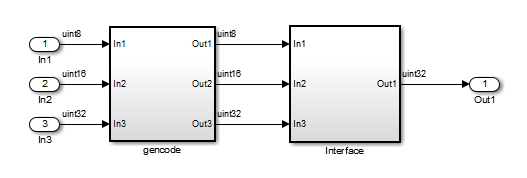

Подсистема top содержит две подсистемы низшего уровня:

Предположим, что вы хотите сгенерировать HDL-код от top, с черным квадратом взаимодействуют через интерфейс от Interface подсистема. Задавать интерфейс черного квадрата:

Щелкните правой кнопкой по Interface подсистема и выбирает HDL Code> HDL Block Properties.

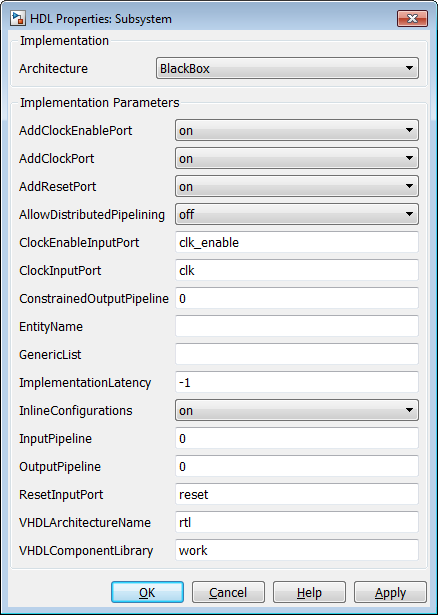

Диалоговое окно HDL Properties появляется.

Установите Architecture на BlackBox.

Следующие параметры доступны для реализации черного квадрата:

Параметры блоков HDL, доступные для реализации черного квадрата, позволяют вам настроить сгенерированный интерфейс. Смотрите Настраивают Черный квадрат или HDL Интерфейс Cosimulation для получения информации об этих параметрах.

Измените параметры, как желаемый и нажмите Apply.

Нажмите OK, чтобы закрыть диалоговое окно HDL Properties.

Когда вы генерируете код для DUT в ex_blackbox_subsys модель, следующие сообщения появляются:

>> makehdl('ex_blackbox_subsys/top')

### Generating HDL for 'ex_blackbox_subsys/top'

### Starting HDL Check.

### HDL Check Complete with 0 errors, 0 warnings and 0 messages.

### Begin VHDL Code Generation

### Working on ex_blackbox_subsys/top/gencode as hdlsrc\gencode.vhd

### Working on ex_blackbox_subsys/top as hdlsrc\top.vhd

### HDL Code Generation Complete.В сообщениях о ходе выполнения заметьте что gencode подсистема генерирует отдельный файл, gencode.vhd, для его определения сущности VHDL. Interface подсистема не генерирует такой файл. Интерфейсный код для этой подсистемы находится в top.vhd, сгенерированный от ex_blackbox_subsys/top. Следующий листинг кода показывает определение компонента и инстанцирование, сгенерированное для Interface подсистема.

COMPONENT Interface

PORT( clk : IN std_logic;

clk_enable : IN std_logic;

reset : IN std_logic;

In1 : IN std_logic_vector(7 DOWNTO 0); -- uint8

In2 : IN std_logic_vector(15 DOWNTO 0); -- uint16

In3 : IN std_logic_vector(31 DOWNTO 0); -- uint32

Out1 : OUT std_logic_vector(31 DOWNTO 0) -- uint32

);

END COMPONENT;

...

u_Interface : Interface

PORT MAP( clk => clk,

clk_enable => enb,

reset => reset,

In1 => gencode_out1, -- uint8

In2 => gencode_out2, -- uint16

In3 => gencode_out3, -- uint32

Out1 => Interface_out1 -- uint32

);

enb <= clk_enable;

ce_out <= enb;

Out1 <= Interface_out1;

По умолчанию интерфейс черного квадрата, сгенерированный для подсистем, включает часы, часы включают и сбрасывают порты. Настройте Черный квадрат или HDL, который описывает Козимулэйшн Интерфэс, как можно переименовать или подавить генерацию этих сигналов и настроить другие аспекты сгенерированного интерфейса.