Если ваша модель Simulink® содержит несколько частот дискретизации или использует скорость и оптимизацию области, которая вставляет конвейерные регистры, ваш проект может иметь мультивелосипедные дорожки. Мультивелосипедные дорожки являются информационными каналами между двумя регистрами, которые действуют на уровне частоты дискретизации медленнее, чем тактовая частота FPGA и поэтому берут несколько тактов, чтобы завершить их выполнение. Чтобы синхронизировать тактовую частоту с частотами дискретизации различных путей в вашем проекте, можно использовать один режим тактовой синхронизации или режим тактовой синхронизации кратного. По умолчанию HDL Coder™ использует один режим тактовой синхронизации, который генерирует один основной тактовый генератор на уровне самой быстрой частоты дискретизации и создает контроллер синхронизации сущность, чтобы управлять тактовой частотой к мультивелосипедным дорожкам. Контроллер синхронизации генерирует набор часов, включает с необходимым уровнем и информацией о фазе, чтобы управлять последовательными элементами, такими как блоки Delay, которые действуют на уровне различных частот дискретизации.

Когда вы синтезируете сгенерированный HDL-код, инструменты синтеза могут не удовлетворить требования синхронизации мультивелосипедных дорожек. Отказ синхронизации происходит, потому что инструменты синтеза не могут вывести различные частоты дискретизации в вашем проекте от сгенерированного HDL-кода. Инструменты синтеза принимают, что регистры в вашем проекте, запущенном на уровне основного тактового генератора и, требуют, чтобы данные переместились между регистрами в одном такте. Однако мультивелосипедные дорожки не обязаны завершать свое выполнение в одном такте и поэтому не могут удовлетворить требования синхронизации. Чтобы удовлетворить требования синхронизации, укажите, что генерация включает - базирующиеся ограничения тракта мультицикла.

Инструменты синтеза требуют, чтобы данные распространили от исходного регистра до целевого регистра в одном такте. Ограничения тракта мультицикла ослабляют это требование синхронизации, позволяя несколько тактов для данных распространить между регистрами. Использование генератора кода, которое контроллер синхронизации включает сигналам создать, включает - базирующиеся группы регистров, с регистрами в каждой группе, управляемой теми же часами, включают. Когда вы применяете разрешение - базирующиеся ограничения и генерируете HDL-код, генератор кода выводит ограничительный файл с соглашением о присвоении имен dutname_constraints. Файл задает требования синхронизации мультивелосипедных дорожек и содержит информацию о настройке, и содержите ограничения, которому нужно соответствовать.

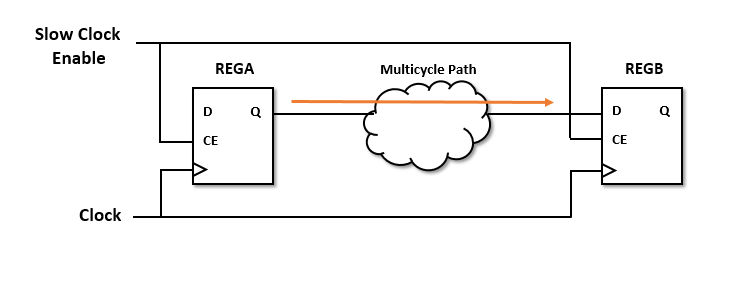

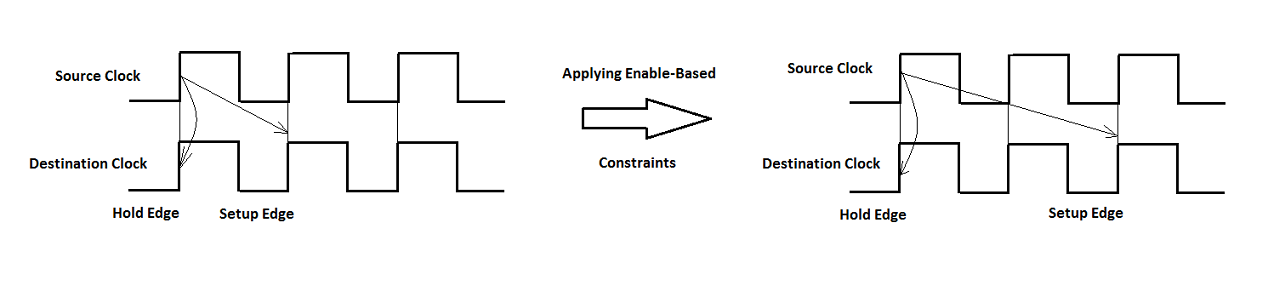

Этот рисунок показывает мультивелосипедную дорожку, которая берет определенное число тактов, скажите N, для данных, чтобы распространить от REGA к REGB. По умолчанию инструменты синтеза задают ребро настройки в следующем активном фронте синхроимпульса и ребро хранения в том же активном фронте синхроимпульса относительно целевого сигнала часов. Для мультивелосипедной дорожки, которая берет N такты, ограничения переопределяют настройку и содержат ребро, чтобы допускать более длительное время распространения данных.

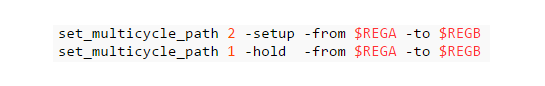

Например, полагайте, что мультивелосипедная дорожка берет два такта для верхней части данных, распространяют от источника до целевого регистра. Эта форма волны показывает, как применение включает - базирующиеся ограничения переопределяют настройку, и содержите ребра. Этот фрагмент кода показывает эту настройку, и содержите требование в ограничительном файле, который сгенерирован, когда вы включаете ограничения тракта мультицикла.

Прежде чем вы сгенерируете разрешение - базирующиеся ограничения, вы должны:

Сохраните пути к мультициклу в своем проекте. Прежде чем вы включите генерацию ограничений тракта мультицикла, убедитесь, что вы отключаете оптимизацию, такую как конвейеризация тактовой частоты и адаптивная конвейеризация в тех областях, где вы хотите применить ограничения тракта мультицикла.

Убедитесь, что область, которая действует на более медленной тактовой частоте, ограничена путем синхронизации основанных на диспетчере часов, включают сигналы, действующие в нулевой фазе.

Задайте Synthesis tool. Формат ограничительного файла мультивелосипедной дорожки, который сгенерирован, зависит от Synthesis tool, который вы задаете. Если вы не задаете инструмент синтеза, и флажок Generate EDA Scripts устанавливается, HDL Coder не генерирует ограничения мультивелосипедной дорожки.

Используйте один режим тактовой синхронизации. В HDL Code Generation> панель Global Settings, набор Clock Inputs к Single.

Можно задать генерацию ограничений мультицикла в диалоговом окне Configuration Parameters, или в HDL Workflow Advisor пользовательский интерфейс, или в командной строке.

В диалоговом окне Configuration Parameters, на HDL Code Generation> панель Target and Optimizations, устанавливают флажок Enable based constraints.

В HDL Workflow Advisor, на HDL Code Generation> Set Code Generation Options> задача Set Optimization Options, устанавливают флажок Enable based constraints.

В командной строке используйте MulticyclePathConstraints свойство с hdlset_param или makehdl.

Если инструменты синтеза идентифицируют ограничения мультивелосипедной дорожки, вы можете:

Осознайте более высокие тактовые частоты и улучшите синхронизацию своего проекта.

Уменьшайте место области на целевом устройстве FPGA, потому что ограничения мультивелосипедной дорожки не вводят конвейерных регистров.

Уменьшайте время генерации HDL-кода, потому что генератор кода не должен запускать много настроек оптимизации.

Уменьшайте время синтеза, поскольку ограничения мультивелосипедной дорожки ослабляют требования синхронизации к инструменту синтеза.

Пропустите верификацию своего проекта после генерации HDL-кода, когда сгенерированная модель с ограничениями идентична исходной модели.

Когда вы указываете информацию мультивелосипедной дорожки к инструменту синтеза, не рекомендуется использовать установку информации о пути От регистра к регистру в панели Target and Optimizations. Если вы используете эту установку, генератор кода выводит текстовый файл, который описывает информацию о пути к мультициклу в формате, который не является нативным к конкретному инструменту синтеза. Необходимо преобразовать эту информацию в формат ограничений тракта мультицикла, требуемый инструментом синтеза.

Когда вы используете разрешение - базирующаяся ограничительная установка:

Сгенерированные ограничения более устойчивы к сменам имени в инструментах синтеза.

Генерация HDL-кода быстрее чем тогда, когда вы используете установку информации о пути От регистра к регистру.

Target workflow может быть Generic ASIC/FPGA, FPGA Turnkey, IP Core Generation, и Simulink Real-Time FPGA I/O.

Ограничительный формат файла поддерживается с Xilinx ISE, Xilinx Vivado, и Altera QUARTUS II.

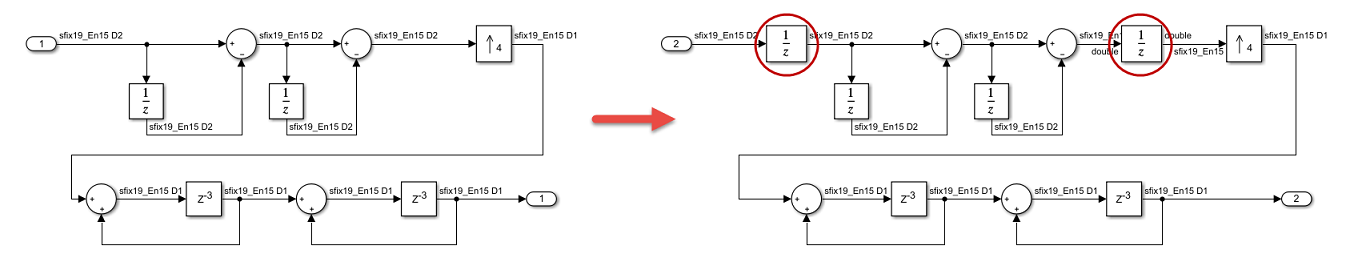

Когда вы указываете, что генерация включает - базирующиеся ограничения, использует эти шаблоны моделирования в вашем проекте. Если ваша модель содержит низкоскоростные области, которые не ограничены регистрами, то добавляют задержки на той же низкой скорости к вводу и выводу низкоскоростных областей. Например, если вы входите hdlcoder_clockdemo в командной строке в MATLAB® вы видите многоскоростной фильтр Интерполяции CIC, реализованный в одном режиме тактовой синхронизации. Этот рисунок показывает как связанному ввод и вывод низкоскоростной области, аннотируемой медленным шагом расчета D2 в модели с блоками Unit Delay так, чтобы разрешение - базирующиеся ограничения могло идентифицировать низкоскоростной путь.

Примечание

Можно использовать блоки Rate Transition, чтобы ввести регистры ввода и вывода, но убедиться, что регистры являются низкой скоростью и имеют нулевую фазу.

Включите - базирующиеся ограничения тракта мультицикла имеют различные форматы файлов, которые зависят от Synthesis tool, который вы задаете.

HDL Coder генерирует ограничения в форме SDC файл. Этот фрагмент кода показывает SDC файл сгенерирован для Altera® Quartus® II.

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0 set enbreg [get_registers *u_DUT_tc|phase_0] set_multicycle_path 4 -to [get_fanouts $enbreg -through [get_pins -hier *|ena]] -end -setup set_multicycle_path 3 -to [get_fanouts $enbreg -through [get_pins -hier *|ena]] -end -hold

HDL Coder генерирует ограничения в форме XDC файл. Этот фрагмент кода показывает XDC файл сгенерирован для Xilinx® Vivado®.

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0

set enbregcell [get_cells -hier -filter {mcp_info=="DUT_tc.u1_d4_o0"}]

set enbregnet [get_nets -of_objects [get_pins -of_objects $enbregcell -filter {DIRECTION == OUT}]]

set reglist [get_cells -of [filter [all_fanout -flat -endpoints_only $enbregnet] IS_ENABLE]]

set_multicycle_path 4 -setup -from $reglist -to $reglist -quiet

set_multicycle_path 3 -hold -from $reglist -to $reglist -quietОграничительная форма мультивелосипедной дорожки включает - базирующиеся группы регистров путем запроса списка соединений синтеза для ATTRIBUTE ключевое слово. Этот фрагмент кода показывает это ключевое слово в списке соединений синтеза, когда вы запускаете любой из поддерживаемых целевых рабочих процессов.

... ATTRIBUTE mcp_info: string ATTRIBUTE mcp_info OF phase_0 : SIGNAL IS "DUT_tc.u1_d4_o0"; ...

HDL Coder генерирует ограничения в форме UCF файл. Этот фрагмент кода показывает UCF файл сгенерировал для модели, которой управляли одной низкоскоростной областью часы, включают сигнал, и имеет целевую частоту 300MHz. Отрывок показывает, что ограничения мультивелосипедной дорожки зависят от Target Frequency, который вы задаете.

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0 NET "*u_DUT_tc/phase_0" TNM_NET = FFS "TN_u_DUT_tc_phase_0"; TIMESPEC "TS_u_DUT_tc_phase_0" = FROM "TN_u_DUT_tc_phase_0" TO "TN_u_DUT_tc_phase_0" TS_FPGA_CLK/4;

Этот фрагмент кода показывает ограничения часов, которые сгенерированы, когда вы запускаете Generic ASIC/FPGA, FPGA Turnkey, или Simulink Real-Time FPGA I/O рабочий процесс с Xilinx ISE.

# Timing Specification Constraints NET "clk" TNM_NET = "TN_clk"; TIMESPEC "TS_FPGA_CLK" = PERIOD "TN_clk" 300 MHz;

Использовать ограничения мультивелосипедной дорожки, когда вы генерируете HDL-код при помощи makehdl функционируйте, убедитесь, что вы добавляете TS_FPGA_CLK ограничение к UCF файл.

Ограничительный файл мультивелосипедной дорожки не поддерживается с FPGA-in-the-Loop рабочий процесс.

IP Core Generation рабочий процесс не генерирует ограничение часов и поэтому не поддерживает ограничительную генерацию мультивелосипедной дорожки с Xilinx ISE.

Если низкоскоростная область не ограничена регистрами, ограничения мультивелосипедной дорожки требует, чтобы вы добавили два блока Delay на низкой скорости, которая увеличивает задержку вашего проекта.

Генератор кода не добавляет ограничения на пути между регистрами, которые имеют ненулевое значение фазы для базирующегося контроллера синхронизации, включают сигналы. Для генератора кода, чтобы добавить ограничения, используйте регистры, которые выводят из фазы 0 часы включают сигналы, такие как блоки Delay.

Сгенерированные ограничения мультицикла могут быть менее эффективными, если вы применяете ограничения в областях, которые имеют оптимизацию, такую как конвейеризация тактовой частоты, и адаптивная конвейеризация включила. С конвейеризацией тактовой частоты регистры действуют на более быстрой тактовой частоте и поэтому не могут сохранить низкоскоростные регистры в вашем проекте.

HDL Coder не генерирует ограничения мультивелосипедной дорожки для односкоростных моделей.

Генератор кода не выводит ограничительный файл мультивелосипедной дорожки, если вы используете несколько режим тактовой синхронизации.