Когда вы запускаете рабочий процесс элемента кода аппаратного программного обеспечения для платформ SoC, вы генерируете ядро IP HDL для алгоритма DUT, и затем интегрируете ядро IP в исходный проект. Смотрите Рабочий процесс Элемента кода аппаратного программного обеспечения для Платформ SoC.

Чтобы протестировать ядро IP HDL на целевом компьютере, можно сгенерировать скрипт программного интерфейса и модель программного интерфейса. Модель программного интерфейса использует блоки драйверов AXI, чтобы протестировать базовую функциональность IP HDL в симуляции режима external mode. Для быстрого прототипирования используйте скрипт сгенерированного программного обеспечения вместо этого. Скрипт содержит порты DUT и информацию об отображении интерфейса который использование HDL Coder™ создать драйверы AXI и получить доступ к ядру IP HDL.

Используйте целевую платформу, что вы хотите развернуть модель программного интерфейса в, такую как ZedBoard™

Установите последнюю версию стороннего инструмента синтеза, такого как Xilinx® Vivado®, как упомянуто в Поддержке Языка HDL и Поддерживаемых Сторонних программах и Оборудовании. На вашем сеансе MATLAB®, установленном путь к тому установленному инструменту синтеза при помощи hdlsetuptoolpath функция.

Если вы генерируете модель программного интерфейса, необходимо установить Embedded Coder® и Simulink® Coder™.

Установите HDL Coder и пакеты поддержки Embedded Coder для целевой платформы. На Панели инструментов MATLAB нажмите кнопку Home> Add-Ons> Get Add-Ons. Смотрите Получают и Управляют Дополнениями.

При выполнении IP Core Generation рабочий процесс, можно сгенерировать скрипт программного интерфейса и модель от HDL Workflow Advisor пользовательский интерфейс и в командной строке.

От пользовательского интерфейса, в Embedded System Integration> задача Generate Software Interface, устанавливают флажки Generate Software interface model и Generate Software interface script.

Если вы предназначаетесь для автономных плат FPGA, вы не можете сгенерировать модель программного интерфейса. Вместо этого можно сгенерировать скрипт программного интерфейса и протестировать ядро IP при помощи Ведущего драйвера AXI MATLAB.

В задаче Set Target Reference Design, набор Insert JTAG MATLAB as AXI Master к on. Запустите рабочий процесс к задаче Generate Software Interface.

В задаче Generate Software Interface установите флажок Generate Software interface script и запустите эту задачу.

В командной строке экспортируйте настройки HDL Workflow Advisor в скрипт, и затем используйте эти свойства с объектом Workflow Configuration. Этот скрипт задает выполнение задачи программного интерфейса путем генерации и модели и скрипта. Если вы пропускаете задачу установкой RunTaskGenerateSoftwareInterface к false, затем модель и скрипт не сгенерированы. Смотрите Конфигурируют и Рабочий процесс Генерации Ядра IP Запуска со Скриптом..

% Export Workflow Configuration Script % ... %% Load the Model load_system('hdlcoder_led_blinking'); %% Model HDL Parameters % Set Model HDL parameters % ... hdlset_param('hdlcoder_led_blinking', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_led_blinking', 'Workflow', 'IP Core Generation'); % ... % Set Workflow tasks to run hWC.RunTaskGenerateSoftwareInterface = true; hWC.GenerateSoftwareInterfaceModel = true; hWC.GenerateSoftwareInterfaceScript = true; % ... %% Run the workflow hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC);

Когда вы запускаете рабочий процесс для платформ SoC, генерируете модель программного интерфейса, чтобы протестировать базовую функциональность IP HDL. Если вам установили Embedded Coder и Simulink Coder, можно сгенерировать встроенный код из модели, и создать и запустить исполняемый файл на ядре Linux® на процессоре ARM. Когда вы предназначаетесь для автономных плат FPGA, вы не можете сгенерировать модель программного интерфейса, потому что платы не имеют встроенного процессора ARM. Вместо этого сгенерируйте скрипт программного интерфейса, чтобы протестировать ядро IP при помощи Ведущего устройства AXI MATLAB.

Модель интерфейса сгенерированного программного обеспечения заменяет алгоритм DUT в вашей исходной модели с блоками драйверов AXI на основе таблицы интерфейса Целевой платформы и настроек исходного проекта. Чтобы протестировать базовую функциональность IP HDL, симулируйте модель в режиме external mode, чтобы работать на целевом компьютере. Модели включили параллельное выполнение по умолчанию, что означает, что несколько задач выполняются одновременно процессором на борту платформы SoC.

Модель программного интерфейса имеет то же имя как ваша исходная модель с префиксным gm_ и постфиксный _interface. Сгенерированная модель от генерации HDL-кода имеет префиксный gm_. Чтобы указать, что вы используете эту модель в качестве модели программного интерфейса, можно изменить префикс в sm_.

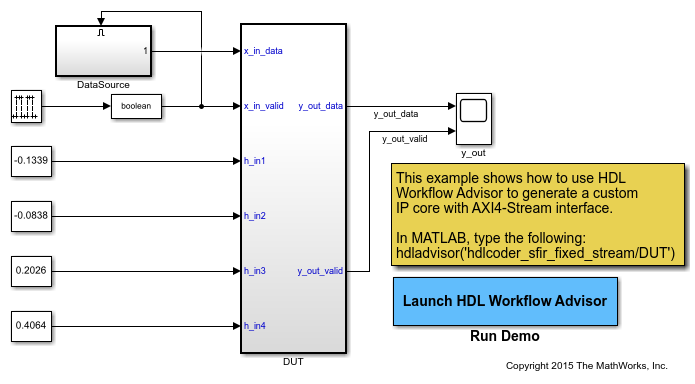

Например, откройте модель hdlcoder_sfir_fixed_stream. Эта модель сопоставляет sfir_fixed модель к упрощенному AXI4-потоковому протоколу путем вставки Valid предупредите как порт элемента управления вводом.

open_system('hdlcoder_sfir_fixed_stream')

Откройте HDL Workflow Advisor для подсистемы DUT. В задаче Set Target Device and Synthesis Tool задайте IP Core Generation как Target workflow и ZedBoard как Target platform. Нажмите Run this task.

В задаче Set Target Reference Design задайте Default system with AXI4-Stream interface как Target Reference Design. Нажмите Run this task.

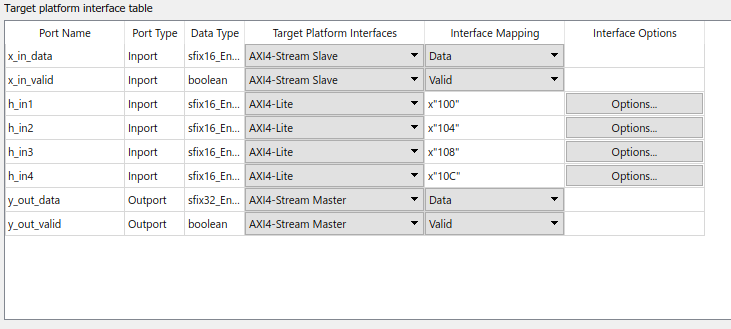

В задаче Set Target Interface сопоставьте порты DUT, чтобы предназначаться для интерфейсов в таблице интерфейса Целевой платформы. Нажмите Run this task.

Щелкните правой кнопкой по задаче Generate Software Interface и выберите Run to selected task. Запустите рабочий процесс, чтобы сгенерировать модель программного интерфейса.

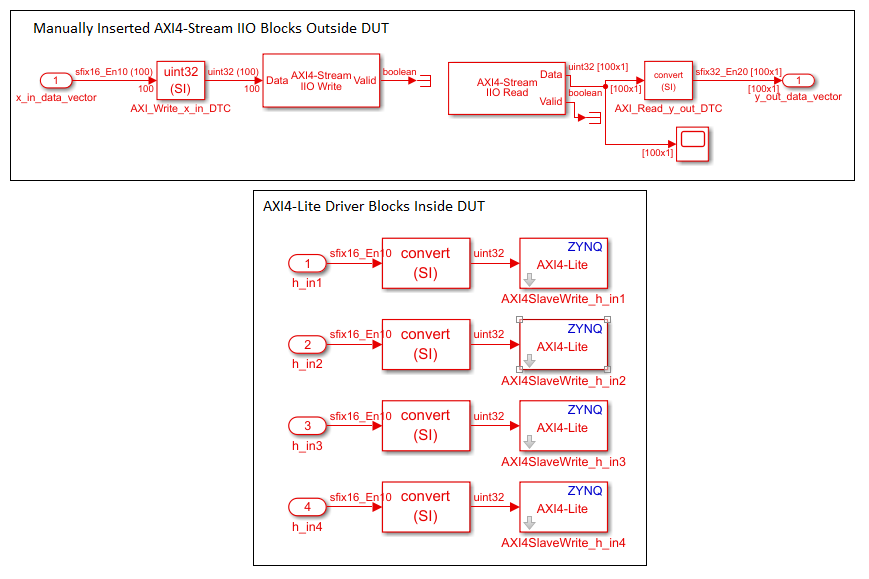

Модель интерфейса сгенерированного программного обеспечения имеет имя gm_hdlcoder_sfir_fixed_stream_interface. Когда ваша исходная модель использует скалярные порты для Data порты x_in_data и y_out_data, задача Generate software interface выводит предупреждение, что AXI4-потоковые IIO блоки драйверов автоматически не сгенерированы в модели программного интерфейса. Можно или вставить блоки драйверов от Библиотеки Пакета Поддержки Embedded Coder для целевой платформы в Браузере Библиотеки Simulink или повторно выполнить рабочий процесс путем отображения Data порты к векторным сигналам. Видеть модель программного интерфейса, которой вставили AXI4-потоковые IIO блоки драйверов в него, открытый hdlcoder_sfir_fixed_stream_sw. Модель использует AXI4-Stream IIO Write (Пакет Поддержки Embedded Coder для Платформы Xilinx Zynq) и AXI4-Stream IIO Read (Пакет Поддержки Embedded Coder для Платформы Xilinx Zynq) блоки для Data порты. Порты фильтра сопоставлены с AXI4-Lite блоки драйверов.

open_system('hdlcoder_sfir_fixed_stream_sw')

Сконфигурируйте модель со временем остановки inf. На вкладке Hardware вы видите аппаратные настройки, заданные на модели. Можно затем соединиться, и создать и запустить приложение на целевой платформе, чтобы проверить базовую функциональность IP HDL. Для примера смотрите Начало работы с AXI4-потоковым Интерфейсом в Рабочем процессе Zynq.

Для быстрого прототипирования и тестирования базовой функциональности IP HDL, используйте скрипт программного интерфейса. Скрипт не требует лицензии Embedded Coder. Скриптом является файл MATLAB, который сгенерирован на основе исходного проекта и табличных настроек интерфейса Целевой платформы. Это содержит команды, которые позволяют вам соединиться с целевым компьютером, и записать в или читать из сгенерированного ядра IP из MATLAB. Для автономных плат FPGA используйте скрипт интерфейса сгенерированного программного обеспечения, чтобы проверить базовую функциональность IP HDL при помощи Ведущего устройства AXI MATLAB.

Скрипт программного интерфейса имеет то же имя как ваша исходная модель с префиксным gs_ и постфиксный _interface. Скрипт инстанцирует функции настройки, которая сгенерирована, когда вы включаете генерацию скрипта программного интерфейса. Например, этот код показывает функцию настройки, сгенерированную для модели hdlcoder_sfir_fixed_stream с исходным проектом и Целевой платформой соединяют интерфейсом с табличными настройками, заданными выше. Функция настройки содержит команды для ведомого устройства AXI4 и AXI4-потоковых интерфейсов, что использование HDL Coder, чтобы управлять портами DUT в сгенерированном ядре IP HDL, которые сопоставлены с соответствующими интерфейсами.

function gs_hdlcoder_sfir_fixed_stream_setup(hFPGA) %-------------------------------------------------------------------------- % Software Interface Script Setup % % Generated with MATLAB 9.10 (R2021a) at 09:13:05 on 10/07/2020. % This function was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Run this function on an "fpga" object to configure it with % the same interfaces as the generated IP core. %-------------------------------------------------------------------------- %% AXI4-Lite addAXI4SlaveInterface(hFPGA, ... "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xA0000000, ... "AddressRange", 0x10000); hPort_h_in1 = hdlcoder.DUTPort("h_in1", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x100"); hPort_h_in2 = hdlcoder.DUTPort("h_in2", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x104"); hPort_h_in3 = hdlcoder.DUTPort("h_in3", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x108"); hPort_h_in4 = hdlcoder.DUTPort("h_in4", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x10C"); mapPort(hFPGA, [hPort_h_in1, hPort_h_in2, hPort_h_in3, hPort_h_in4]); %% AXI4-Stream addAXI4StreamInterface(hFPGA, ... "InterfaceID", "AXI4-Stream", ... "WriteEnable", true, ... "WriteFrameLength", 1024, ... "ReadEnable", true, ... "ReadFrameLength", 1024); hPort_x_in_data = hdlcoder.DUTPort("x_in_data", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); hPort_y_out_data = hdlcoder.DUTPort("y_out_data", ... "Direction", "OUT", ... "DataType", numerictype(1,32,20), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); mapPort(hFPGA, [hPort_x_in_data, hPort_y_out_data]); end

Скрипт программного интерфейса инстанцирует этой функции настройки, чтобы соединиться с целью и отправить команды записи или чтение. Можно не прокомментировать и отправить значимые данные при помощи входных параметров к DUT в исходной модели. После взаимодействия через интерфейс с оборудованием скрипт отключается от аппаратного ресурса, сопоставленного с fpga объект.

%-------------------------------------------------------------------------- % Software Interface Script % % Generated with MATLAB 9.10 (R2020b) at 09:13:10 on 10/07/2020. % This script was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Use this script to access DUT ports in the design mapped to compatible IP core interfaces. % You can write to input ports in the design and read from output ports directly from MATLAB. % % To write to input ports, use the "writePort" command and specify port name and input data. % The input data will be cast to the DUT port's data type before writing. % % To read from output ports, use the "readPort" command and specify the port name. % The output data will be returned with the same data type as the DUT port. % % Use the "release" command to release MATLAB's control of the hardware resources. %-------------------------------------------------------------------------- %% Create fpga object hFPGA = fpga("Xilinx"); %% Setup fpga object % This function configures "fpga" object with same interfaces as the generated IP core gs_hdlcoder_sfir_fixed_stream_setup(hFPGA); %% Write/read DUT ports % Uncomment the following lines to write/read DUT ports in the generated IP Core. % Update the example data in the write commands with meaningful data to write to the DUT. %% AXI4-Lite writePort(hFPGA, "h_in1", zeros([1 1])); writePort(hFPGA, "h_in2", zeros([1 1])); writePort(hFPGA, "h_in3", zeros([1 1])); writePort(hFPGA, "h_in4", zeros([1 1])); %% AXI4-Stream writePort(hFPGA, "x_in_data", zeros([1 1024])); data_y_out_data = readPort(hFPGA, "y_out_data"); %% Release hardware resources release(hFPGA)