Нативная поддержка с плавающей точкой в HDL Coder™ позволяет вам сгенерировать код из своего проекта с плавающей точкой. Если ваш проект имеет комплексную математику и тригонометрические операции или имеет данные с большим динамическим диапазоном, используйте собственный компонент, с плавающей точкой.

В вашей модели Simulink®:

У вас могут быть полуточность, и типы данных с плавающей точкой с двойной точностью с одинарной точностью и операции.

У вас может быть комбинация целого числа, фиксированной точки и операций с плавающей точкой. При помощи блоков Data Type Conversion можно выполнить преобразования между с плавающей точкой и типами данных с фиксированной точкой.

Сгенерированный код:

Выполняет стандарт IEEE 754 арифметики с плавающей точкой.

Независимо от цели. Можно развернуть код по любому типовому FPGA или ASIC.

Не требует блоков обработки с плавающей точкой или трудно блоков DSP с плавающей точкой на целевом ASIC или FPGA.

Поддержки HDL Coder:

Математические и тригонометрические функции

Большое подмножество блоков Simulink

Нестандартные числа

Настройка задержки оператора с плавающей точкой

Нативная технология с плавающей точкой в HDL Coder придерживается стандарта IEEE арифметики с плавающей точкой. Для основных арифметических операций, таких как сложение, вычитание, умножение, деление и обратная величина, когда вы генерируете HDL-код в нативном режиме с плавающей точкой, числовые результаты получили, совпадают с исходной моделью Simulink.

Определенные операции высшей математики, такие как экспоненциал, логарифм и тригонометрические операторы имеют специфичные для машины поведения реализации потому что эти операторы повторение использования Taylor series и Remez основанные на выражении реализации. Когда вы используете эти операторы в нативном режиме с плавающей точкой, сгенерированный HDL-код может иметь относительно небольшие числовые различия от модели Simulink. Эти числовые различия в допустимом диапазоне и поэтому указывают на податливость со стандартом IEEE 754.

Чтобы сгенерировать код, который выполняет стандарт IEEE 754, поддержки HDL Coder:

Вокруг к самому близкому режиму округления

Нестандартные числа

Исключения, такие как NaN (Не Номер), Inf и Нуль

Индивидуальная настройка ULP (Модули в Последнем Месте) и относительная точность

Для получения дополнительной информации смотрите Числовые Факторы с Собственным компонентом, С плавающей точкой.

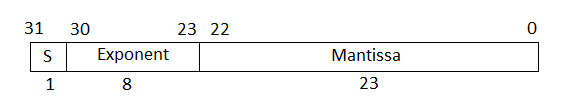

В стандарте IEEE 754-2008 число с плавающей запятой с одинарной точностью составляет 32 бита. 32-битный номер кодирует 1-битный знак, 8-битную экспоненту и 23-битную мантиссу.

Этот график является нормированным представлением для чисел с плавающей запятой. Можно вычислить фактическое значение нормального номера как:

Поле экспоненты представляет экспоненту плюс смещение 127. Размер мантиссы составляет 24 бита. Ведущий бит является 1, таким образом, представление кодирует более низкие 23 бита.

Используйте типы с одинарной точностью для приложений, которые требуют большего динамического диапазона, чем типы полуточности. Операции с одинарной точностью используют меньше памяти, и имеет более низкую задержку, чем типы с двойной точностью.

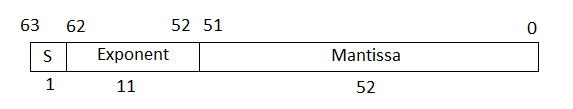

В стандарте IEEE 754-2008 число с плавающей запятой с одинарной точностью составляет 64 бита. 64-битный номер кодирует 1-битный знак, 11-битную экспоненту и 52-битную мантиссу.

Поле экспоненты представляет экспоненту плюс смещение 1 023. Размер мантиссы составляет 53 бита. Ведущий бит является 1, таким образом, представление кодирует более низкие 52 бита.

Использование с двойной точностью вводит для приложений, которые требуют большего динамического диапазона, точности и точности. Эти операции используют большую область на FPGA и более низкую целевую частоту.

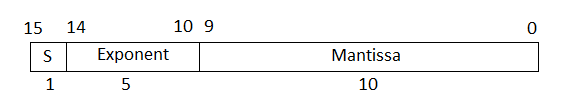

В стандарте IEEE 754-2008 число с плавающей запятой полуточности составляет 16 битов. 16-битный номер кодирует 1-битный знак, 5-битную экспоненту и 10-битную мантиссу.

Поле экспоненты представляет экспоненту плюс смещение 15. Размер мантиссы составляет 11 битов. Ведущий бит является 1, таким образом, представление кодирует более низкие 10 битов.

Используйте типы полуточности для приложений, которые требуют меньшего динамического диапазона, использует намного меньше памяти, имеет более низкую задержку и сохраняет ресурсы FPGA.

При использовании half типы, вы можете хотеть явным образом установить Output data type блоков к half вместо настройки по умолчанию Inherit: Inherit via internal rule. Чтобы изучить, как изменить параметры программно, смотрите Параметры блоков HDL Набора для Нескольких Блоков Программно.

С нативной поддержкой с плавающей точкой HDL Coder поддерживает генерацию кода из моделей Simulink, которые содержат сигналы с плавающей точкой и сигналы фиксированной точки. Вы можете хотеть смоделировать свой проект с типами с плавающей точкой к:

Реализуйте алгоритмы, которые имеют большой или неизвестный динамический диапазон, который может выйти за пределы области значений представимых фиксированных точек.

Реализуйте комплексную математику и тригонометрические операции, которые затрудняют, чтобы спроектировать в фиксированной точке.

Получите более высокую точность и лучшую точность.

Проекты с плавающей точкой могут потенциально занять больше области на целевом компьютере. В вашей модели Simulink рекомендуется использовать типы данных с плавающей точкой в информационном канале алгоритма и типы данных с фиксированной точкой в управляющей логике алгоритма. Этот рисунок показывает раздел модели Simulink, которая использует Single и фиксированные точки. При помощи блоков Data Type Conversion можно выполнить преобразования между синглом и фиксированными точками.