Развертывание алгоритмических моделей к оборудованию FPGA позволяет сделать беспроводное тестирование и верификацию. Однако разработка систем радиосвязей для оборудования требует компромиссов проекта между аппаратными ресурсами и пропускной способностью. Можно ускорить аппаратный проект и развертывание при помощи оптимизированных HDL блоков, которые имеют подходящие для оборудования интерфейсы и архитектуры, примеры готовых узлов, которые реализуют фрагменты LTE и 5G физический уровень NR и автоматическая генерация HDL-кода. Можно также использовать пакеты аппаратной поддержки, чтобы помочь с развертыванием и проверкой проекта на действительном оборудовании.

Продукты MathWorks® HDL, такие как Wireless HDL Toolbox™, позволяют вам запускаться с математической модели, такой как код MATLAB® от LTE Toolbox™ или 5G Toolbox™, и проектировать аппаратную реализацию того алгоритма, который подходит для FPGAs и ASICs.

Проект радиосвязей часто запускается с разработки алгоритмов и тестирующий использование функций MATLAB. Код MATLAB, который обычно работает с матрицами данных с плавающей точкой, хорош для разработки математических алгоритмов, управления большими наборами данных и визуализации данных.

Инженеры аппаратного обеспечения обычно получают математическую спецификацию от команды алгоритма и повторно реализуют алгоритм для оборудования. Аппаратные проекты требуют компромиссов использования ресурсов для тактовой частоты и полной пропускной способности. Обычно это компромисс означает работать с потоковой передачей данных и использованием некоторой логики, чтобы управлять устройством хранения данных и потоком данных. Инженеры аппаратного обеспечения обычно работают на языках описания аппаратных средств (HDLs), как VHDL и Verilog, которые обеспечивают основанное на цикле моделирование и параллелизм.

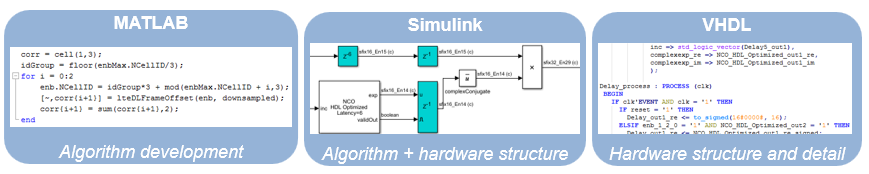

Чтобы устранить этот разрыв между математическим алгоритмом и аппаратной реализацией, используйте модель алгоритма MATLAB в качестве начальной точки для аппаратной реализации. Внесите инкрементные изменения в проект, чтобы сделать его подходящим для оборудования и прогресса к модели Simulink®, которую можно использовать, чтобы автоматически сгенерировать HDL-код при помощи HDL Coder™.

Эта схема показывает прогрессию проекта от математического алгоритма в MATLAB к аппаратно-совместимой реализации в Simulink, и затем сгенерированному коду VHDL.

В то время как и MATLAB и Simulink поддерживают автоматическую генерацию HDL-кода, необходимо создать проект с требованиями к аппаратным средствам в памяти, и Simulink в лучшем костюме для основанного на цикле моделирования для оборудования. Это может представлять параллельные информационные каналы и данные о потоковой передаче с управляющими сигналами справиться с синхронизацией потока данных. Чтобы помочь в выборе фиксированной точки, это ясно визуализирует распространение типа данных в проекте. Это также позволяет, чтобы легкая конвейеризация математических операций улучшила максимальную тактовую частоту в оборудовании.

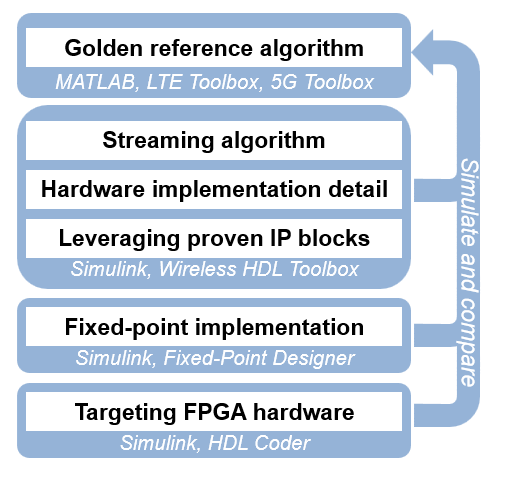

В то время как вы создаете свой готовый к оборудованию проект, используйте алгоритм MATLAB в качестве "золотой ссылки", чтобы проверить, что каждая версия проекта все еще удовлетворяет математические требования. Рабочий процесс, показанный в схеме, использует MATLAB и Simulink как сотрудничество и коммуникационные инструменты между аппаратными командами проектировщиков и алгоритмом.

Например, при разработке для LTE или беспроводных стандартов 5G, можно использовать LTE Toolbox и функции 5G Toolbox, чтобы создать золотую ссылку в MATLAB. Затем переход к Simulink и создает аппаратно-совместимую реализацию при помощи библиотечных блоков от Wireless HDL Toolbox и блоков из Communications Toolbox™ и DSP System Toolbox™ та генерация HDL-кода поддержки. Можно снова использовать тест и инфраструктуру генерации данных из MATLAB путем импортирования данных от MATLAB до модели Simulink и возвращения выходного параметра модели к MATLAB, чтобы проверить его по "золотой ссылке".

Библиотечные блоки от Wireless HDL Toolbox реализуют энкодеры, декодеры, модуляторы, демодуляторы и генераторы последовательности для использования в LTE, 5G или общей системе радиосвязей. Эти блоки используют стандартный интерфейс данных о потоковой передаче для оборудования. Этот интерфейс дает возможность соединять части алгоритма вместе и включает управляющие сигналы, которые управляют потоком данных и отмечают контуры системы координат. Эти блоки поддерживают автоматическую генерацию HDL-кода с HDL Coder. Можно также использовать блоки из Communications Toolbox и DSP System Toolbox та генерация HDL-кода поддержки.

Блоки обеспечивают подходящие для оборудования архитектуры, которые оптимизируют использование ресурса, такой как включая сумматор и конвейеризацию множителя, чтобы соответствовать хорошо срезам DSP FPGA. Они также поддерживают автоматические и конфигурируемые типы данных с фиксированной точкой. Используя предопределенные блоки также позволяет вам пробовать различные настройки параметра, не изменяя остальную часть проекта.

Для списков блоков, которые поддерживают генерацию HDL-кода, см. Черный список Wireless HDL Toolbox (генерация HDL-кода) (Wireless HDL Toolbox), Черный список Communications Toolbox (генерация HDL-кода) (Communications Toolbox) и Черный список DSP System Toolbox (генерация HDL-кода) (DSP System Toolbox).

Wireless HDL Toolbox предоставляет примеры готовых узлов, которые содержат готовые к оборудованию реализации значительных частей LTE и 5G физический уровень NR. Эти проекты проверяются по "золотым ссылочным" функциям, обеспеченным LTE Toolbox и 5G Toolbox. Они были также протестированы на платах FPGA, чтобы подтвердить, что они кодируют и декодируют беспроводные формы волны и используют разумную сумму аппаратных ресурсов. Они спроектированы, чтобы быть модульными, масштабируемыми, и расширяемыми, таким образом, можно вставить дополнительные физические каналы. Проект приемника был протестирован с помощью полученного не воздуха форм волны.

Набор примеров готовых узлов включает:

LTE и 5G NR первичный и вторичный сигнал синхронизации (PSS/SSS) генерация и обнаружение

Детектор канала совместного управления нисходящего канала LTE и генерация основного блока информации (MIB) и восстановление

LTE первый системный блок информации (SIB1) декодер

Модели аппаратного программного интерфейса для MIB и битного парсинга SIB1 и индексации данных об оценке канала

Генерация сигналов LTE для передачи нескольких-антенн

Поддержка FDD и TDD для приложений передатчика и приемника LTE

Эти примеры готовых узлов могут быть использованы как есть, чтобы обеспечить информацию о пакете вашему уникальному приложению и сгенерировать синтезируемый VHDL или Verilog с HDL Coder. Они также служат примерами, чтобы проиллюстрировать методические рекомендации для реализации коммуникационных алгоритмов на оборудовании ASIC или FPGA.

Wireless HDL Toolbox предоставляет блокам ту генерацию HDL-кода поддержки. Чтобы сгенерировать HDL-код из проектов, которые используют эти блоки, у вас должна быть лицензия HDL Coder. HDL Coder производит независящий от устройств код с именами сигнала, которые соответствуют модели Simulink. HDL Coder также обеспечивает инструмент, чтобы управлять процессом синтеза и предназначения FPGA и позволяет вам сгенерировать скрипты и испытательные стенды для использования со сторонними симуляторами HDL.

Чтобы помочь с настройкой и предназначением программируемой логики на прототипной плате, и проверить вашу разработку системы радиосвязей на оборудовании, загружают пакет аппаратной поддержки, такой как Пакет Поддержки Communications Toolbox для Радио Xilinx® Zynq®-Based.