Можно оптимизировать тактовую частоту, используемую кодом фильтра путем применения конвейерных регистров. Несмотря на то, что регистры увеличивают полную задержку фильтра и использованное пространство, они предоставляют существенные улучшения тактовой частоте. Эти регистры отключены по умолчанию. Когда вы включаете им, кодер добавляет регистры между этапами расчета в фильтре.

| Для... | Конвейерно обработайте регистры, добавляются |

|---|---|

| КИХ, антисимметричный КИХ и симметричные КИХ-фильтры | Между уровнями итогового дерева суммирования |

| Транспонированные КИХ-фильтры | Между содействующими множителями и сумматорами |

| БИХ-фильтры | Между разделами |

| CIC | Между разделами расчески |

Например, для шестого БИХ-фильтра порядка, кодер добавляет два конвейерных регистра. Кодер вставляет конвейерный регистр между первым и вторым разделом, и между вторым и третьим разделом.

Для КИХ-фильтров использование конвейерных регистров оптимизирует суммирование финала фильтра. Для получения дополнительной информации смотрите Оптимизирующее Итоговое Суммирование для КИХ-Фильтров.

Примечание

Конвейерно обработайте регистры в КИХ, антисимметричном КИХ, и симметричные КИХ-фильтры могут привести к числовым результатам, которые отличаются от результатов, приведенных исходным объектом фильтра, потому что они обеспечивают древовидный режим итогового суммирования.

Использовать конвейерные регистры,

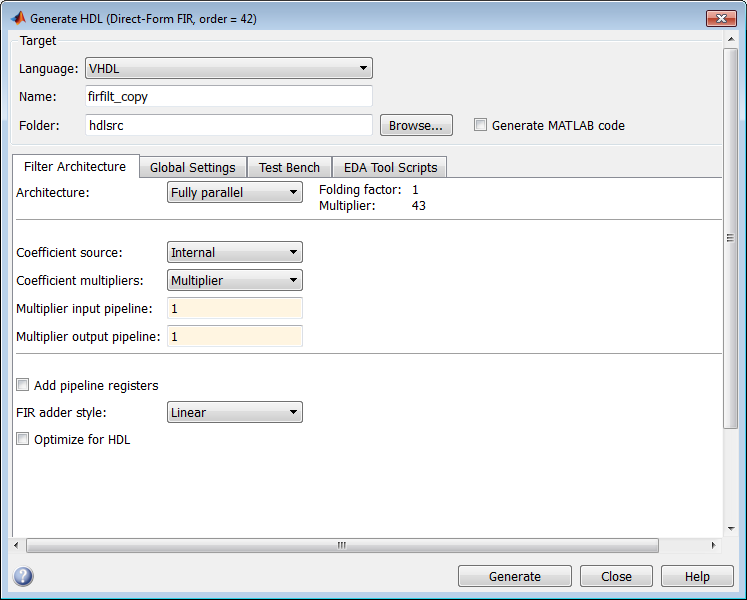

Выберите опцию Add pipeline registers в панели Filter architecture диалогового окна Generate HDL.

Для КИХ антисимметричный КИХ и симметричные КИХ-фильтры, рассматривают установку допуска на погрешность для сгенерированного испытательного стенда с учетом числовых различий. Допуск на погрешность является количеством младших значащих битов, которые испытательный стенд игнорирует при сравнении результатов. Установить допуск на погрешность:

Выберите панель Test Bench в диалоговом окне Generate HDL. Затем кликните по вкладке Configuration.

Установите поле Error margin (bits) на целое число, которое указывает на максимальное приемлемое количество битов различия в числовых результатах.

Продолжите устанавливать другие опции или нажмите Generate, чтобы инициировать генерацию кода.

Альтернатива командной строки: используйте generatehdl функция со свойством AddPipelineRegisters оптимизировать фильтры с конвейерными регистрами.

Если вы сохраняете операции множителя для КИХ-фильтра, можно достигнуть более высоких тактовых частот путем добавления настроек канала связи при вводах или выводах множителя.

Следующая фигура показывает варианты пользовательского интерфейса для опций конвейеризации множителя. Включить эти опции, Coefficient multipliers к Multiplier.

Multiplier input pipeline: Чтобы добавить настройки канала связи перед каждым множителем, введите желаемый номер этапов как целое число, больше, чем или равный 0.

Multiplier output pipeline: Чтобы добавить настройки канала связи после каждого множителя, введите желаемый номер этапов как целое число, больше, чем или равный 0.

Альтернатива командной строки: используйте generatehdl функция с MultiplierInputPipeline и MultiplierOutputPipeline свойства задать конвейеризацию множителя для КИХ-фильтров.

Если вы генерируете HDL-код для КИХ-фильтра, полагаете, что оптимизация итогового метода суммирования применяется к фильтру. По умолчанию кодер применяет линейное суммирование сумматора, которое является итоговым методом суммирования, обсужденным в большинстве учебников DSP. В качестве альтернативы можно дать кодеру команду применять дерево или конвейерно обрабатывать итоговое суммирование. Когда установлено в древовидный режим, кодер создает итоговый сумматор, который выполняет попарное сложение на последовательных продуктах, которые выполняются параллельно, а не последовательно. Конвейерный режим приводит к результатам, похожим на древовидный режим со сложением этапа конвейерных регистров после обработки каждого уровня дерева.

В сравнении,

Количество работы сумматора для линейного и древовидного режима является тем же самым. Синхронизация для древовидного режима может быть лучше должна быть параллельной сложениям.

Конвейерно обработайте режим, оптимизирует тактовую частоту, но увеличивает задержку фильтра. Задержка увеличивается log2(number of products), окруженный до ближайшего целого числа.

Линейный режим помогает достигнуть числовой точности по сравнению с исходным объектом фильтра. Дерево и конвейерные режимы могут привести к числовым результатам, которые отличаются от результатов, приведенных объектом фильтра.

Изменить итоговое суммирование, которое будет применено к КИХ-фильтру:

Выберите одну из этих опций в панели Filter architecture диалогового окна Generate HDL.

| Для... | Выбрать... |

|---|---|

| Линейный режим (значение по умолчанию) | Linear в меню FIR adder style |

| Древовидный режим | Tree в меню FIR adder style |

| Режим Pipeline | Флажок Add pipeline registers |

Если вы задаете дерево или конвейерный режим, рассматриваете установку допуска на погрешность для сгенерированного испытательного стенда с учетом числовых различий. Допуск на погрешность является количеством младших значащих битов, которые испытательный стенд игнорирует при сравнении результатов. Установить допуск на погрешность,

Выберите панель Test Bench в диалоговом окне Generate HDL. Затем кликните по вкладке Configuration.

Установите поле Error margin (bits) на целое число, которое указывает на максимальное приемлемое количество битов различия в числовых результатах.

Продолжите устанавливать другие опции или нажмите Generate, чтобы инициировать генерацию кода.

Альтернатива командной строки: используйте generatehdl функция со свойством FIRAdderStyle или AddPipelineRegisters оптимизировать итоговое суммирование для КИХ-фильтров.

Кодер добавляет дополнительный входной регистр (input_register) и дополнительный выходной регистр (output_register) во время генерации HDL-кода. Эти дополнительные регистры могут быть полезны для синхронизации целей, но они добавляют к полной задержке.

Следующий блок процесса пишет в дополнительный входной регистр input_register когда событие часов имеет место и clk активен высокий (1):

Input_Register_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

input_register <= (OTHERS => '0');

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

input_register <= input_typeconvert;

END IF;

END IF;

END PROCESS Input_Register_Process ;

Следующий блок процесса пишет в дополнительный выходной регистр output_register когда событие часов имеет место и clk активен высокий (1):

Output_Register_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

output_register <= (OTHERS => '0');

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

output_register <= output_typeconvert;

END IF;

END IF;

END PROCESS Output_Register_Process;

Если полная задержка является беспокойством о вашем приложении, и у вас нет требований синхронизации, можно подавить генерацию дополнительных регистров можно следующим образом:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку Ports в панели Additional settings.

Очистите Add input register и Add output register как требуется. Следующий рисунок показывает установку для подавления генерации дополнительного входного регистра.

Альтернатива командной строки: используйте generatehdl и функция со свойствами AddInputRegister andAddOutputRegister добавить дополнительный регистр ввода или вывода.