Если у вас есть лицензия Simulink® Coder™, можно сгенерировать испытательный стенд Универсальной методологии верификации (UVM) и дополнительные компоненты из модели Simulink. Генерация компоненты UVM включает прямой переход от вашего окружения Simulink до среды UVM.

HDL Verifier™ экспортирует Подсистемы Simulink как сгенерированный код C в компонентах UVM с интерфейсом программирования на машинном языке (DPI). Можно интегрировать эти сгенерированные компоненты в существующую среду UVM. Можно также использовать сгенерированный испытательный стенд UVM, чтобы протестировать HDL DUT, заменяя сгенерированный поведенческий DUT на подробный проект HDL.

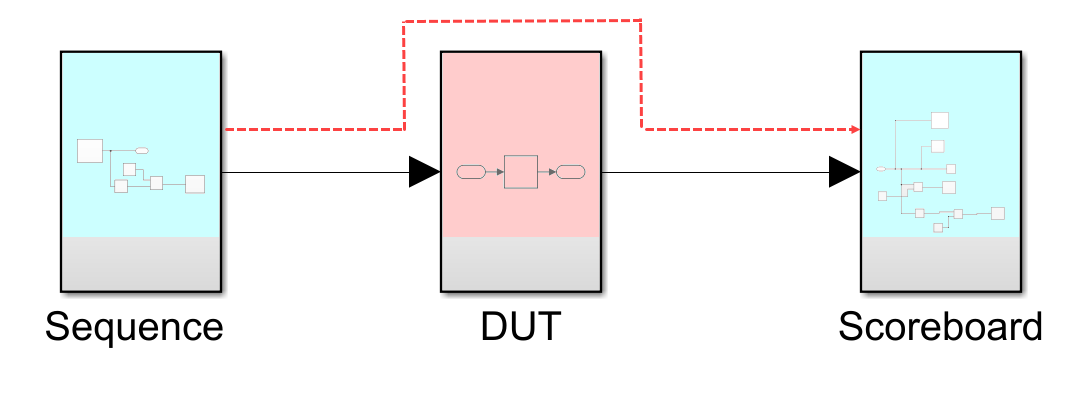

Ваша модель Simulink должна включать эти подсистемы.

Подсистема DUT. Эта подсистема генерирует SystemVerilog DPI (SVDPI) поведенческая модель вашего DUT. Для получения дополнительной информации о генерации SystemVerilog DPI, смотрите Генерацию Компонента DPI с Simulink.

Подсистема последовательности. Эта подсистема создает стимул и управляет им к DUT.

Подсистема табло. Эта подсистема собирает и проверяет выход DUT.

Последовательность может также управлять сигналами непосредственно к табло, как проиллюстрировано в красном на рисунке Структуры модели Simulink.

Для получения дополнительной информации о том, как создать подсистему, смотрите, Создают Подсистемы (Simulink).

Структура модели Simulink

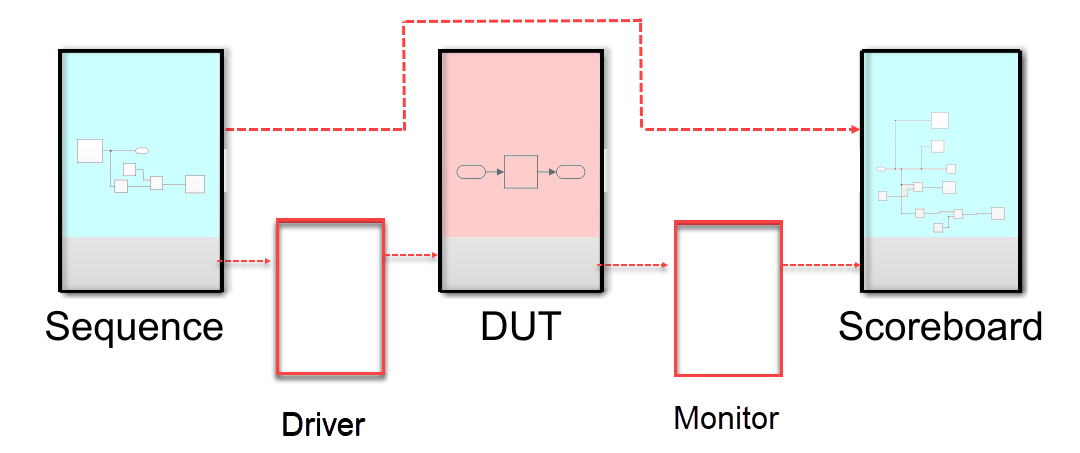

В дополнение к предыдущей структуре можно опционально включать эти подсистемы.

Подсистема драйвера

Подсистема монитора

При добавлении монитора или подсистемы драйвера, эта функция поддерживает эти настройки.

Если ваша модель включает подсистему драйвера, то все сигналы, выходящие из последовательности, должны быть соединены с драйвером или табло.

Если ваша модель включает подсистему драйвера, то все сигналы, выходящие из драйвера, должны быть соединены с DUT.

Если ваша модель включает подсистему монитора, то все сигналы, выходящие из DUT, должны быть соединены с монитором.

Если ваша модель включает подсистему монитора, то все сигналы, выходящие из монитора, должны быть соединены с табло.

Это изображение показывает модель Simulink, которая включает подсистему драйвера и подсистему монитора.

Поскольку генерация UVM использует технологию для генерации SystemVerilog DPI, необходимо сначала выбрать системный конечный файл поддержки. Откройте диалоговое окно параметров конфигурации и выберите Code Generation из левой панели. Для Системного конечного файла нажмите Browse, и затем выберите systemverilog_dpi_grt.tlc из списка.

В качестве альтернативы, если у вас есть продукт Embedded Coder®, можно выбрать целевой systemverilog_dpi_ert.tlc. Эта цель позволяет опциям генерации дополнительного кода доступа, когда вы выбираете Code Generation из левой панели диалогового окна Configuration Parameters.

Для примера генерации UVM смотрите, Генерируют Параметрированный Испытательный стенд UVM от Simulink.

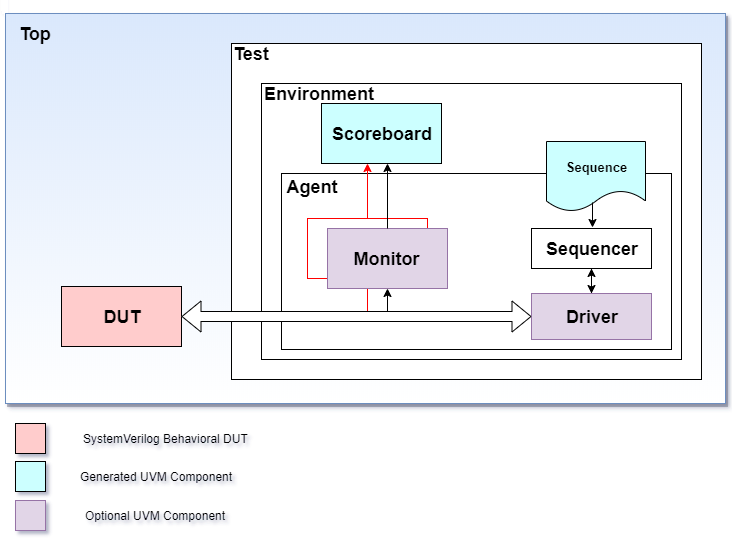

Используйте uvmbuild функция, чтобы сгенерировать эту структуру компонентов UVM.

Верхняя часть – Этот модуль инстанцирует сгенерированного поведенческого DUT и тестовой среды. Главный модуль имеет часы и сигналы сброса, которые распространяют в проект.

DUT – поведенческий модуль проекта под тестом сгенерирован от вашей подсистемы DUT Simulink.

Тест – Этот модуль включает среду UVM и класс последовательности.

Объект Sequence - This UVM задает набор транзакций. Объект последовательности сгенерирован от вашей подсистемы последовательности Simulink.

Среда – Этот модуль включает агента и сгенерированное табло.

Табло – табло UVM сгенерировано от вашей подсистемы табло Simulink.

Агент – агент UVM включает секвенсер, драйвер и монитор. Если прямой путь существует от подсистемы последовательности Simulink до подсистемы табло Simulink, дополнительный монитор, проиллюстрированный в красном на рисунке, включен, чтобы контролировать тот сигнал.

Секвенсер – Этот модуль управляет потоком транзакций последовательности к DUT.

Драйвер – Этот модуль сгенерирован от вашей подсистемы драйвера Simulink и преобразовывает каждую транзакцию от Последовательности до сигналов, что поведенческий DUT понимает.

Монитор – Этот модуль сгенерирован от вашей подсистемы монитора Simulink, и это производит сигналы от поведенческого DUT и генерирует транзакции, которые отправляются в табло UVM.

Для получения дополнительной информации о компонентах UVM и структуре, см. справочник UVM.

При генерации компонентов UVM HDL Verifier генерирует компоненты SystemVerilog DPI от DUT, последовательности и подсистем табло. Артефакты генерации DPI помещаются в три директории, один для каждой подсистемы: DUT, последовательность и табло. Для каждой из этих трех подсистем папка создается с этим содержимым.

subsystem_buildsubsystem_build

subsystem_dpi_pkg.sv

subsystem_dpi.sv

DPI и заголовочные файлы компонента с расширениями.c и.h

Метаданные и информационные файлы с расширениями .mat, .txt, .dmr, .tmw, и .def

Make-файл для компиляции компонентов в.o и .so файлы

После генерации трех папок для заданных подсистем четвертая папка создается для дополнительных файлов компонента UVM и скриптов выполнения. Папку называют top-model-name_uvmbuild/uvm_testbenchtop-model-name имя вашей главной модели Simulink. Эта папка включает несколько подпапок.

DPI_dut – Эта папка содержит копию пакета SystemVerilog, файлов модуля и .dll файла от dut_build

scoreboard – Эта папка содержит копию пакета SystemVerilog и .dll файла от scoreboard_build

sequence – Эта папка содержит копию пакета SystemVerilog и .dll файла от sequence_build

top – Эта папка содержит пакет SystemVerilog и файлы модуля для главной модели Simulink. Эта папка также содержит скрипты для выполнения симулятора HDL.

uvm_artifacts – Эта папка содержит эти файлы SystemVerilog.

mw_dpi_types_pkg.sv – Этот файл содержит определения сгенерированных типов SystemVerilog, такие как enum и struct, отсоединенный интерфейсами компонента UVM. Только компоненты UVM, которые используют эти типы, импортируют этот пакет.

mw_ – Этот файл содержит объект UVM, который задает тип входной транзакции для табло.DUT_trans.sv

mw_ – Этот файл задает тип интерфейса DUT SystemVerilog. Это содержит вводы и выводы DUT, а также порты для часов, сброса, и часы - включают сигналы.DUT_if.sv

mw_ – Этот файл включает передачу драйвер UVM по умолчанию. При определении подсистемы драйвера к DUT_driver.svuvmbuild функция, этот модуль включает планировщик и вызовы API компонента DPI Driver_dpi_pkg.sv

mw_ – Этот файл включает передачу монитор UVM. Выборки монитора сигнализируют с драйвера на табло.DUT_monitor_input.sv

mw_ – Этот файл включает передачу монитор UVM. Выборки монитора сигнализируют с DUT на табло. При определении подсистемы монитора к DUT_monitor.svuvmbuild функция, этот модуль включает планировщик и вызовы API Monitor_dpi_pkg.sv

mw_ – Этот файл включает агента UVM, который инстанцирует последовательности, драйвера и монитора.DUT_agent.sv

mw_ – Этот файл включает среду UVM, которая инстанцирует агента и табло.DUT_environment.sv

mw_ – Этот файл включает тест UVM, который инстанцирует среды и последовательности. Тестовый модуль запускает транзакции путем вызова DUT_test.svseq.start.

При определении монитора или драйвера к uvmbuild функция, две дополнительных директории сгенерированы в uvm_testbench директория.

driver – Эта папка сгенерирована, если вы задали подсистему монитора к uvmbuild функция. Эта папка содержит копию пакета SystemVerilog и совместно использованного файла библиотеки (dll-файл или таким-образом-файл) от driver_build

monitor – Эта папка сгенерирована, если вы задали подсистему монитора к uvmbuild функция. Эта папка содержит копию пакета SystemVerilog и совместно использованного файла библиотеки (dll-файл или таким-образом-файл) от monitor_build

Поддерживаемые типы данных Simulink преобразованы в типы данных SystemVerilog, как показано в этой таблице.

Сгенерированные типы SystemVerilog

| MATLAB® | SystemVerilog | ||

|---|---|---|---|

| Совместимый тип C | Логический вектор | Битовый вектор | |

uint8 | byte unsigned | logic [7:0] | bit [7:0] |

uint16 | shortint unsigned | logic [15:0] | bit [15:0] |

uint32 | int unsigned | logic [31:0] | bit [31:0] |

uint64 | longint unsigned | logic [63:0] | bit [63:0] |

int8 | byte | logic signed [7:0] | bit signed [7:0] |

int16 | shortint | logic signed [15:0] | bit signed [15:0] |

int32 | int | logic signed [31:0] | bit signed [31:0] |

int64 | longint | logic signed [63:0] | bit signed [63:0] |

boolean | byte unsigned | logic [0:0] | bit [0:0] |

| фиксированная точка | Порт является знаком, расширенным к встроенному типу C, такому как |

Логическая длина вектора ( |

Длина битового вектора ( |

single | shortreal | ||

double | real | ||

complex | Можно выбрать между SystemVerilog | ||

| векторы, матрицы | массивы Например, 4 2 матрица в Simulink преобразована в одномерный массив восьми элементов в SystemVerilog. Кодер сглаживает матрицы в порядке развертывания по столбцам. | ||

| невиртуальная шина | Можно выбрать между SystemVerilog | ||

| перечислимые типы данных | enum | ||

HDL Verifier преобразует матрицы и векторы к одномерным массивам в SystemVerilog. Например, 4 2 матрица в Simulink преобразована в одномерный массив восьми элементов в SystemVerilog.

uvmbuild функция игнорирует компоненты Simulink, которые не заданы как DUT, последовательность, табло, драйвер или подсистемы монитора.

Можно использовать обратную связь в любой из подсистем, но не между ними.

Последовательность и подсистемы табло должны действовать на одном уровне, и основные шаги расчета их подсистем должны быть равными. Для получения дополнительной информации о шагах расчета, смотрите Шаги расчета в Системах (Simulink).

Основные шаги расчета драйвера, DUT и подсистем монитора должны быть равными. Их порты могут быть многоскоростными, но наибольший общий делитель (GCD) или основной шаг расчета должны быть тем же самым.

Шаг расчета последовательности и подсистем табло должен быть больше или быть равен основному шагу расчета драйвера, DUT и монитора.