Тиристор с помощью NPN и транзисторов PnP

Simscape / Электрический / Semiconductors & Converters

Блок Thyristor обеспечивает два способа смоделировать тиристор:

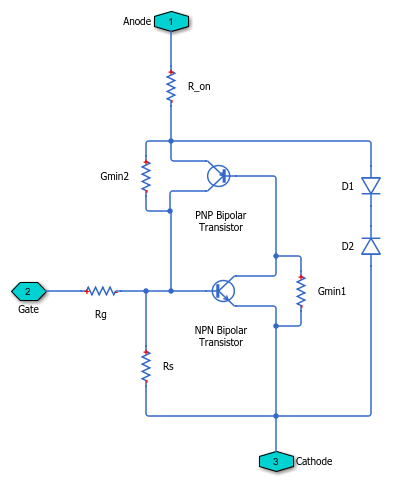

Как эквивалентная схема на основе NPN и биполярные транзисторы PnP

Приближением интерполяционной таблицы к I-V на состоянии (текущее напряжение) кривая

Эквивалентная схема содержит пару NPN и биполярных транзисторов PnP, как показано на следующем рисунке.

P N P N структура тиристора является соответствующим PnP и структурами N-P-N биполярных транзисторов, основой каждого устройства, соединенного к коллектору другого устройства. Чтобы гарантировать, что эта схема ведет себя как тиристор, необходимо выбрать подходящие значения параметров NPN и устройств PnP плюс внешние резисторы. Например, для схемы, чтобы фиксироваться в на состоянии, когда-то инициированный подходящим током затвора, общий доход этих двух транзисторов должен быть больше того. Эта структура модели реплицирует поведение тиристора в схемах типового приложения, одновременно представляя минимальное количество уравнений к решателю, чтобы улучшить скорость симуляции.

Примечание

Чрезвычайно важно, чтобы вы параметрировали тиристорный компонент правильно перед использованием его в вашей модели. Чтобы помочь вам сделать это, существует две тестовых обвязки в примерах Simscape™ Electrical™, Тиристорной Статической Валидации Поведения и Тиристорной Динамической Валидации Поведения. Следуйте тексту справки для этих двух примеров, плюс таблица данных для вашего устройства, чтобы повторно параметрировать тиристорный компонент так, чтобы это реплицировало необходимое поведение. Можно затем скопировать параметрированный компонент в модель. Всего хорошего, чтобы смоделировать схему диска логического элемента правильно, включая серийное сопротивление схемы. Соединение управляемого источника напряжения непосредственно к тиристорному логическому элементу дает нефизические результаты, потому что это фиксирует логический элемент к напряжению катода, когда спрос на логический элемент является нулем.

Модель получает следующие тиристорные поведения:

Токи состояния Off, IDRM и IRRM. Они обычно заключаются в кавычки для максимальных напряжений несостояния VDRM и VRRM. Это принято, как имеет место для большинства тиристоров, что IDRM = IRRM и VDRM = VRRM.

Триггерное напряжение логического элемента равно значению параметров Corresponding gate voltage, V_GT, когда ток затвора равен значению параметров Gate trigger current, I_GT.

Тиристор фиксируется на том, когда ток затвора равен Gate trigger current, I_GT. Тиристор не фиксируется на том, пока ток затвора не достигает этого значения. Чтобы убедиться дело обстоит так, необходимо установить параметр Internal shunt resistor, Rs правильно. Если сопротивление слишком высоко, то логический элемент инициировал, прежде чем ток затвора достигает iGT. Если сопротивление слишком мало, то логический элемент не инициировал.

Можно определить значение внутреннего RS резистора шунта путем выполнения симуляции. Чтобы видеть, как это может быть сделано, обратитесь к Тиристорному Статическому примеру Валидации Поведения. В качестве альтернативы, если вы используете тиристор в схеме, где существует внешний резистор RGK, соединенный от логического элемента до катода, затем эффект RS обычно очень мал, и это может быть установлено в inf.

С тиристором в на состоянии, если ток затвора удален, тиристор остается в на состоянии, при условии, что текущая загрузка выше, чем текущее содержание. Вы не задаете содержание, текущее непосредственно, потому что его значение, в основном, определяется другими параметрами блоков.

Однако текущее содержание может быть под влиянием параметра Product of NPN and PNP forward current gains на вкладке Advanced. Сокращение усиления увеличивает текущее содержание.

Напряжение на состоянии равно значению параметров On-state voltage, V_T, когда текущая загрузка равна значению параметров On-state current, I_T. Это обеспечено значением сопротивления R_on, которое учитывает падение напряжения, замеченное через устройства NPN и PnP.

Инициирование уровнем повышения напряжения несостояния. Быстрое изменение в напряжении анодного катода вызывает ток в условиях основной емкости коллектора. Если этот ток является достаточно большим, он инициировал тиристор в на состоянии. Тиристорная стандартная программа инициализации вычисляет подходящее значение для основной емкости коллектора, так, чтобы, когда скорость изменения напряжения равна значению параметров Critical rate of rise of off-state voltage, dV/dt, тиристор включил. Это вычисление основано на приближении, что необходимым током является vGT / RGK, где RGK является значением сопротивления катода логического элемента, используемым при заключении в кавычки критического значения dV/dt.

Ненулевое управляемое логическим элементом время включения, в основном, под влиянием NPN device forward transit time, TF. Вы или задаете этот параметр непосредственно или вычисляете приближенное значение для TF со времени включения.

Ненулевое коммутируемое время выключения, в основном, под влиянием PNP device forward transit time, TF. Можно или задать этот параметр непосредственно или установить его быть равным прямому времени транспортировки для транзистора NPN.

Резисторы Gmin1 и Gmin2 улучшают числовую робастность при больших прямых и противоположных напряжениях. Их значения влияют на токи несостояния на не больше, чем 1% при максимальных прямых и противоположных напряжениях несостояния.

Примечание

Поскольку эта реализация блока включает модель заряда, необходимо смоделировать импеданс схемы, управляющей логическим элементом, чтобы получить представительный поворот - на и выключить динамику. Поэтому, если вы упрощаете управляющую схему логического элемента путем представления его как управляемого источника напряжения, необходимо включать подходящий последовательный резистор между источником напряжения и логическим элементом.

При использовании представления интерполяционной таблицы вы вводите сведенные в таблицу значения для анодного катодного тока как функция напряжения анодного катода когда в на состоянии. Основными преимуществами использования этой опции является скорость симуляции и простота параметризации. Чтобы далее упростить базовую модель, это представление не моделирует:

Устройство, инициировавшее из-за уровня повышения напряжения несостояния

Коммутируемое время выключения

Задержка при включении представлена входным конденсатором катода логического элемента, значение которого вычисляется так, чтобы задержка между повышением напряжения затвора и устройством, начинающим включать, была равна значению, заданному параметром Turn-on delay time. Поворот - на времени нарастания для текущей загрузки реализован путем сползания нелинейно между нулем и током, определенным профилем текущего напряжения на состоянии по периоду времени, заданному значением параметра Turn-on rise time. Обратите внимание на то, что получившийся поворот - на текущем профиле является приближением к существующему устройству.

Блок имеет дополнительный тепловой порт, скрытый по умолчанию. Чтобы осушить тепловой порт, щелкните правой кнопкой по блоку по своей модели, и затем из контекстного меню выбирают Simscape> Block choices> Show thermal port. Это действие отображает тепловой порт H на значке блока и отсоединяет параметры Thermal Port.

Используйте тепловой порт, чтобы симулировать эффекты выработанного тепла и температуры устройства. Для получения дополнительной информации об использовании тепловых портов и на параметрах Thermal Port, смотрите Термальные эффекты Симуляции в Полупроводниках.

Этот блок не моделирует температурно-зависимые эффекты. Этот блок симулирован при температуре, заданной значением параметров Measurement temperature. Все параметры должны быть заключены в кавычки для этой температуры.

Если вы используете представление эквивалентной схемы:

В чувствительных вентильных схемах (то есть, где нет никакого внешнего резистора катода логического элемента RGK), необходимо установить значение параметра Internal shunt resistor, Rs, чтобы гарантировать правильное инициирование. Если внутреннее сопротивление шунта слишком высоко, то тиристорные триггеры для токов меньше, чем iGT. Если внутреннее сопротивление шунта является слишком низким, тиристор не инициировал для входа, текущего из iGT. Для получения дополнительной информации при использовании симуляции, чтобы определить приемлемое внутреннее значение сопротивления шунта, смотрите Тиристорный Статический пример Валидации Поведения.

Инициирование путем превышения напряжения переключения не моделируется.

Численно тиристор может быть требовательным, чтобы симулировать, учитывая очень небольшие токи затвора по сравнению с текущей загрузкой, и также очень крутые текущие градиенты во время переключения. Однако для большинства типичных основанных на тиристоре схем, можно использовать параметры симуляции по умолчанию. В некоторых случаях вы, возможно, должны сжать Absolute Tolerance и параметры Relative Tolerance на вкладке Solver диалогового окна Configuration Parameters, гарантировать сходимость. В таких случаях, изменяя значение по умолчанию Absolute Tolerance от auto к 1e-4 или 1e-5 обычно достаточно, потому что это предотвращает адаптивное изменение этого параметра в процессе моделирования.

Токи утечки аппроксимированы диодами D1 и D2, как показано в эквивалентной схеме. Этот подход принимает, что утечка через эти два транзистора мала в сравнении. Это предположение не допустимо для значений vGT, которые значительно меньше, чем типичное прямое падение напряжения 0,6 В.

Если вы используете представление интерполяционной таблицы:

Инициирование путем превышения напряжения переключения или скоростью изменения напряжения несостояния не моделируется.

Коммутируемое время выключения не моделируется. Проверяйте, что ваша схема не нарушает установленное коммутируемое время выключения для тиристора.

Когда вы задаете поворот - на времени нарастания, получившийся профиль текущего времени является приближением.

[1] Г. Массобрио и П. Антоньетти. Полупроводниковое моделирование устройства с SPICE. 2-й выпуск, McGraw-Hill, 1993.

NPN Bipolar Transistor | PNP Bipolar Transistor | Thyristor (Piecewise Linear)