Подсистема, выполнение которой включено внешним входом

Simulink / Ports & Subsystems

HDL Coder / Ports & Subsystems

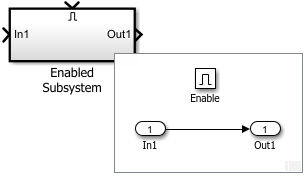

Блок Enabled Subsystem является блоком Subsystem, предварительно сконфигурированным как начальная точка для создания подсистемы, которая выполняется, когда управляющий сигнал имеет положительное значение.

Используйте блоки Enabled Subsystem для модели:

Разрывы

Дополнительная функциональность

Альтернативная функциональность

In — Вход сигнала с блоком подсистемыРазмещение блока Inport в блоке подсистемы добавляет внешний входной порт в блок. Метка порта совпадает с именем блока Inport.

Используйте блоки Inport, чтобы получить сигналы от окружения.

Типы данных: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus

Enable — Вход управляющего сигнала с блоком подсистемыРазмещение блока Enable в блоке подсистемы добавляет внешний входной порт в блок и изменяет блок в блок Enable Subsystem.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

Out — Выход сигнала от подсистемыРазмещение блока Outport в блоке подсистемы добавляет выходной порт из блока. Метка порта на блоке подсистемы является именем блока Outport.

Используйте блоки Outport , чтобы отправить сигналы в окружение.

Типы данных: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus

Фактическая поддержка генерации кода зависит от реализации блока.

HDL Coder™ обеспечивает дополнительные параметры конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

При использовании активированных подсистем в моделях, предназначенных для генерации HDL-кода, это - хорошая практика, чтобы рассмотреть следующее:

Для результатов синтеза совпадать с результатами Simulink®, порт Enable должен управляться зарегистрированной логикой (с синхронными часами) на FPGA.

Поместите единичные задержки на Enabled выходные сигналы Подсистемы. Выполнение так препятствует тому, чтобы генератор кода вставил дополнительные обходные регистры в HDL-код.

Enabled подсистемы могут влиять на результаты синтеза следующими способами:

В некоторых случаях скорость системных часов может понизиться небольшим процентом.

Сгенерированный код использует больше ресурсов, масштабирующихся с количеством активированных экземпляров подсистемы и количеством выходных портов на подсистему.

| Архитектура | Описание |

|---|---|

Module (значение по умолчанию) | Сгенерируйте код для подсистемы и блоков в подсистеме. |

BlackBox | Сгенерируйте интерфейс черного квадрата. Сгенерированный HDL-код включает только определения порта ввода/вывода для подсистемы. Поэтому можно использовать подсистему в модели, чтобы сгенерировать интерфейс к существующему, вручную записанному HDL-коду. Генерация интерфейса черного ящика для подсистем похожа на генерацию интерфейса блока Model без сигналов часов. |

| Удалите подсистему из сгенерированного кода. Можно использовать подсистему в симуляции, однако, обработать его как "нет" в HDL-коде. |

| Общий | |

|---|---|

| AdaptivePipelining | Автоматическая конвейерная вставка на основе инструмента синтеза, предназначайтесь для частоты и размеров слова множителя. Значением по умолчанию является |

| BalanceDelays | Обнаруживает введение новых задержек вдоль одного пути и вставляет соответствие с задержками на других путях. Значением по умолчанию является |

| ClockRatePipelining | Вставьте конвейерные регистры на более быстрой тактовой частоте вместо более медленной скорости передачи данных. Значением по умолчанию является |

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| DistributedPipelining | Конвейерно обработайте распределение регистра или повторную синхронизацию регистра. Значением по умолчанию является |

| DSPStyle | Синтез приписывает для отображения множителя. Значением по умолчанию является |

| FlattenHierarchy | Удалите иерархию подсистемы из сгенерированного HDL-кода. Значением по умолчанию является |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| SharingFactor | Количество функционально эквивалентных ресурсов, чтобы сопоставить с одним совместно используемым ресурсом. Значением по умолчанию является 0. См. также Разделение ресурсов (HDL Coder). |

| StreamingFactor | Количество параллельных информационных каналов или векторы, которые являются временем, мультиплексированным, чтобы преобразовать в последовательные, скалярные информационные каналы. Значение по умолчанию 0, который реализует полностью параллельные информационные каналы. См. также Передающий потоком (HDL Coder). |

Целевая спецификация

Этот блок не может быть DUT, таким образом, настройки свойства блока во вкладке Target Specification проигнорированы.

HDL Coder поддерживает генерацию HDL-кода для активированных подсистем, которые отвечают следующим условиям:

Активированная подсистема не является DUT.

Подсистема и не инициирована и включена.

Разрешать сигнал является скаляром.

Выходные параметры активированной подсистемы имеют начальное значение 0.

Все вводы и выводы активированной подсистемы (включая разрешать сигнал) запускаются на том же уровне.

Параметр Show output port блока Enable устанавливается на Off.

Параметр States when enabling блока Enable устанавливается на held т.е. . блок Enable не сбрасывает состояния, когда включено).

Параметр Output when disabled для активированных выходных портов подсистемы устанавливается на held т.е. . активированная подсистема не сбрасывает выходные значения, когда отключено).

Если DUT содержит следующие блоки, RAMArchitecture установлен в WithClockEnable:

Dual Port RAM

Simple Dual Port RAM

Single Port RAM

Активированная подсистема не содержит следующие блоки:

CIC Decimation

CIC Interpolation

FIR Decimation

FIR Interpolation

Downsample

Upsample

HDL FIFO

Блоки HDL Cosimulation (HDL Verifier™)

Переход уровня

NR Polar Encoder и NR Polar Decoder (Wireless HDL Toolbox™)

Автоматический пример Контроллера Усиления показывает, как можно использовать включенные подсистемы в генерации HDL-кода. Открыть пример, введите:

hdlcoder_agc

Фактическая поддержка типов данных зависит от реализации блока.

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.